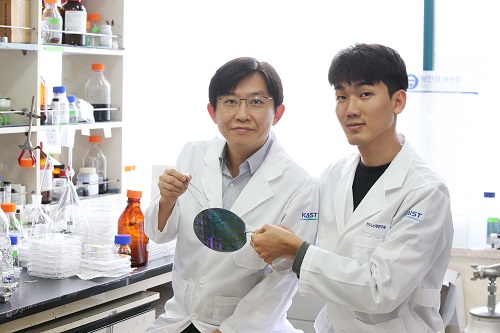

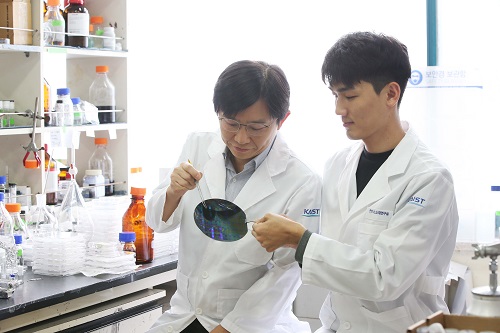

〈 김상욱 교수, 진형민 연구원 〉

우리 대학 신소재공학과 김상욱 교수 연구팀이 카메라의 플래시를 이용해 반도체를 제작하는 기술을 개발했다.

이 기술은 반도체용 7나노미터 패턴 기법으로 한 번의 플래시를 조사하는 것만으로 대면적에서 초미세 패턴을 제작할 수 있다. 향후 고효율, 고집적 반도체 소자 제작 등에 활용 가능할 것으로 기대된다.

진형민 연구원, 박대용 박사과정이 공동 1저자로 참여한 이번 연구 결과는 국제 학술지 ‘어드밴스드 머티리얼즈(Advanced Materials)’ 8월 21일자 온라인 판에 게재됐다.

4차 산업혁명의 주요 요소인 인공지능, 사물인터넷, 빅데이터 등의 기술에는 고용량, 고성능 반도체 소자가 핵심적으로 필요하다. 이러한 차세대 고집적 반도체 소자를 만들기 위해서는 패턴을 매우 작게 형성하는 리소그래피(Lithography) 기술의 개발이 필수적이다.

현재 관련 업계에서는 작은 패턴 제작에 주로 광 리소그래피(Photolithograph) 기술을 이용하고 있다. 하지만 이 기술은 10나노미터 이하의 패턴을 형성하기엔 한계가 있다.

고분자를 이용한 분자조립 패턴 기술은 공정비용이 저렴하고 10나노미터 이하 패턴 형성이 가능해 광 리소그래피를 대신할 차세대 기술로 각광받고 있다. 그러나 고온 열처리나 유독성 증기 처리에 시간이 많이 소요되기 때문에 대량 생산이 어려워 상용화에 한계가 있다.

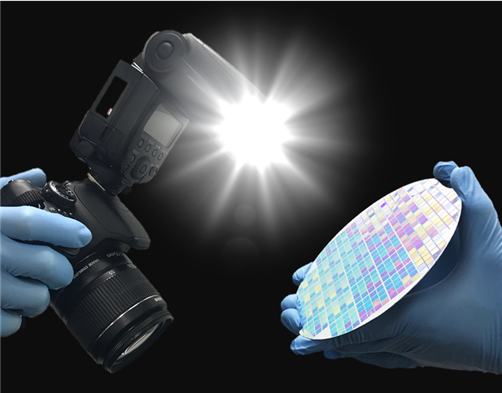

연구팀은 고분자 분자조립 패턴 기술의 문제 해결을 위해 순간적으로 강한 빛을 내는 카메라 플래시를 활용했다. 플래시 빛을 이용하면 15 밀리 초(1밀리 초 : 천분의 1초) 내에 7나노미터의 반도체 패턴을 구현할 수 있고, 대면적에서 수십 밀리 초의 짧은 시간 내에 수 백도의 고온을 낼 수 있다.

연구팀은 이 기술을 고분자 분자 조립에 응용해 단 한 번의 플래시를 조사하는 것으로 분자 조립 패턴을 형성할 수 있음을 증명했다.

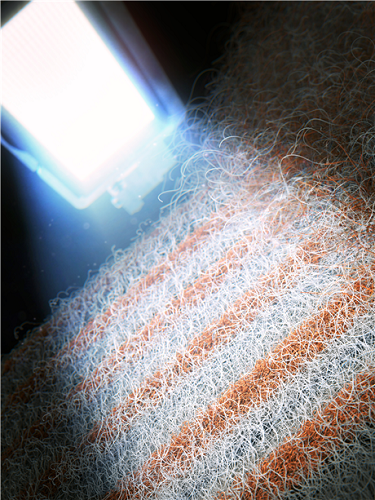

또한 연구팀은 고온 열처리 공정이 불가능한 고분자 유연 기판에도 적용이 가능함을 확인했다. 이를 통해 차세대 유연 반도체 제작에 응용할 수 있을 것으로 보인다.

연구팀은 카메라 플래시 광열 공정을 분자 조립 기술에 도입해 분자 조립 반도체기술의 실현을 앞당길 수 있는 고효율의 기술이라고 밝혔다.

연구를 주도한 김상욱 교수는 “분자조립 반도체 기술은 그 잠재성에도 불구하고 공정효율 제고가 큰 숙제로 남아 있었다”며 “이번 기술은 분자조립기반 반도체의 실용화에 획기적 해결책이 될 것이다”고 말했다.

신소재공학과 이건재 교수, 부산대학교 재료공학과 김광호 교수와의 공동으로 진행된 이번 연구는 과학기술정보통신부 리더연구자지원사업인 다차원 나노조립제어 창의연구단과 글로벌프론티어사업의 지원을 받아 수행됐다.

□ 사진 설명

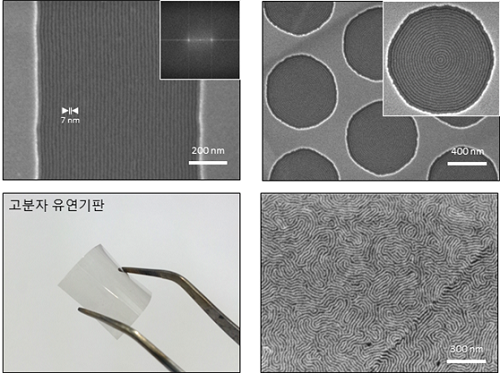

사진1. 플래시 광을 이용한 반도체 패턴 형성

사진2. 플래시 광을 이용한 분자조립 패턴 형성 모식도

사진3. 다양한 가이드 패턴을 이용한 자기조립 패턴 제어와 고분자 유연기판에서의 플래시 자기조립 패턴 형성

-

연구 미래 반도체 소재 나노 분석 정확도 획기적 향상

머리카락 두께의 수만 분의 1도 관찰할 수 있는 초정밀 현미경으로 특수 전자소자를 측정할 때 발생하던 오차의 원인이 밝혀졌다. 한미 공동 연구진이 그동안 측정 대상 물질의 특성으로 여겨졌던 오차가, 실제로는 현미경 탐침 끝부분과 물질 표면 사이의 극미세 공간 때문이라는 사실을 밝혀낸 것이다. 이번 연구는 반도체, 메모리 소자, 센서 등에 활용되는 나노 소재 특성을 정확하게 분석하여 관련 기술 발전에 크게 기여할 것이다. 우리 대학 신소재공학과 홍승범 교수 연구팀이 미국 버클리 대학 레인 마틴(Lane W. Martin) 교수팀과의 국제 공동연구를 통해, 주사탐침현미경 측정의 최대 난제였던 신호 정확도를 저해하는 핵심 요인을 규명하고 이를 제어하는 획기적인 방법을 개발했다고 18일 밝혔다. 연구팀은 현미경 탐침과 시료 표면 사이에 존재하는 비접촉 유전 간극이 측정 오차의 주요 원인임을 밝혀냈다. 이 간극은 측정환경에서 쉽게 변조되거나 오염물질로 채워져 있어 전기적 측정에

2024-11-18 -

행사 제1회 한국인공지능시스템포럼(이하 KAISF) 조찬 강연회 개최

우리 대학이 12일(화) 오전 대전 인터시티호텔에서 ‘제1회 한국인공지능시스템포럼(이하 KAISF) 조찬 강연회’를 개최했다. 이는 우리 대학 인공지능반도체대학원이 AI 기술에 관련 미래와 혁신 등에 대해 다양한 분야의 전문가들이 함께 논의하는 장을 열고자 추진됐다. 총 77명의 전문가가 참석한 이번 행사에는 이광형 총장, 홍진배 정보통신기획평가원장, 방승찬 한국전자통신연구원장 등이 축사를 전했다. 이어서 ▲칩렛 이종 집적 첨단 패키지 기반 페타플롭스급 고성능 PIM 설계(한진호 한국전자통신연구원 PIM인공지능반도체연구실장) ▲자율주행·자율 행동체 연구개발사업 소개(최정단 한국전자통신연구원 모빌리티로봇연구본부장)에 대해 발표했다. 이후 인공지능 반도체 설계 전문 기업인 리벨리온(Rebellions)의 박성현 대표가 ‘인공지능 반도체와 리벨리온의 여정’을 주제로 강연을 진행했다. 박성현 리벨리온 대표는 강연에서 &ldq

2024-11-12 -

행사 KAIST-삼성전자, 시스템 반도체 칩 추가 지원 협약 체결

우리 대학이 삼성전자와 ‘130nm BCDMOS 공정 지원' 협약을 23일 오후 체결한다. 삼성전자가 반도체 설계 전문 인재 양성을 위해 지원하는 BCDMOS(복합고전압소자: Bipolar-CMOS-DMOS)*는 고전압과 고속 동작이 필요한 전력 관리 응용 분야에 적합한 공정이다. 이번 협약을 바탕으로 130nm(나노미터) BCDMOS 8인치 공정을 올해 하반기부터 도입해 국내 반도체 전공 석·박사 과정 학생에게 칩 제작 기회를 제공한다. 이를 위해, 우리 대학 반도체설계교육센터(소장 박인철, IC Design Education Center 이하 IDEC)는 130nm BCDMOS 공정을 위한 설계 전자설계자동화툴(EDA Tool)과 기술 지원 환경을 마련했다. IDEC은 삼성전자와 협력해 2021년부터 28nm 로직** 공정 칩 제작 기회를 학생들에게 제공하고 있으며, 지난해 28nm FD-SOI***공정 지원도 추가했다. 올해 제공된

2024-07-24 -

행사 “AI 반도체 미래가 밝다” KAIST PIM반도체설계연구센터, AI반도체 전문인력 양성 교육

과학기술정보통신부·정보통신기획평가원이 주관하는 PIM인공지능반도체 핵심기술개발사업의 지원을 받고있는 우리 대학 PIM반도체설계연구센터가 AI 반도체 전문인력 양성을 위해 전국 AI 및 반도체 관련 학과 학부생과 대학원생을 대상으로 SK하이닉스와 삼성전자의 PIM* 기반 이론 및 실습 교육을 진행했다. 강의는 6월 20일(목)부터 6월 21일(금)까지 SK하이닉스 교육, 7월 4일(목)부터 7월 5일(금)까지 삼성전자 교육을 각각 KAIST PIM반도체설계연구센터에서 진행했다. *PIM(Processing-In-Memory): 메모리 반도체에 연산 기능을 추가하여 AI와 빅데이터 처리 분야에서 데이터 처리 속도를 높이면서도 사용 전력을 줄이는 반도체 설계 기술 이번 교육은 SK하이닉스의 AiM*과 삼성전자의 HBM-PIM*을 활용하여 수강생들이 직접 실습할 수 있는 기회를 제공했다. 전국 25개 대학교에서 300명이 넘는 학생들이 접수하여 높은 관심을 받았다

2024-07-11 -

인물 김이섭 교수 연구실 박준영 석사졸업생, 국제 반도체 설계 자동화 학회 최우수논문상 수상

우리 대학 전기및전자공학부 김이섭 교수 연구실의 박준영 석사졸업생이 6월 23일 ~ 6월 27일, 미국 샌프란시스코에서 개최된 국제 반도체 설계 자동화 학회 (Design Automation Conference, 이하 DAC) 에서 최우수 논문상(Best Paper Award)을 수상하는 성과를 거두었다. DAC은 1964년에 설립돼 올해 61회째를 맞은, 반도체설계자동화, 인공지능 알고리즘과 칩 설계 등을 포함하는 국제학술대회로서, 제출된 논문 중 상위 20퍼센트 정도만 선정하는, 관련 분야 최고 권위의 학회이다. 수상한 연구는 우리 대학 전기및전자공학부 졸업생 박준영 씨의 석사과정 졸업 논문에 기반한 것으로서, Large Language Model 모델 추론의 문제점이 되는 KV 캐싱의 메모리 전송을 줄이는 알고리즘 근사 기법과 하드웨어 아키텍처를 제안하였으며, 학회 best paper award 선정 위원회로부터 그 우수성을 인정받아 발표논문 337편 중 (제출논문

2024-07-02