%EB%82%B8%EB%93%9C%ED%94%8C%EB%9E%98%EC%8B%9C

-

낸드플래시 방식의 고신뢰성 인공 시냅스 소자 개발

우리 대학 신소재공학과 김경민 교수 연구팀이 낸드플래시(NAND Flash)의 전하 저장 방식을 활용하여 양산성이 높으며 높은 균일도를 갖는 고신뢰성 인공 시냅스 소자 개발에 성공했다고 6일 밝혔다.

최근 고성능의 인공지능 기술(Artificial Intelligence; AI) 구현을 위하여 인공 시냅스 소자를 통해 크로스바 어레이 구조에서 고밀도의 메모리 집적과 행렬 연산 가속을 동시에 구현하는 맞춤형 하드웨어를 개발하기 위한 노력이 계속되고 있다.

시냅스 소자의 후보 물질로 다양한 물질이 제시되었으나, 인공지능 가속기가 요구하는 다비트성 (Multi-bit), 보존성 (retention), 균일성 (uniformity), 내구성(Endurance) 등을 모두 만족하는 소자는 매우 드물었으며, 또한 제시되는 후보 물질들의 동작 방식도 기존 반도체 소자들과 매우 달라 반도체 소자로 활용함에 있어 양산성 및 수율 등에도 추가적인 검증이 필요하다는 한계가 있었다.

김경민 교수 연구팀은 낸드플래시의 전하 저장하는 방식을 차용한 2단자 구조의 인공 시냅스 소자를 개발했다. 기존에는 2단자 시냅스 구조가 안정적으로 동작하기 위해서는 전하의 저장 상태를 읽기 위해 산화막을 얇게 하여 저장된 전하의 보존성을 희생해야하는 한계가 있었다. 연구팀은 이번 연구에서 알루미늄 산화막, 나이오븀 산화막, 탄탈룸 산화막 등이 순차적으로 적층된 최적의 시냅스 소자 구조를 제안하였으며, 이를 통해 안정적인 다비트성과 보존성을 모두 확보하였다.

또한, 제안한 시냅스 소자가 갖는 자가정류(self-rectifying) 특성을 활용하는 병렬 컴퓨팅 방법을 제시하여 기존의 순차적 컴퓨팅 대비 필요한 에너지를 약 71% 절약할 수 있었다.

공동 제1 저자인 신소재공학과 김근영 석박통합과정은 “이번 연구는 이미 검증된 낸드플래시 메모리 구조를 인공 시냅스 소자에 적용하여 시냅스 소자의 양산성에 대한 우려를 불식한데 의미가 있다”며 “이처럼 향후 개발되는 인공지능 반도체에도 기존 반도체 소자의 고성능 특성과 물질의 새로운 특성을 접목하는 연구가 활발히 이뤄질 것으로 예상된다”고 밝혔다.

이러한 인공 시냅스 소자 기술은 인공지능 컴퓨팅을 저전력으로 구현하는 지능형 반도체 소자에 적용되어 에지 컴퓨팅 (Edge computing)과 같이 적은 에너지 소모가 필수적인 인공지능 기술에 다양하게 적용될 수 있을 것으로 기대된다.

이번 연구는 국제 학술지 ‘어드밴스드 사이언스(Advanced Science)’에 11월 28일 字 온라인 게재됐으며 한국연구재단, KAIST, SK Hynix의 지원을 받아 수행됐다. (논문명: Retention secured nonlinear and self-rectifying analog charge trap memristor for energy-efficient neuromorphic hardware)

2022.12.06 조회수 8027

낸드플래시 방식의 고신뢰성 인공 시냅스 소자 개발

우리 대학 신소재공학과 김경민 교수 연구팀이 낸드플래시(NAND Flash)의 전하 저장 방식을 활용하여 양산성이 높으며 높은 균일도를 갖는 고신뢰성 인공 시냅스 소자 개발에 성공했다고 6일 밝혔다.

최근 고성능의 인공지능 기술(Artificial Intelligence; AI) 구현을 위하여 인공 시냅스 소자를 통해 크로스바 어레이 구조에서 고밀도의 메모리 집적과 행렬 연산 가속을 동시에 구현하는 맞춤형 하드웨어를 개발하기 위한 노력이 계속되고 있다.

시냅스 소자의 후보 물질로 다양한 물질이 제시되었으나, 인공지능 가속기가 요구하는 다비트성 (Multi-bit), 보존성 (retention), 균일성 (uniformity), 내구성(Endurance) 등을 모두 만족하는 소자는 매우 드물었으며, 또한 제시되는 후보 물질들의 동작 방식도 기존 반도체 소자들과 매우 달라 반도체 소자로 활용함에 있어 양산성 및 수율 등에도 추가적인 검증이 필요하다는 한계가 있었다.

김경민 교수 연구팀은 낸드플래시의 전하 저장하는 방식을 차용한 2단자 구조의 인공 시냅스 소자를 개발했다. 기존에는 2단자 시냅스 구조가 안정적으로 동작하기 위해서는 전하의 저장 상태를 읽기 위해 산화막을 얇게 하여 저장된 전하의 보존성을 희생해야하는 한계가 있었다. 연구팀은 이번 연구에서 알루미늄 산화막, 나이오븀 산화막, 탄탈룸 산화막 등이 순차적으로 적층된 최적의 시냅스 소자 구조를 제안하였으며, 이를 통해 안정적인 다비트성과 보존성을 모두 확보하였다.

또한, 제안한 시냅스 소자가 갖는 자가정류(self-rectifying) 특성을 활용하는 병렬 컴퓨팅 방법을 제시하여 기존의 순차적 컴퓨팅 대비 필요한 에너지를 약 71% 절약할 수 있었다.

공동 제1 저자인 신소재공학과 김근영 석박통합과정은 “이번 연구는 이미 검증된 낸드플래시 메모리 구조를 인공 시냅스 소자에 적용하여 시냅스 소자의 양산성에 대한 우려를 불식한데 의미가 있다”며 “이처럼 향후 개발되는 인공지능 반도체에도 기존 반도체 소자의 고성능 특성과 물질의 새로운 특성을 접목하는 연구가 활발히 이뤄질 것으로 예상된다”고 밝혔다.

이러한 인공 시냅스 소자 기술은 인공지능 컴퓨팅을 저전력으로 구현하는 지능형 반도체 소자에 적용되어 에지 컴퓨팅 (Edge computing)과 같이 적은 에너지 소모가 필수적인 인공지능 기술에 다양하게 적용될 수 있을 것으로 기대된다.

이번 연구는 국제 학술지 ‘어드밴스드 사이언스(Advanced Science)’에 11월 28일 字 온라인 게재됐으며 한국연구재단, KAIST, SK Hynix의 지원을 받아 수행됐다. (논문명: Retention secured nonlinear and self-rectifying analog charge trap memristor for energy-efficient neuromorphic hardware)

2022.12.06 조회수 8027 -

반도체 다층 소자의 개별 층 두께를 옹스트롬 정확도로 비파괴 검사하는 기술 개발

우리 대학 기계공학과 김정원 교수 연구팀이 삼차원 낸드플래시 메모리(이하 3D-NAND)의 비파괴적인 검사를 위해 광학 측정법과 머신러닝을 사용한 다층 두께 측정기술을 개발했다. 이 기술은 200층 이상의 초고밀도 3D-NAND 소자 공정 과정에서 전수검사 방법으로 사용돼 공정의 효율을 극대화할 수 있을 것으로 기대된다.

3D-NAND 메모리는 수백층의 메모리 셀이 적층되어 있는 메모리 반도체로, 기존의 평면형 플래시 메모리와 비교하여 저장용량과 에너지 효율이 매우 우수하여 개인용 USB부터 서버 시스템까지 다양하게 사용되고 있다.

기존에는 수직으로 적층된 반도체 셀들의 두께를 측정하기 위하여 전자현미경을 사용하였다. 하지만 전자현미경을 사용한 방법은 샘플의 단면을 이미징하기 위하여 샘플을 절단해야 하고 비용도 많이 들기 때문에, 전수검사로서는 적합하지 않은 문제가 있었다.

연구팀은 반도체 다층 구조가 초고속 광학 시스템에 자주 사용되는 유전체 거울의 구조와 유사하다는 점에 착안하여, 유전체 거울의 분석에 활용되는 광학 스펙트럼 측정법을 반도체 다층 구조에도 적용했다.

연구팀은 엘립소미터(ellipsometer)와 스펙트로포토미터(spectrophotometer)를 이용한 반도체 다층 샘플의 스펙트럼 측정과 머신러닝 알고리즘을 활용하여 200층이 넘는 반도체 물질의 각 층 두께를 1.6 옹스트롬 (1Å = 1미터의 100억 분의 1)의 평균제곱근오차로 예측할 수 있는 방법을 개발했다. 이 기술은 삼차원 반도체 소자의 검수 공정, 적층 공정, 그리고 식각 공정의 정확도를 크게 향상시킬 수 있을 것으로 기대된다.

연구팀은 또한 시뮬레이션 스펙트럼 데이터를 생성해 개별 층의 두께 불량을 검출할 수 있는 머신러닝 학습법도 개발했다. 그 결과 반도체 물질 적층 시 목표로 설정한 두께보다 약 50Å만큼 얇게 제작된 샘플들을 정상 범주의 샘플들로부터 성공적으로 분리할 수 있었다. 연구팀이 개발한 불량샘플 검출법은 시뮬레이션 데이터를 활용하기 때문에 큰 비용이 들지 않으며, 공정의 초기에 발견될 수 있는 불량 샘플들을 효과적으로 검출할 수 있을 것으로 기대된다.

최근 글로벌 IT 기업들의 서버 시스템에 대한 수요가 늘어나고 높은 저장용량을 가진 스마트 기기들이 개발됨에 따라, 초고밀도, 초고효율을 갖는 3D-NAND 메모리가 반도체 시장에서 각광받고 있다. 이번 연구 결과는 다양한 삼차원 반도체 소자들의 비파괴적인 검수를 위해 활용될 수 있다.

김 교수는 “비파괴적인 광학 측정법과 머신러닝을 결합한 방법은 다양한 반도체 검수 공정에도 적용할 수 있다”고 밝히며, “다양한 반도체 소자들의 형상이나 공정 조건 모니터링에도 광학측정법과 머신러닝을 결합한 접근방식을 활용할 것”이라고 말했다.

기계공학과 곽현수 박사과정 학생이 제1저자로 참여하고 삼성전자 메모리 계측기술팀과의 산학협력연구로 수행된 이번 연구는 국제학술지 ‘라이트: 어드밴스드 매뉴팩처링(Light: Advanced Manufacturing)’ 창간호에 1월 12일 게재됐다. (논문명: Non-destructive thickness characterisation of 3D multilayer semiconductor devices using optical spectral measurements and machine learning)

이번 연구는 삼성전자 산학연구과제의 지원을 받아 수행됐다.

2021.01.13 조회수 67550

반도체 다층 소자의 개별 층 두께를 옹스트롬 정확도로 비파괴 검사하는 기술 개발

우리 대학 기계공학과 김정원 교수 연구팀이 삼차원 낸드플래시 메모리(이하 3D-NAND)의 비파괴적인 검사를 위해 광학 측정법과 머신러닝을 사용한 다층 두께 측정기술을 개발했다. 이 기술은 200층 이상의 초고밀도 3D-NAND 소자 공정 과정에서 전수검사 방법으로 사용돼 공정의 효율을 극대화할 수 있을 것으로 기대된다.

3D-NAND 메모리는 수백층의 메모리 셀이 적층되어 있는 메모리 반도체로, 기존의 평면형 플래시 메모리와 비교하여 저장용량과 에너지 효율이 매우 우수하여 개인용 USB부터 서버 시스템까지 다양하게 사용되고 있다.

기존에는 수직으로 적층된 반도체 셀들의 두께를 측정하기 위하여 전자현미경을 사용하였다. 하지만 전자현미경을 사용한 방법은 샘플의 단면을 이미징하기 위하여 샘플을 절단해야 하고 비용도 많이 들기 때문에, 전수검사로서는 적합하지 않은 문제가 있었다.

연구팀은 반도체 다층 구조가 초고속 광학 시스템에 자주 사용되는 유전체 거울의 구조와 유사하다는 점에 착안하여, 유전체 거울의 분석에 활용되는 광학 스펙트럼 측정법을 반도체 다층 구조에도 적용했다.

연구팀은 엘립소미터(ellipsometer)와 스펙트로포토미터(spectrophotometer)를 이용한 반도체 다층 샘플의 스펙트럼 측정과 머신러닝 알고리즘을 활용하여 200층이 넘는 반도체 물질의 각 층 두께를 1.6 옹스트롬 (1Å = 1미터의 100억 분의 1)의 평균제곱근오차로 예측할 수 있는 방법을 개발했다. 이 기술은 삼차원 반도체 소자의 검수 공정, 적층 공정, 그리고 식각 공정의 정확도를 크게 향상시킬 수 있을 것으로 기대된다.

연구팀은 또한 시뮬레이션 스펙트럼 데이터를 생성해 개별 층의 두께 불량을 검출할 수 있는 머신러닝 학습법도 개발했다. 그 결과 반도체 물질 적층 시 목표로 설정한 두께보다 약 50Å만큼 얇게 제작된 샘플들을 정상 범주의 샘플들로부터 성공적으로 분리할 수 있었다. 연구팀이 개발한 불량샘플 검출법은 시뮬레이션 데이터를 활용하기 때문에 큰 비용이 들지 않으며, 공정의 초기에 발견될 수 있는 불량 샘플들을 효과적으로 검출할 수 있을 것으로 기대된다.

최근 글로벌 IT 기업들의 서버 시스템에 대한 수요가 늘어나고 높은 저장용량을 가진 스마트 기기들이 개발됨에 따라, 초고밀도, 초고효율을 갖는 3D-NAND 메모리가 반도체 시장에서 각광받고 있다. 이번 연구 결과는 다양한 삼차원 반도체 소자들의 비파괴적인 검수를 위해 활용될 수 있다.

김 교수는 “비파괴적인 광학 측정법과 머신러닝을 결합한 방법은 다양한 반도체 검수 공정에도 적용할 수 있다”고 밝히며, “다양한 반도체 소자들의 형상이나 공정 조건 모니터링에도 광학측정법과 머신러닝을 결합한 접근방식을 활용할 것”이라고 말했다.

기계공학과 곽현수 박사과정 학생이 제1저자로 참여하고 삼성전자 메모리 계측기술팀과의 산학협력연구로 수행된 이번 연구는 국제학술지 ‘라이트: 어드밴스드 매뉴팩처링(Light: Advanced Manufacturing)’ 창간호에 1월 12일 게재됐다. (논문명: Non-destructive thickness characterisation of 3D multilayer semiconductor devices using optical spectral measurements and machine learning)

이번 연구는 삼성전자 산학연구과제의 지원을 받아 수행됐다.

2021.01.13 조회수 67550 -

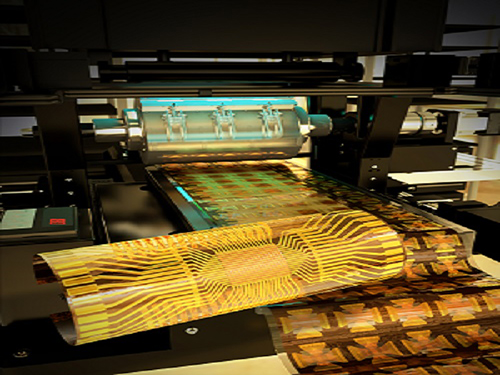

이건재 교수, 유연고집적회로의 연속적패키징 기술 개발

〈 이 건 재 교수 〉

우리 대학 신소재공학과 이건재 교수와 한국기계연구원 김재현 박사 공동 연구팀이 롤 기반 공정을 통해 플렉서블 기기의 핵심기술인 유연 고집적회로를 연속적으로 패키징(소자와 전자기기를 연결하는 전기적 포장) 및 전사(轉寫)할 수 있는 기술을 개발했다.

또한 개발된 롤 기반 전사 및 패키징 기술을 유연 낸드플래시 메모리(전원이 끊겨도 저장된 데이터를 잃어버리지 않는 비휘발성 메모리의 일종)에 적용하는데 성공했다.

이번 연구 결과는 재료과학 분야 학술지인 ‘어드밴스드 머티리얼즈(Advanced Materials)’ 7월 20일자 온라인 판에 게재됐다.

롤 공정(유연기판을 회전하는 롤에 감으며 동시에 공정을 진행하는 방식) 기반의 유연전자 생산기술은 높은 생산효율을 바탕으로 웨어러블 및 플렉서블 기기 상용화에 중요한 역할을 할 것으로 기대되고 있다.

그러나 지금까지는 고집적회로를 롤 공정으로 구현하는 방법 및 주변회로와 상호 연결하는 패키징 기술이 해결되지 않아 실용화에 한계가 있었다.

문제 해결을 위해 연구팀은 기존 반도체 공정을 이용해 실리콘 기판에 낸드 플래시 메모리를 형성한 후 수백 나노미터(10분의 1m) 두께로 얇게 만들었다.

그 후 개발한 롤 기반 전사 및 패키징 기술을 통해 소자를 유연기판에 옮기는 동시에 이방성 전도 필름을 이용해 상호 연결하는 기술을 구현했다.

연구팀의 최종적인 실리콘 기반 유연 낸드플래시 메모리는 반복적인 휘어짐에도 모든 기능이 정상적으로 동작했고 외부와의 상호연결도 매우 안정적으로 유지됐다.

개발된 롤 기반 유연 고집적회로 기술은 유연 어플리케이션 프로세서(AP), 고집적 메모리, 고속 통신소자 등의 양산에 응용 가능할 것으로 기대된다.

이 교수는 “높은 생산성을 지닌 롤 기반 전사 기술을 이용해 단결정 실리콘 박막 고집적회로를 유연한 인쇄회로 기판 위에 패키징하는 생산기술을 확보했다”며 “향후 유연 디스플레이 및 배터리 기술과 함께 휘어지는 컴퓨터 구현의 핵심 생산 기술이 될 것으로 기대된다”고 말했다.

김재현 박사는 “한국기계연구원이 보유한 롤 기반 전사 기술을 이용해 단결정 실리콘 고집적소자를 유연한 폴리머 인쇄회로 기판 상에 손상 없이 전사함과 동시에 소자와 인쇄회로기판이 전기적으로 연결되도록 하는 롤 기반의 생산 공정 기술을 개발하였다”며 “이 기술은 향후 고성능 전자 소자를 유연 기판 위에 형성해 사물인터넷 및 웨어러블용 고성능 전자기기를 제조하는 핵심 생산 기술이 될 것으로 전망한다.”라고 말했다.

이건재 교수는 2013년도에 0.18 씨모스(CMOS) 공정기반으로 컴퓨터의 두뇌에 해당하는 휘어지는 유연 고집적회로를 최초로 구현했다. 특히 반도체분야 최고 권위학회인 국제반도체소자학회(IEDM)에서 초청받아 발표하는 등 세계적인 주목을 받았다.

한국기계연구원 김재현 박사 연구팀은 2009년부터 롤 스탬프를 이용해 박막소자를 옮기는 기술을 연구하고 있다. 관련 롤 전사 장비 기술을 디스플레이 및 반도체 용도의 롤 장비 회사에 기술이전하기도 했다.

이번 연구는 2013년부터 진행된 한국기계연구원의 나노소재 응용 고성능 유연소자기술 기반구축사업의 일환으로 수행됐다. 이건재 교수는 교원창업을 통해 유연한 고집적회로 관련 기술 상용화를 계획 중이다.

□ 그림 설명

그림1. 연속 롤-패키징 공정의 개요 모식도

그림2. 제작된 유연 실리콘 낸드 플래시메모리

2016.09.01 조회수 19359

이건재 교수, 유연고집적회로의 연속적패키징 기술 개발

〈 이 건 재 교수 〉

우리 대학 신소재공학과 이건재 교수와 한국기계연구원 김재현 박사 공동 연구팀이 롤 기반 공정을 통해 플렉서블 기기의 핵심기술인 유연 고집적회로를 연속적으로 패키징(소자와 전자기기를 연결하는 전기적 포장) 및 전사(轉寫)할 수 있는 기술을 개발했다.

또한 개발된 롤 기반 전사 및 패키징 기술을 유연 낸드플래시 메모리(전원이 끊겨도 저장된 데이터를 잃어버리지 않는 비휘발성 메모리의 일종)에 적용하는데 성공했다.

이번 연구 결과는 재료과학 분야 학술지인 ‘어드밴스드 머티리얼즈(Advanced Materials)’ 7월 20일자 온라인 판에 게재됐다.

롤 공정(유연기판을 회전하는 롤에 감으며 동시에 공정을 진행하는 방식) 기반의 유연전자 생산기술은 높은 생산효율을 바탕으로 웨어러블 및 플렉서블 기기 상용화에 중요한 역할을 할 것으로 기대되고 있다.

그러나 지금까지는 고집적회로를 롤 공정으로 구현하는 방법 및 주변회로와 상호 연결하는 패키징 기술이 해결되지 않아 실용화에 한계가 있었다.

문제 해결을 위해 연구팀은 기존 반도체 공정을 이용해 실리콘 기판에 낸드 플래시 메모리를 형성한 후 수백 나노미터(10분의 1m) 두께로 얇게 만들었다.

그 후 개발한 롤 기반 전사 및 패키징 기술을 통해 소자를 유연기판에 옮기는 동시에 이방성 전도 필름을 이용해 상호 연결하는 기술을 구현했다.

연구팀의 최종적인 실리콘 기반 유연 낸드플래시 메모리는 반복적인 휘어짐에도 모든 기능이 정상적으로 동작했고 외부와의 상호연결도 매우 안정적으로 유지됐다.

개발된 롤 기반 유연 고집적회로 기술은 유연 어플리케이션 프로세서(AP), 고집적 메모리, 고속 통신소자 등의 양산에 응용 가능할 것으로 기대된다.

이 교수는 “높은 생산성을 지닌 롤 기반 전사 기술을 이용해 단결정 실리콘 박막 고집적회로를 유연한 인쇄회로 기판 위에 패키징하는 생산기술을 확보했다”며 “향후 유연 디스플레이 및 배터리 기술과 함께 휘어지는 컴퓨터 구현의 핵심 생산 기술이 될 것으로 기대된다”고 말했다.

김재현 박사는 “한국기계연구원이 보유한 롤 기반 전사 기술을 이용해 단결정 실리콘 고집적소자를 유연한 폴리머 인쇄회로 기판 상에 손상 없이 전사함과 동시에 소자와 인쇄회로기판이 전기적으로 연결되도록 하는 롤 기반의 생산 공정 기술을 개발하였다”며 “이 기술은 향후 고성능 전자 소자를 유연 기판 위에 형성해 사물인터넷 및 웨어러블용 고성능 전자기기를 제조하는 핵심 생산 기술이 될 것으로 전망한다.”라고 말했다.

이건재 교수는 2013년도에 0.18 씨모스(CMOS) 공정기반으로 컴퓨터의 두뇌에 해당하는 휘어지는 유연 고집적회로를 최초로 구현했다. 특히 반도체분야 최고 권위학회인 국제반도체소자학회(IEDM)에서 초청받아 발표하는 등 세계적인 주목을 받았다.

한국기계연구원 김재현 박사 연구팀은 2009년부터 롤 스탬프를 이용해 박막소자를 옮기는 기술을 연구하고 있다. 관련 롤 전사 장비 기술을 디스플레이 및 반도체 용도의 롤 장비 회사에 기술이전하기도 했다.

이번 연구는 2013년부터 진행된 한국기계연구원의 나노소재 응용 고성능 유연소자기술 기반구축사업의 일환으로 수행됐다. 이건재 교수는 교원창업을 통해 유연한 고집적회로 관련 기술 상용화를 계획 중이다.

□ 그림 설명

그림1. 연속 롤-패키징 공정의 개요 모식도

그림2. 제작된 유연 실리콘 낸드 플래시메모리

2016.09.01 조회수 19359