%EC%A7%91%EC%A0%81%ED%9A%8C%EB%A1%9C

-

전자장비의 높은 전력 소모 한계를 뛰어넘는 저전력 고성능 다이오드 소자 최초 개발

우리 대학 물리학과 조성재 교수 연구팀이 기존 흔히 쓰이는 쇼트키 다이오드(Schottky diode)가 갖는 열적 거동의 한계를 뛰어넘는 저전력 정류 소자를 세계 최초로 개발하는 데 성공했다고 25일 밝혔다.

조 교수 연구팀은 단층 흑연, 즉, 그래핀(graphene)이 가지는 선형적 분산 관계의 전자 띠 구조 (linear dispersion band structure)를 이용해 열적 거동 한계(thermionic limit)를 극복한 다이오드를 최초로 구현하는 데 성공했다.

다이오드 전극으로 기존 다이오드에서 활용되었던 금속을 사용하는 대신, 그래핀을 활용함으로써 기존 다이오드의 이상지수 (ideality factor)의 한계를 뛰어넘는 초 이상적(super-ideal) 저전력 정류 소자를 개발하는 데 성공할 수 있었다.

물리학과 조성재 교수 연구실의 명규호 박사, 신원길 박사, 성경환 박사과정이 공동 제1 저자로 참여한 이번 연구는 국제 학술지 `네이쳐 커뮤니케이션스 (Nature Communications)' 7월 온라인판에 출판됐다. (논문명 : Dirac-source diode with sub-unity ideality factor).

현대 정보화 기술 발전에 따라 트랜지스터 소형화 및 집적도 증가가 꾸준히 이뤄졌고, 열 전하 방출(thermionic emission)의 물리적 특성에 의해 제한되는 문턱전압이하 스윙(subthreshold swing, SS, 트랜지스터에서 전류를 10배 증가시키는 데 필요한 전압의 값)이 60mV/dec 라는 한계를 뛰어넘는 트랜지스터에 대한 연구가 이뤄져왔다. 다이오드는 믹서, 셀렉터, 스위치, 광센서, 태양광 소자 등 많은 전자 장비에 쓰임에도 불구하고 열 전하 방출에 의한 열적 거동 한계를 뛰어넘는 연구는 이뤄지지 않고 있다.

반도체 물질과 금속이 접합됐을 때 두 물질의 계면에서 형성되는 쇼트키 장벽에 의해 정류 현상이 일어나는 쇼트키 다이오드의 성능은 크게 정류비(rectifying ratio, 온(on) 상태와 오프(off) 상태 전압의 비)와 이상 지수 (ideality factor)로 나눌 수 있다. 쇼트키 다이오드의 이상 지수는 다이오드의 전류를 10배 증가시키는 데 필요한 전압의 값과 연관된 수치이며, 열적 거동 한계로 인해 상온에서의 일반적인 쇼트키 다이오드는 이상 지수 1 이상의 값을 반드시 가지는 것으로 알려져 있다.

연구팀은 이번 연구에서 단층의 이황화 몰리브덴에 일함수가 다른 단층 그래핀과 다층 그래핀의 비대칭적 접촉을 통해 계면 문제를 해결한 쇼트키 다이오드를 구현했다. 단층의 흑연, 즉, 그래핀은 선형적 분산 관계의 전자 띠 구조를 가지고 있는 물질로, 일반적인 금속과는 달리 에너지에 따라 전하 밀도가 급격히 증감하는 성질을 갖고 있다.

이번 연구에서 새롭게 개발한 그래핀 소스를 이용한 디랙 소스(Dirac-source) 다이오드는 넓은 전류 작동범위 (1-10,000배 전류 범위)에서 이상 지수의 값이 1 미만을 갖는 열적 거동의 한계를 극복한 성능을 달성했으며, 다이오드의 온(on) 상태와 오프(off) 상태의 비율인 정류비가 1억(108) 이상으로, 기존에 보고되어왔던 다이오드보다 2-10배 낮은 전압으로도 기존의 다이오드보다 높은 전류의 정류 작동이 가능함을 보였다.

연구팀이 1 미만의 이상 지수를 갖는 고성능 저전력 쇼트키 다이오드를 개발한 것은 세계 최초로서 2차원 물질 기반의 저전력 다이오드 소자가 미래의 저전력 트랜지스터의 개발과 발맞춰 다양한 저전력 집적회로의 구성이 가능해질 수 있음을 의미한다.

물리학과 조성재 교수는 "이번 연구는 세계 최초로 물리적인 열적 거동 한계를 뛰어넘는 저전력, 고성능의 다이오드 소자를 발명한 것으로, 최소한의 전압과 전력으로 태양광 소자나 광검출기와 같은 미래 산업에서의 활용성이 높을 것으로 기대한다ˮ라고 말했다.

한편 이번 연구는 한국연구재단의 지능형 반도체 선도기술 개발사업과 중견연구자지원사업의 지원을 받아 수행됐다.

2022.08.25 조회수 11108

전자장비의 높은 전력 소모 한계를 뛰어넘는 저전력 고성능 다이오드 소자 최초 개발

우리 대학 물리학과 조성재 교수 연구팀이 기존 흔히 쓰이는 쇼트키 다이오드(Schottky diode)가 갖는 열적 거동의 한계를 뛰어넘는 저전력 정류 소자를 세계 최초로 개발하는 데 성공했다고 25일 밝혔다.

조 교수 연구팀은 단층 흑연, 즉, 그래핀(graphene)이 가지는 선형적 분산 관계의 전자 띠 구조 (linear dispersion band structure)를 이용해 열적 거동 한계(thermionic limit)를 극복한 다이오드를 최초로 구현하는 데 성공했다.

다이오드 전극으로 기존 다이오드에서 활용되었던 금속을 사용하는 대신, 그래핀을 활용함으로써 기존 다이오드의 이상지수 (ideality factor)의 한계를 뛰어넘는 초 이상적(super-ideal) 저전력 정류 소자를 개발하는 데 성공할 수 있었다.

물리학과 조성재 교수 연구실의 명규호 박사, 신원길 박사, 성경환 박사과정이 공동 제1 저자로 참여한 이번 연구는 국제 학술지 `네이쳐 커뮤니케이션스 (Nature Communications)' 7월 온라인판에 출판됐다. (논문명 : Dirac-source diode with sub-unity ideality factor).

현대 정보화 기술 발전에 따라 트랜지스터 소형화 및 집적도 증가가 꾸준히 이뤄졌고, 열 전하 방출(thermionic emission)의 물리적 특성에 의해 제한되는 문턱전압이하 스윙(subthreshold swing, SS, 트랜지스터에서 전류를 10배 증가시키는 데 필요한 전압의 값)이 60mV/dec 라는 한계를 뛰어넘는 트랜지스터에 대한 연구가 이뤄져왔다. 다이오드는 믹서, 셀렉터, 스위치, 광센서, 태양광 소자 등 많은 전자 장비에 쓰임에도 불구하고 열 전하 방출에 의한 열적 거동 한계를 뛰어넘는 연구는 이뤄지지 않고 있다.

반도체 물질과 금속이 접합됐을 때 두 물질의 계면에서 형성되는 쇼트키 장벽에 의해 정류 현상이 일어나는 쇼트키 다이오드의 성능은 크게 정류비(rectifying ratio, 온(on) 상태와 오프(off) 상태 전압의 비)와 이상 지수 (ideality factor)로 나눌 수 있다. 쇼트키 다이오드의 이상 지수는 다이오드의 전류를 10배 증가시키는 데 필요한 전압의 값과 연관된 수치이며, 열적 거동 한계로 인해 상온에서의 일반적인 쇼트키 다이오드는 이상 지수 1 이상의 값을 반드시 가지는 것으로 알려져 있다.

연구팀은 이번 연구에서 단층의 이황화 몰리브덴에 일함수가 다른 단층 그래핀과 다층 그래핀의 비대칭적 접촉을 통해 계면 문제를 해결한 쇼트키 다이오드를 구현했다. 단층의 흑연, 즉, 그래핀은 선형적 분산 관계의 전자 띠 구조를 가지고 있는 물질로, 일반적인 금속과는 달리 에너지에 따라 전하 밀도가 급격히 증감하는 성질을 갖고 있다.

이번 연구에서 새롭게 개발한 그래핀 소스를 이용한 디랙 소스(Dirac-source) 다이오드는 넓은 전류 작동범위 (1-10,000배 전류 범위)에서 이상 지수의 값이 1 미만을 갖는 열적 거동의 한계를 극복한 성능을 달성했으며, 다이오드의 온(on) 상태와 오프(off) 상태의 비율인 정류비가 1억(108) 이상으로, 기존에 보고되어왔던 다이오드보다 2-10배 낮은 전압으로도 기존의 다이오드보다 높은 전류의 정류 작동이 가능함을 보였다.

연구팀이 1 미만의 이상 지수를 갖는 고성능 저전력 쇼트키 다이오드를 개발한 것은 세계 최초로서 2차원 물질 기반의 저전력 다이오드 소자가 미래의 저전력 트랜지스터의 개발과 발맞춰 다양한 저전력 집적회로의 구성이 가능해질 수 있음을 의미한다.

물리학과 조성재 교수는 "이번 연구는 세계 최초로 물리적인 열적 거동 한계를 뛰어넘는 저전력, 고성능의 다이오드 소자를 발명한 것으로, 최소한의 전압과 전력으로 태양광 소자나 광검출기와 같은 미래 산업에서의 활용성이 높을 것으로 기대한다ˮ라고 말했다.

한편 이번 연구는 한국연구재단의 지능형 반도체 선도기술 개발사업과 중견연구자지원사업의 지원을 받아 수행됐다.

2022.08.25 조회수 11108 -

집속 이온빔을 이용해 양자점 양자 광원의 순도 향상 기술개발

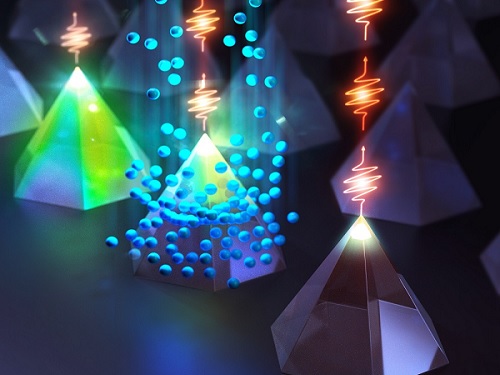

우리 대학 물리학과 조용훈 교수 연구팀이 집속 이온빔을 이용해 반도체 피라미드 구조의 꼭짓점에 형성된 단일 양자점(퀀텀닷)의 단광자 순도를 높이는 기술을 개발하는 데 성공했다고 29일 밝혔다.

이번 연구를 통해 개발된 기술은 향후 피라미드 꼭짓점 같이 위치를 정확히 제어하여 형성된 양자 광원뿐만 아니라 고밀도 양자점 기반 양자 광원, 전기 구동 양자점 기반 양자 광원 등 다양한 양자 광소자에 활용될 수 있을 것으로 기대된다.

양자 광원은 동시에 두 개 이상의 광자를 방출하지 않고 한 개의 광자씩만 방출하는 광원으로, 양자역학의 비복제 원리(no-cloning theorem)에 의해 단일 양자 정보를 복사할 수 없다는 점에서 해킹에 대해 안전한 양자 통신에 쓰일 수 있다. 특히 반도체 기반 양자점은 칩 상에 집적할 수 있고 전기 구동 또한 가능하다는 점에서 실용성이 높은 양자 광원으로써 널리 연구되고 있다.

하지만 반도체 양자점 기반 양자 광원에는 양자점 주변 구조에서 발생하는 배경 잡음(background signal)이 공존하게 되는데, 이러한 배경 잡음은 양자광으로서의 성질을 약하게 만들어 양자광이 해킹당할 가능성이 생기게 된다. 따라서 반도체 양자점을 실질적인 양자 광원으로 사용하기 위해서는 배경 잡음을 줄여 양자광의 신호 대 잡음비를 크게 만드는 것이 중요한 요소라 할 수 있다.

기존의 연구들에서는 양자 광원 주변의 배경 잡음을 줄여 신호 대 잡음비를 개선하기 위해 배경 잡음 신호가 나오는 부분을 에칭으로 제거하거나, 금속으로 막아버리는 등의 방법을 사용했다. 하지만, 이러한 방법들은 양자점의 양자광 신호를 감소시키거나, 양자점 주변의 구조를 파괴한다는 약점이 있었다.

조용훈 교수 연구팀은 집속 이온빔을 이용해 양자점 주변의 구조를 물리적으로 파괴하지 않고, 양자광 신호도 약화시키지 않은 채 배경 잡음 신호만을 효과적으로 제거할 수 있는 기술을 개발했고, 이를 반도체 피라미드 구조의 꼭짓점에 정교하게 형성된 양자점에 적용했다.

집속 이온빔 기술은 반도체 기술이나 생물학 등의 분야에서 에칭을 통한 나노 구조 제작이나 이미징 테스트를 위한 시료 제작 등에 널리 쓰여 왔다. 하지만 집속 이온빔을 빛을 내는 반도체 광소자나 광 집적회로를 제작하는 데 이용하게 되면, 이온 빔을 맞은 곳보다 훨씬 넓은 주변 영역에 이르기까지 결함 구조를 생성해 원하는 발광 신호를 크게 약화하는 문제가 있었다. 하지만 조용훈 교수 연구팀은 집속 이온빔의 종류와 조건을 정밀하게 조절하면 반도체 구조를 파괴하지 않으면서 배경 잡음 신호 만을 나노스케일의 공간해상도로 선택적으로 소광(luminescence quenching) 할 수 있다는 점에 착안했다.

이를 이용해 반도체 피라미드 구조의 꼭짓점에 있는 양자점 주변의 배경 잡음 신호를 나노스케일로 소광하는 데 성공했고, 이에 따라 나오는 발광 신호가 얼마나 양자광에 가까운지를 나타내는 지표인 단광자 순도를 크게 개선시켰다.

이는 양자점의 발광 신호와 구조체를 파괴하지 않고 배경 잡음만을 나노스케일로 소광할 수 있는 기술을 최초로 개발해, 피라미드 꼭짓점과 같이 위치가 제어된 양자점 뿐만 아니라 다양한 반도체 양자점 기반의 양자 광소자나 광 집적회로에서 원하지 않는 신호를 선택적으로 제거하여 소자의 성능을 높이는데 활용될 수 있는 결과라는 점에서 의미가 있다.

연구를 주도한 조용훈 교수는 "집속 이온빔을 이용해 원하지 않는 주변 배경 잡음 신호를 선택적으로 소광할 수 있는 고분해능 기법을 개발했고, 이는 다양한 양자 광소자와 광 집적회로, 그리고 디스플레이 분야에도 응용될 수 있는 기반 기술이 될 것ˮ이라고 말했다.

우리 대학 물리학과 최민호 박사과정과 전성문 박사과정이 공동 제 1저자로 참여한 이번 연구 결과는 삼성미래기술육성사업과 한국연구재단의 중견연구자지원사업의 지원을 받아 수행됐으며, 나노 과학 분야의 세계적 학술지인 `ACS 나노 (ACS Nano)' 7월 27일 字에 정식 출간됐다. (논문명: Nanoscale focus pinspot for high purity quantum emitters via focused-ion-beam induced luminescence quenching)

2021.07.30 조회수 13526

집속 이온빔을 이용해 양자점 양자 광원의 순도 향상 기술개발

우리 대학 물리학과 조용훈 교수 연구팀이 집속 이온빔을 이용해 반도체 피라미드 구조의 꼭짓점에 형성된 단일 양자점(퀀텀닷)의 단광자 순도를 높이는 기술을 개발하는 데 성공했다고 29일 밝혔다.

이번 연구를 통해 개발된 기술은 향후 피라미드 꼭짓점 같이 위치를 정확히 제어하여 형성된 양자 광원뿐만 아니라 고밀도 양자점 기반 양자 광원, 전기 구동 양자점 기반 양자 광원 등 다양한 양자 광소자에 활용될 수 있을 것으로 기대된다.

양자 광원은 동시에 두 개 이상의 광자를 방출하지 않고 한 개의 광자씩만 방출하는 광원으로, 양자역학의 비복제 원리(no-cloning theorem)에 의해 단일 양자 정보를 복사할 수 없다는 점에서 해킹에 대해 안전한 양자 통신에 쓰일 수 있다. 특히 반도체 기반 양자점은 칩 상에 집적할 수 있고 전기 구동 또한 가능하다는 점에서 실용성이 높은 양자 광원으로써 널리 연구되고 있다.

하지만 반도체 양자점 기반 양자 광원에는 양자점 주변 구조에서 발생하는 배경 잡음(background signal)이 공존하게 되는데, 이러한 배경 잡음은 양자광으로서의 성질을 약하게 만들어 양자광이 해킹당할 가능성이 생기게 된다. 따라서 반도체 양자점을 실질적인 양자 광원으로 사용하기 위해서는 배경 잡음을 줄여 양자광의 신호 대 잡음비를 크게 만드는 것이 중요한 요소라 할 수 있다.

기존의 연구들에서는 양자 광원 주변의 배경 잡음을 줄여 신호 대 잡음비를 개선하기 위해 배경 잡음 신호가 나오는 부분을 에칭으로 제거하거나, 금속으로 막아버리는 등의 방법을 사용했다. 하지만, 이러한 방법들은 양자점의 양자광 신호를 감소시키거나, 양자점 주변의 구조를 파괴한다는 약점이 있었다.

조용훈 교수 연구팀은 집속 이온빔을 이용해 양자점 주변의 구조를 물리적으로 파괴하지 않고, 양자광 신호도 약화시키지 않은 채 배경 잡음 신호만을 효과적으로 제거할 수 있는 기술을 개발했고, 이를 반도체 피라미드 구조의 꼭짓점에 정교하게 형성된 양자점에 적용했다.

집속 이온빔 기술은 반도체 기술이나 생물학 등의 분야에서 에칭을 통한 나노 구조 제작이나 이미징 테스트를 위한 시료 제작 등에 널리 쓰여 왔다. 하지만 집속 이온빔을 빛을 내는 반도체 광소자나 광 집적회로를 제작하는 데 이용하게 되면, 이온 빔을 맞은 곳보다 훨씬 넓은 주변 영역에 이르기까지 결함 구조를 생성해 원하는 발광 신호를 크게 약화하는 문제가 있었다. 하지만 조용훈 교수 연구팀은 집속 이온빔의 종류와 조건을 정밀하게 조절하면 반도체 구조를 파괴하지 않으면서 배경 잡음 신호 만을 나노스케일의 공간해상도로 선택적으로 소광(luminescence quenching) 할 수 있다는 점에 착안했다.

이를 이용해 반도체 피라미드 구조의 꼭짓점에 있는 양자점 주변의 배경 잡음 신호를 나노스케일로 소광하는 데 성공했고, 이에 따라 나오는 발광 신호가 얼마나 양자광에 가까운지를 나타내는 지표인 단광자 순도를 크게 개선시켰다.

이는 양자점의 발광 신호와 구조체를 파괴하지 않고 배경 잡음만을 나노스케일로 소광할 수 있는 기술을 최초로 개발해, 피라미드 꼭짓점과 같이 위치가 제어된 양자점 뿐만 아니라 다양한 반도체 양자점 기반의 양자 광소자나 광 집적회로에서 원하지 않는 신호를 선택적으로 제거하여 소자의 성능을 높이는데 활용될 수 있는 결과라는 점에서 의미가 있다.

연구를 주도한 조용훈 교수는 "집속 이온빔을 이용해 원하지 않는 주변 배경 잡음 신호를 선택적으로 소광할 수 있는 고분해능 기법을 개발했고, 이는 다양한 양자 광소자와 광 집적회로, 그리고 디스플레이 분야에도 응용될 수 있는 기반 기술이 될 것ˮ이라고 말했다.

우리 대학 물리학과 최민호 박사과정과 전성문 박사과정이 공동 제 1저자로 참여한 이번 연구 결과는 삼성미래기술육성사업과 한국연구재단의 중견연구자지원사업의 지원을 받아 수행됐으며, 나노 과학 분야의 세계적 학술지인 `ACS 나노 (ACS Nano)' 7월 27일 字에 정식 출간됐다. (논문명: Nanoscale focus pinspot for high purity quantum emitters via focused-ion-beam induced luminescence quenching)

2021.07.30 조회수 13526 -

임성갑 교수, 새로운 다층 금속 상호연결 기술 개발

우리 대학 생명화학공학과 임성갑 교수와 POSTECH(총장 김도연) 창의IT융합공학과 김재준 교수 공동 연구팀이 비아홀(via-hole, vertical interconnect access hole) 공정 없이도 금속을 다중으로 상호 연결할 수 있는 기술을 개발했고, 이를 통해 5층 이상의 3차원 고성능 유기 집적회로를 구현했다.

이번 기술은 금속의 수직 상호 연결을 위해 공간을 뚫는 작업인 비아홀 공정 대신 패턴된 절연막을 직접 쌓는 방식으로, 유기 반도체 집적회로를 형성하는데 적용할 수 있는 신개념의 공정이다.

유호천 박사와 박홍근 박사과정 학생이 공동 1 저자로 참여한 이번 연구 결과는 국제적인 학술지인 네이처 커뮤니케이션(Nature Communications) 6월 3일 자 온라인판에 게재됐다. (논문명: Highly stacked 3D organic integrated circuits with via-hole-less multilevel metal interconnects)

유기 트랜지스터는 구부리거나 접어도 그 특성을 그대로 유지할 수 있는 장점 덕분에 유연(flexible) 디스플레이 및 웨어러블 센서 등 다양한 분야에 적용할 수 있다.

그러나 이러한 유기물 반도체는 화학적 용매, 플라즈마, 고온 등에 의해 쉽게 손상되는 문제점 때문에 일반적인 식각 공정을 적용할 수 없어 유기 트랜지스터 기반 집적회로 구현의 걸림돌로 여겨졌다.

공동 연구팀은 유기물 반도체의 손상 없이 안정적인 금속 전극 접속을 위해 절연막에 비아홀을 뚫는 기존 방식에서 벗어나 패턴된 절연막을 직접 쌓는 방식을 택했다. 패턴된 절연막은 패턴 구조에 따라 반도체소자를 선택적으로 연결할 수 있도록 했다.

특히 연구팀은 ‘개시제를 이용한 화학 기상 증착법(iCVD: initiated chemical vapor deposition)’을 통해 얇고 균일한 절연막 패턴을 활용해 안정적인 트랜지스터 및 집적회로를 구현하는 데 성공했다.

공동 연구팀은 긴밀한 협력을 통해 개발한 금속 상호 연결 방법이 유기물 손상 없이 100%에 가까운 소자 수율로 유기 트랜지스터를 제작할 수 있음을 확인했다. 제작된 트랜지스터는 탁월한 소자 신뢰성 및 균일성을 보여 유기 집적회로 제작에 큰 역할을 했다.

연구팀은 수직적으로 분포된 트랜지스터들을 상호 연결해 인버터, 낸드, 노어 등 다양한 디지털 논리 회로를 구현하는 데 성공했다. 또한, 효과적인 금속 상호 연결을 위한 레이아웃 디자인 규칙을 제안했다. 이러한 성과는 향후 유기 반도체 기반 집적회로 구현 연구에 유용한 지침이 될 것으로 기대된다.

연구책임자인 POSTECH 김재준 교수는 “패턴된 절연막을 이용하는 발상의 전환이 유기 집적회로로 가기 위한 핵심 기술의 원천이 됐다”라며 “향후 유기 반도체 뿐 아니라 다양한 반도체 집적회로 구현의 핵심적인 역할을 할 것으로 기대한다”라고 말했다.

본 연구는 과학기술정보통신부, 한국연구재단과 삼성전자 미래기술육성센터의 지원을 받아 수행됐다.

□ 그림 설명

그림1. 제안된 금속 상호 연결 기술 모식도

그림2. 수직 집적된 디지털 회로 공정 모식도 및 이미지

2019.06.11 조회수 20284

임성갑 교수, 새로운 다층 금속 상호연결 기술 개발

우리 대학 생명화학공학과 임성갑 교수와 POSTECH(총장 김도연) 창의IT융합공학과 김재준 교수 공동 연구팀이 비아홀(via-hole, vertical interconnect access hole) 공정 없이도 금속을 다중으로 상호 연결할 수 있는 기술을 개발했고, 이를 통해 5층 이상의 3차원 고성능 유기 집적회로를 구현했다.

이번 기술은 금속의 수직 상호 연결을 위해 공간을 뚫는 작업인 비아홀 공정 대신 패턴된 절연막을 직접 쌓는 방식으로, 유기 반도체 집적회로를 형성하는데 적용할 수 있는 신개념의 공정이다.

유호천 박사와 박홍근 박사과정 학생이 공동 1 저자로 참여한 이번 연구 결과는 국제적인 학술지인 네이처 커뮤니케이션(Nature Communications) 6월 3일 자 온라인판에 게재됐다. (논문명: Highly stacked 3D organic integrated circuits with via-hole-less multilevel metal interconnects)

유기 트랜지스터는 구부리거나 접어도 그 특성을 그대로 유지할 수 있는 장점 덕분에 유연(flexible) 디스플레이 및 웨어러블 센서 등 다양한 분야에 적용할 수 있다.

그러나 이러한 유기물 반도체는 화학적 용매, 플라즈마, 고온 등에 의해 쉽게 손상되는 문제점 때문에 일반적인 식각 공정을 적용할 수 없어 유기 트랜지스터 기반 집적회로 구현의 걸림돌로 여겨졌다.

공동 연구팀은 유기물 반도체의 손상 없이 안정적인 금속 전극 접속을 위해 절연막에 비아홀을 뚫는 기존 방식에서 벗어나 패턴된 절연막을 직접 쌓는 방식을 택했다. 패턴된 절연막은 패턴 구조에 따라 반도체소자를 선택적으로 연결할 수 있도록 했다.

특히 연구팀은 ‘개시제를 이용한 화학 기상 증착법(iCVD: initiated chemical vapor deposition)’을 통해 얇고 균일한 절연막 패턴을 활용해 안정적인 트랜지스터 및 집적회로를 구현하는 데 성공했다.

공동 연구팀은 긴밀한 협력을 통해 개발한 금속 상호 연결 방법이 유기물 손상 없이 100%에 가까운 소자 수율로 유기 트랜지스터를 제작할 수 있음을 확인했다. 제작된 트랜지스터는 탁월한 소자 신뢰성 및 균일성을 보여 유기 집적회로 제작에 큰 역할을 했다.

연구팀은 수직적으로 분포된 트랜지스터들을 상호 연결해 인버터, 낸드, 노어 등 다양한 디지털 논리 회로를 구현하는 데 성공했다. 또한, 효과적인 금속 상호 연결을 위한 레이아웃 디자인 규칙을 제안했다. 이러한 성과는 향후 유기 반도체 기반 집적회로 구현 연구에 유용한 지침이 될 것으로 기대된다.

연구책임자인 POSTECH 김재준 교수는 “패턴된 절연막을 이용하는 발상의 전환이 유기 집적회로로 가기 위한 핵심 기술의 원천이 됐다”라며 “향후 유기 반도체 뿐 아니라 다양한 반도체 집적회로 구현의 핵심적인 역할을 할 것으로 기대한다”라고 말했다.

본 연구는 과학기술정보통신부, 한국연구재단과 삼성전자 미래기술육성센터의 지원을 받아 수행됐다.

□ 그림 설명

그림1. 제안된 금속 상호 연결 기술 모식도

그림2. 수직 집적된 디지털 회로 공정 모식도 및 이미지

2019.06.11 조회수 20284 -

최성율, 박상희 교수, 전자기기용 저전력 멤리스터 집적회로 개발

우리 대학 전기및전자공학부 최성율 교수와 신소재공학과 박상희 교수 공동 연구팀이 메모리와 레지스터의 합성어인 멤리스터(Memristor)를 이용해 저전력 비휘발성 로직-인-메모리 집적회로를 개발했다.

레지스터, 커패시터, 인덕터에 이어 4번째 전자 회로 소자인 멤리스터를 통한 기술로 새로운 컴퓨팅 아키텍처(하드웨어와 소프트웨어를 포함한 컴퓨터 시스템 전체 설계방식)를 제공할 수 있을 것으로 기대된다.

장병철, 남윤용 박사과정이 공동 1저자로 참여한 이번 연구는 재료분야 국제 학술지 ‘어드밴스드 펑셔널 머티리얼즈(Advanced Functional Materials)’ 1월 10일자 표지 논문으로 게재됐다.

4차 산업혁명 시대는 사물인터넷, 인공지능 등의 정보통신 기술 기반을 통해 발전되고 있으며 이는 사용자 친화적인 유연, 웨어러블 기기를 활용해 제공될 것으로 보여진다.

이러한 측면에서 저전력 배터리를 기반으로 한 소프트 전자기기의 개발에 대한 필요성이 커지고 있다.

하지만 기존 트랜지스터로 구성된 메모리와 로직회로 기반의 전자 시스템은 문턱전압 이하 수준의 트랜지스터 누설 전류(subthreshold leakage current)에 의한 대기전력 소모로 인해 휴대용 전자기기로의 응용에 한계가 있었다. 또한 기존 메모리와 프로세서가 분리돼 있어 데이터를 주고받는 과정에서 전력과 시간이 소모되는 문제점도 있었다.

연구팀은 문제 해결을 위해 정보의 저장과 로직 연산 기능을 동시에 구현할 수 있는 로직-인-메모리 집적회로를 개발했다.

플라스틱 기판 위에 비휘발성의 고분자 소재를 이용한 멤리스터, 산화물 반도체 소재를 이용한 유연 쇼트키 다이오드 선택소자(Schottky Diode Selector)를 수직으로 집적해 선택소자와 멤리스터가 일대일로 짝을 이루는 1S-1M 집적소자 어레이를 구현했다.

연구팀은 기존의 아키텍처와는 달리 대기 전력을 거의 소모하지 않는 비휘발성 로직-인-메모리 집적회로를 구현해 새로운 컴퓨팅 아키텍처를 개발했다. 또한 어레이 상에서 소자 간에 흐르는 스니크(sneak) 전류라고 불리는 누설 전류 문제도 해결했다.

그 밖에도 연구팀의 기술은 병렬 컴퓨터 방식인 하나의 명령어로 여러 값을 동시에 계산하는 단일 명령 다중 데이터 처리(Single-Instruction Multiple-Data, SIMD)를 구현했다.

최 교수는 “멤리스터와 선택소자의 집적을 통해 유연한 로직-인-메모리 집적회로를 구현한 이번 연구는 유연성과 저전력성을 가진 메모리와 로직을 동시에 제공한다”며 “모바일 및 웨어러블 전자시스템의 혁신을 가져 올 수 있는 원천기술을 확보했다는 의의를 갖는다”고 말했다.

이번 연구는 과학기술정보통신부 한국연구재단이 추진하는 글로벌프론티어사업 등의 지원을 받아 수행됐다.

□ 그림 설명

그림1. 저널에 게재된 표지논문 사진

그림2 유연 멤리스티브 비휘발성 로직-인-메모리 회로와 소자 단면 고해상도 투과전자현미경 이미지

그림3. 비휘발성 메모리 소자 응용을 위한 인가전압에 따른 소자 성능 확인

그림4. 유연 1S-1M 집적 소자 어레이의 병렬 로직 연산

2018.02.13 조회수 23525

최성율, 박상희 교수, 전자기기용 저전력 멤리스터 집적회로 개발

우리 대학 전기및전자공학부 최성율 교수와 신소재공학과 박상희 교수 공동 연구팀이 메모리와 레지스터의 합성어인 멤리스터(Memristor)를 이용해 저전력 비휘발성 로직-인-메모리 집적회로를 개발했다.

레지스터, 커패시터, 인덕터에 이어 4번째 전자 회로 소자인 멤리스터를 통한 기술로 새로운 컴퓨팅 아키텍처(하드웨어와 소프트웨어를 포함한 컴퓨터 시스템 전체 설계방식)를 제공할 수 있을 것으로 기대된다.

장병철, 남윤용 박사과정이 공동 1저자로 참여한 이번 연구는 재료분야 국제 학술지 ‘어드밴스드 펑셔널 머티리얼즈(Advanced Functional Materials)’ 1월 10일자 표지 논문으로 게재됐다.

4차 산업혁명 시대는 사물인터넷, 인공지능 등의 정보통신 기술 기반을 통해 발전되고 있으며 이는 사용자 친화적인 유연, 웨어러블 기기를 활용해 제공될 것으로 보여진다.

이러한 측면에서 저전력 배터리를 기반으로 한 소프트 전자기기의 개발에 대한 필요성이 커지고 있다.

하지만 기존 트랜지스터로 구성된 메모리와 로직회로 기반의 전자 시스템은 문턱전압 이하 수준의 트랜지스터 누설 전류(subthreshold leakage current)에 의한 대기전력 소모로 인해 휴대용 전자기기로의 응용에 한계가 있었다. 또한 기존 메모리와 프로세서가 분리돼 있어 데이터를 주고받는 과정에서 전력과 시간이 소모되는 문제점도 있었다.

연구팀은 문제 해결을 위해 정보의 저장과 로직 연산 기능을 동시에 구현할 수 있는 로직-인-메모리 집적회로를 개발했다.

플라스틱 기판 위에 비휘발성의 고분자 소재를 이용한 멤리스터, 산화물 반도체 소재를 이용한 유연 쇼트키 다이오드 선택소자(Schottky Diode Selector)를 수직으로 집적해 선택소자와 멤리스터가 일대일로 짝을 이루는 1S-1M 집적소자 어레이를 구현했다.

연구팀은 기존의 아키텍처와는 달리 대기 전력을 거의 소모하지 않는 비휘발성 로직-인-메모리 집적회로를 구현해 새로운 컴퓨팅 아키텍처를 개발했다. 또한 어레이 상에서 소자 간에 흐르는 스니크(sneak) 전류라고 불리는 누설 전류 문제도 해결했다.

그 밖에도 연구팀의 기술은 병렬 컴퓨터 방식인 하나의 명령어로 여러 값을 동시에 계산하는 단일 명령 다중 데이터 처리(Single-Instruction Multiple-Data, SIMD)를 구현했다.

최 교수는 “멤리스터와 선택소자의 집적을 통해 유연한 로직-인-메모리 집적회로를 구현한 이번 연구는 유연성과 저전력성을 가진 메모리와 로직을 동시에 제공한다”며 “모바일 및 웨어러블 전자시스템의 혁신을 가져 올 수 있는 원천기술을 확보했다는 의의를 갖는다”고 말했다.

이번 연구는 과학기술정보통신부 한국연구재단이 추진하는 글로벌프론티어사업 등의 지원을 받아 수행됐다.

□ 그림 설명

그림1. 저널에 게재된 표지논문 사진

그림2 유연 멤리스티브 비휘발성 로직-인-메모리 회로와 소자 단면 고해상도 투과전자현미경 이미지

그림3. 비휘발성 메모리 소자 응용을 위한 인가전압에 따른 소자 성능 확인

그림4. 유연 1S-1M 집적 소자 어레이의 병렬 로직 연산

2018.02.13 조회수 23525 -

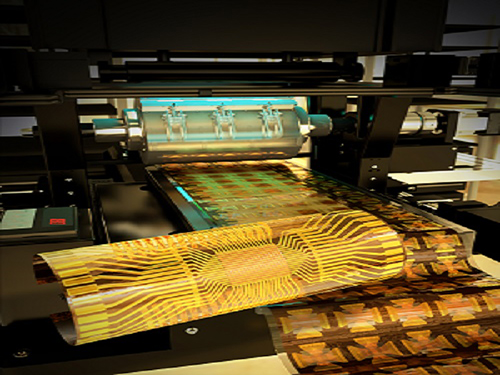

이건재 교수, 유연고집적회로의 연속적패키징 기술 개발

〈 이 건 재 교수 〉

우리 대학 신소재공학과 이건재 교수와 한국기계연구원 김재현 박사 공동 연구팀이 롤 기반 공정을 통해 플렉서블 기기의 핵심기술인 유연 고집적회로를 연속적으로 패키징(소자와 전자기기를 연결하는 전기적 포장) 및 전사(轉寫)할 수 있는 기술을 개발했다.

또한 개발된 롤 기반 전사 및 패키징 기술을 유연 낸드플래시 메모리(전원이 끊겨도 저장된 데이터를 잃어버리지 않는 비휘발성 메모리의 일종)에 적용하는데 성공했다.

이번 연구 결과는 재료과학 분야 학술지인 ‘어드밴스드 머티리얼즈(Advanced Materials)’ 7월 20일자 온라인 판에 게재됐다.

롤 공정(유연기판을 회전하는 롤에 감으며 동시에 공정을 진행하는 방식) 기반의 유연전자 생산기술은 높은 생산효율을 바탕으로 웨어러블 및 플렉서블 기기 상용화에 중요한 역할을 할 것으로 기대되고 있다.

그러나 지금까지는 고집적회로를 롤 공정으로 구현하는 방법 및 주변회로와 상호 연결하는 패키징 기술이 해결되지 않아 실용화에 한계가 있었다.

문제 해결을 위해 연구팀은 기존 반도체 공정을 이용해 실리콘 기판에 낸드 플래시 메모리를 형성한 후 수백 나노미터(10분의 1m) 두께로 얇게 만들었다.

그 후 개발한 롤 기반 전사 및 패키징 기술을 통해 소자를 유연기판에 옮기는 동시에 이방성 전도 필름을 이용해 상호 연결하는 기술을 구현했다.

연구팀의 최종적인 실리콘 기반 유연 낸드플래시 메모리는 반복적인 휘어짐에도 모든 기능이 정상적으로 동작했고 외부와의 상호연결도 매우 안정적으로 유지됐다.

개발된 롤 기반 유연 고집적회로 기술은 유연 어플리케이션 프로세서(AP), 고집적 메모리, 고속 통신소자 등의 양산에 응용 가능할 것으로 기대된다.

이 교수는 “높은 생산성을 지닌 롤 기반 전사 기술을 이용해 단결정 실리콘 박막 고집적회로를 유연한 인쇄회로 기판 위에 패키징하는 생산기술을 확보했다”며 “향후 유연 디스플레이 및 배터리 기술과 함께 휘어지는 컴퓨터 구현의 핵심 생산 기술이 될 것으로 기대된다”고 말했다.

김재현 박사는 “한국기계연구원이 보유한 롤 기반 전사 기술을 이용해 단결정 실리콘 고집적소자를 유연한 폴리머 인쇄회로 기판 상에 손상 없이 전사함과 동시에 소자와 인쇄회로기판이 전기적으로 연결되도록 하는 롤 기반의 생산 공정 기술을 개발하였다”며 “이 기술은 향후 고성능 전자 소자를 유연 기판 위에 형성해 사물인터넷 및 웨어러블용 고성능 전자기기를 제조하는 핵심 생산 기술이 될 것으로 전망한다.”라고 말했다.

이건재 교수는 2013년도에 0.18 씨모스(CMOS) 공정기반으로 컴퓨터의 두뇌에 해당하는 휘어지는 유연 고집적회로를 최초로 구현했다. 특히 반도체분야 최고 권위학회인 국제반도체소자학회(IEDM)에서 초청받아 발표하는 등 세계적인 주목을 받았다.

한국기계연구원 김재현 박사 연구팀은 2009년부터 롤 스탬프를 이용해 박막소자를 옮기는 기술을 연구하고 있다. 관련 롤 전사 장비 기술을 디스플레이 및 반도체 용도의 롤 장비 회사에 기술이전하기도 했다.

이번 연구는 2013년부터 진행된 한국기계연구원의 나노소재 응용 고성능 유연소자기술 기반구축사업의 일환으로 수행됐다. 이건재 교수는 교원창업을 통해 유연한 고집적회로 관련 기술 상용화를 계획 중이다.

□ 그림 설명

그림1. 연속 롤-패키징 공정의 개요 모식도

그림2. 제작된 유연 실리콘 낸드 플래시메모리

2016.09.01 조회수 19376

이건재 교수, 유연고집적회로의 연속적패키징 기술 개발

〈 이 건 재 교수 〉

우리 대학 신소재공학과 이건재 교수와 한국기계연구원 김재현 박사 공동 연구팀이 롤 기반 공정을 통해 플렉서블 기기의 핵심기술인 유연 고집적회로를 연속적으로 패키징(소자와 전자기기를 연결하는 전기적 포장) 및 전사(轉寫)할 수 있는 기술을 개발했다.

또한 개발된 롤 기반 전사 및 패키징 기술을 유연 낸드플래시 메모리(전원이 끊겨도 저장된 데이터를 잃어버리지 않는 비휘발성 메모리의 일종)에 적용하는데 성공했다.

이번 연구 결과는 재료과학 분야 학술지인 ‘어드밴스드 머티리얼즈(Advanced Materials)’ 7월 20일자 온라인 판에 게재됐다.

롤 공정(유연기판을 회전하는 롤에 감으며 동시에 공정을 진행하는 방식) 기반의 유연전자 생산기술은 높은 생산효율을 바탕으로 웨어러블 및 플렉서블 기기 상용화에 중요한 역할을 할 것으로 기대되고 있다.

그러나 지금까지는 고집적회로를 롤 공정으로 구현하는 방법 및 주변회로와 상호 연결하는 패키징 기술이 해결되지 않아 실용화에 한계가 있었다.

문제 해결을 위해 연구팀은 기존 반도체 공정을 이용해 실리콘 기판에 낸드 플래시 메모리를 형성한 후 수백 나노미터(10분의 1m) 두께로 얇게 만들었다.

그 후 개발한 롤 기반 전사 및 패키징 기술을 통해 소자를 유연기판에 옮기는 동시에 이방성 전도 필름을 이용해 상호 연결하는 기술을 구현했다.

연구팀의 최종적인 실리콘 기반 유연 낸드플래시 메모리는 반복적인 휘어짐에도 모든 기능이 정상적으로 동작했고 외부와의 상호연결도 매우 안정적으로 유지됐다.

개발된 롤 기반 유연 고집적회로 기술은 유연 어플리케이션 프로세서(AP), 고집적 메모리, 고속 통신소자 등의 양산에 응용 가능할 것으로 기대된다.

이 교수는 “높은 생산성을 지닌 롤 기반 전사 기술을 이용해 단결정 실리콘 박막 고집적회로를 유연한 인쇄회로 기판 위에 패키징하는 생산기술을 확보했다”며 “향후 유연 디스플레이 및 배터리 기술과 함께 휘어지는 컴퓨터 구현의 핵심 생산 기술이 될 것으로 기대된다”고 말했다.

김재현 박사는 “한국기계연구원이 보유한 롤 기반 전사 기술을 이용해 단결정 실리콘 고집적소자를 유연한 폴리머 인쇄회로 기판 상에 손상 없이 전사함과 동시에 소자와 인쇄회로기판이 전기적으로 연결되도록 하는 롤 기반의 생산 공정 기술을 개발하였다”며 “이 기술은 향후 고성능 전자 소자를 유연 기판 위에 형성해 사물인터넷 및 웨어러블용 고성능 전자기기를 제조하는 핵심 생산 기술이 될 것으로 전망한다.”라고 말했다.

이건재 교수는 2013년도에 0.18 씨모스(CMOS) 공정기반으로 컴퓨터의 두뇌에 해당하는 휘어지는 유연 고집적회로를 최초로 구현했다. 특히 반도체분야 최고 권위학회인 국제반도체소자학회(IEDM)에서 초청받아 발표하는 등 세계적인 주목을 받았다.

한국기계연구원 김재현 박사 연구팀은 2009년부터 롤 스탬프를 이용해 박막소자를 옮기는 기술을 연구하고 있다. 관련 롤 전사 장비 기술을 디스플레이 및 반도체 용도의 롤 장비 회사에 기술이전하기도 했다.

이번 연구는 2013년부터 진행된 한국기계연구원의 나노소재 응용 고성능 유연소자기술 기반구축사업의 일환으로 수행됐다. 이건재 교수는 교원창업을 통해 유연한 고집적회로 관련 기술 상용화를 계획 중이다.

□ 그림 설명

그림1. 연속 롤-패키징 공정의 개요 모식도

그림2. 제작된 유연 실리콘 낸드 플래시메모리

2016.09.01 조회수 19376 -

유회준 교수 연구팀, 세계 최초로 가슴에 붙이는 심장건강상태 모니터링 장치 개발

- 붙이는 파스형태의 심장 건강상태 모니터링 장치, ‘스마트 파스’ 세계 최초개발 -

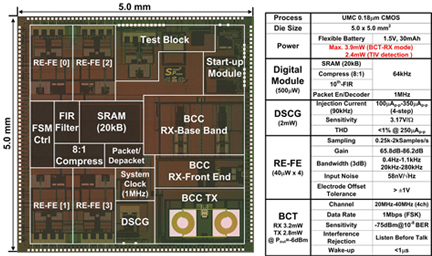

전기및전자공학과 유회준 교수 연구팀이 세계 최초로 가슴에 붙이는 심장건강상태 모니터링 장치를 최근 개발했다.

붙이는 파스형태로 제작돼 휴대폰 등의 휴대용 단말기기를 통하여 원격으로 켜고 끌 수 있으며 데이터통신도 가능하다.

고성능 반도체 집적회로(헬스케어 칩)가 파스 안에 장착돼 있고 파스 표면에 25개의 전극이 형성돼 있어 다양한 형태로 전극을 사용할 수 있으며 심장의 수축·이완 능력과 심전도 신호를 동시에 검출해 무선으로 외부에 알려 준다.

이 장치의 핵심은 크게 심혈관 저항 및 심전도 측정 집적회로(헬스케어 칩)와 이 칩을 내부에 장착하고 있으며 표면에 전극을 형성시킨 4층 헝겊형 기판기술이다.

직물 위에 전극 및 회로 기판을 직접 인쇄할 수 있는 P-FCB(Planar Fashionable Circuit Board)기술로 서로 다른 헝겊에 전극, 무선 안테나, 회로기판(이 헝겊의 중앙부에 헬스 케어 칩을 부착)형성한 후 플렉시블 배터리와 함께 적층해 이 장치를 제작했다.

또한 전극 제어부, 심전도·혈관 저항 측정부, 데이터 압축부, SRAM, 무선 송수신 장치 등을 가지고 초저전력으로 동작하는 특수 헬스 케어 집적회로(크기 5mm X 5mm)를 제작해 헝겊형 회로 기판 위에 부착시켰다.

전극이 형성된 헝겊 면에는 접착제가 발라져 있어 일반 파스처럼 가슴에 부착시켜 사용하게 된다. 완성품은 가로 세로 15Cm X 15Cm이며 두께는 가장 두꺼운 중앙 부분이 1mm정도이다.

특히, 헬스 케어 칩은 차동전류주입기와 재구성이 가능한 고감도 검출 회로를 통해 심혈관 임피던스 변화를 16가지 서로 다른 조합으로 0.81% 신호왜곡 이하로 검출 가능하다.

KAIST 얜롱(Yan Long, 전기및전자공학과 박사과정)연구원은 “헝겊 위에 직접 전극 배열을 인쇄하고 건강관리 칩과 플렉시블 배터리를 부착함으로서 편의성과 착용감을 확보해 간편하게 심전도와 심혈관 임피던스 변화를 동시에 측정할 수 있다.”라고 말했다.

자신의 건강상태를 실시간으로 간편하게 자가진단을 할 수 있어 지속적인 관리가 필요한 만성 심부전 환자 등을 포함한 심혈관 질병이 있는 사람들에게 안성맞춤이다.

만성 심혈관 관련 환자를 위한 건강관리 기술은 2000년 이후 전 세계적으로 꾸준한 관심을 받고 있으나, 대부분 심장의 전기적 특성 즉 심전도 신호만을 검출하는데 그쳤다. 현재까지 개발된 측정기는 크고 이물감이 있으며, 유선으로 연결되는 등 외부와의 저전력 통신이 어려워 일상생활에서 널리 사용되지 못하고 있다.

이번 연구결과는 지난 2월 8일부터 10일까지 미국 샌프란시스코에서 개최된 국제반도체회로 학술회의(ISSCC)에 발표됐다.

❋ ISSCC (International Solid State Circuit Conference: 국제 고체 회로 학회)학회:1954년부터 국제 전기전자공학회 (IEEE SSCS) 주관으로 매년 2월에 미국 San Francisco, Marriot 호텔에서 개최되는 이 분야 최고 권위의 학회로 ‘반도체 올림픽’이라고 불리우고 있음. 전 세계로부터 4천여명의 학자와 연구원들이 참여한 가운데 매년 반도체 분야 최우수 논문 210편만을 엄선하여 3일 동안 발표하면서 연구 성과와 정보를 교환하고 미래의 반도체 산업과 기술을 논의하는 학회임.

(사진 1) 스마트 파스 구조

스마트 파스는 총 4층 구조로 형성 되어 있으며 그 크기는 15cm x 15cm 이다. 가슴에 부착하는 면인 제 1층은 25개의 전극이 형성되어 이 중 4개는 전류 주입 전극으로 16개는 전압 측정 전극으로 5개는 기준 전극으로 사용할 수 있다. 제 2층은 직물형 인덕터(2.2uH, Q=9.2)로 스마트 파스의 무선 데이터 통신을 지원한다. 제 3층은 플렉시블 배터리(1.5V, 30mAh)로 파스를 하루이상 지속적으로 사용할 수 있도록 전원을 공급한다. 제 4층은 직물형 인쇄 회로 기판으로 그 위에 고성능 반도체 칩이 장착되어 있다.

(사진 2) 스마트 파스 사용 예

사용자가 스마트 파스를 가슴에 붙인 모습을 보여 준다. 휴대폰 등의 휴대용 단말기기를 통하여 원격으로 켜고 끌 수 있으며 25개의 전극배열이 피부와 접착되어 있어 심혈관 저항 및 심전도를 여러 가지 형태로 측정하여 내장메모리에 저장 또는 휴대용 단말기기로데이터를 고속으로 송신도 가능하다.

(사진 3) 스마트 파스 측정 예스마트 파스를 통하여 측정된 심전도 신호와 심혈관의 저항의 변화를 보여 준다. 이러한 신호로부터 심장의 수축 이완 능력을 편리하게 일상생활 속에서 측정 가능하다.

(사진 4) 스마트 파스에 장착된 헬스 케어 칩

직물형 인쇄 회로 기판에 장착되어 있는 고성능 반도체칩(헬스케어 칩)의 사진과 제원이다. 본 헬스케어 칩은 최대 3.9mW의 전력을 소모하며 평균 2.4mW의 전력소비로 0.1옴이하의 저항 변화를 고감도 회로를 통하여 검출 가능케 하는 것이 특징이다.

2010.02.10 조회수 24880

유회준 교수 연구팀, 세계 최초로 가슴에 붙이는 심장건강상태 모니터링 장치 개발

- 붙이는 파스형태의 심장 건강상태 모니터링 장치, ‘스마트 파스’ 세계 최초개발 -

전기및전자공학과 유회준 교수 연구팀이 세계 최초로 가슴에 붙이는 심장건강상태 모니터링 장치를 최근 개발했다.

붙이는 파스형태로 제작돼 휴대폰 등의 휴대용 단말기기를 통하여 원격으로 켜고 끌 수 있으며 데이터통신도 가능하다.

고성능 반도체 집적회로(헬스케어 칩)가 파스 안에 장착돼 있고 파스 표면에 25개의 전극이 형성돼 있어 다양한 형태로 전극을 사용할 수 있으며 심장의 수축·이완 능력과 심전도 신호를 동시에 검출해 무선으로 외부에 알려 준다.

이 장치의 핵심은 크게 심혈관 저항 및 심전도 측정 집적회로(헬스케어 칩)와 이 칩을 내부에 장착하고 있으며 표면에 전극을 형성시킨 4층 헝겊형 기판기술이다.

직물 위에 전극 및 회로 기판을 직접 인쇄할 수 있는 P-FCB(Planar Fashionable Circuit Board)기술로 서로 다른 헝겊에 전극, 무선 안테나, 회로기판(이 헝겊의 중앙부에 헬스 케어 칩을 부착)형성한 후 플렉시블 배터리와 함께 적층해 이 장치를 제작했다.

또한 전극 제어부, 심전도·혈관 저항 측정부, 데이터 압축부, SRAM, 무선 송수신 장치 등을 가지고 초저전력으로 동작하는 특수 헬스 케어 집적회로(크기 5mm X 5mm)를 제작해 헝겊형 회로 기판 위에 부착시켰다.

전극이 형성된 헝겊 면에는 접착제가 발라져 있어 일반 파스처럼 가슴에 부착시켜 사용하게 된다. 완성품은 가로 세로 15Cm X 15Cm이며 두께는 가장 두꺼운 중앙 부분이 1mm정도이다.

특히, 헬스 케어 칩은 차동전류주입기와 재구성이 가능한 고감도 검출 회로를 통해 심혈관 임피던스 변화를 16가지 서로 다른 조합으로 0.81% 신호왜곡 이하로 검출 가능하다.

KAIST 얜롱(Yan Long, 전기및전자공학과 박사과정)연구원은 “헝겊 위에 직접 전극 배열을 인쇄하고 건강관리 칩과 플렉시블 배터리를 부착함으로서 편의성과 착용감을 확보해 간편하게 심전도와 심혈관 임피던스 변화를 동시에 측정할 수 있다.”라고 말했다.

자신의 건강상태를 실시간으로 간편하게 자가진단을 할 수 있어 지속적인 관리가 필요한 만성 심부전 환자 등을 포함한 심혈관 질병이 있는 사람들에게 안성맞춤이다.

만성 심혈관 관련 환자를 위한 건강관리 기술은 2000년 이후 전 세계적으로 꾸준한 관심을 받고 있으나, 대부분 심장의 전기적 특성 즉 심전도 신호만을 검출하는데 그쳤다. 현재까지 개발된 측정기는 크고 이물감이 있으며, 유선으로 연결되는 등 외부와의 저전력 통신이 어려워 일상생활에서 널리 사용되지 못하고 있다.

이번 연구결과는 지난 2월 8일부터 10일까지 미국 샌프란시스코에서 개최된 국제반도체회로 학술회의(ISSCC)에 발표됐다.

❋ ISSCC (International Solid State Circuit Conference: 국제 고체 회로 학회)학회:1954년부터 국제 전기전자공학회 (IEEE SSCS) 주관으로 매년 2월에 미국 San Francisco, Marriot 호텔에서 개최되는 이 분야 최고 권위의 학회로 ‘반도체 올림픽’이라고 불리우고 있음. 전 세계로부터 4천여명의 학자와 연구원들이 참여한 가운데 매년 반도체 분야 최우수 논문 210편만을 엄선하여 3일 동안 발표하면서 연구 성과와 정보를 교환하고 미래의 반도체 산업과 기술을 논의하는 학회임.

(사진 1) 스마트 파스 구조

스마트 파스는 총 4층 구조로 형성 되어 있으며 그 크기는 15cm x 15cm 이다. 가슴에 부착하는 면인 제 1층은 25개의 전극이 형성되어 이 중 4개는 전류 주입 전극으로 16개는 전압 측정 전극으로 5개는 기준 전극으로 사용할 수 있다. 제 2층은 직물형 인덕터(2.2uH, Q=9.2)로 스마트 파스의 무선 데이터 통신을 지원한다. 제 3층은 플렉시블 배터리(1.5V, 30mAh)로 파스를 하루이상 지속적으로 사용할 수 있도록 전원을 공급한다. 제 4층은 직물형 인쇄 회로 기판으로 그 위에 고성능 반도체 칩이 장착되어 있다.

(사진 2) 스마트 파스 사용 예

사용자가 스마트 파스를 가슴에 붙인 모습을 보여 준다. 휴대폰 등의 휴대용 단말기기를 통하여 원격으로 켜고 끌 수 있으며 25개의 전극배열이 피부와 접착되어 있어 심혈관 저항 및 심전도를 여러 가지 형태로 측정하여 내장메모리에 저장 또는 휴대용 단말기기로데이터를 고속으로 송신도 가능하다.

(사진 3) 스마트 파스 측정 예스마트 파스를 통하여 측정된 심전도 신호와 심혈관의 저항의 변화를 보여 준다. 이러한 신호로부터 심장의 수축 이완 능력을 편리하게 일상생활 속에서 측정 가능하다.

(사진 4) 스마트 파스에 장착된 헬스 케어 칩

직물형 인쇄 회로 기판에 장착되어 있는 고성능 반도체칩(헬스케어 칩)의 사진과 제원이다. 본 헬스케어 칩은 최대 3.9mW의 전력을 소모하며 평균 2.4mW의 전력소비로 0.1옴이하의 저항 변화를 고감도 회로를 통하여 검출 가능케 하는 것이 특징이다.

2010.02.10 조회수 24880 -

세계에서 가장 작은 나노전자소자 공동 개발

KAIST 최양규 교수팀 / 나노종합팹센터 공동 연구

새로운 구조의 3차원 3nm급 나노전자소자(FinFET) 공동개발

현재 반도체소자 기술의 한계를 극복하여 향후 세계 반도체 시장에서 유리한 입지 확보

KAIST (총장 로버트 러플린) 최양규 교수팀과 나노종합팹센터(소장 이희철)가 테라급 차세대 반도체소자에 적용 가능한 세계에서 가장 작은 새로운 구조의 3차원 3nm급 ‘나노전자소자(FinFET)’를 공동 개발하는데 성공했다

이번에 공동 개발한 나노전자소자는 게이트가 채널의 전면을 감싸고 있는 새로운 형태의 3차원 구조를 고안하여 3nm급 트랜지스터를 개발한 것이다.

이것은 기존의 실리콘 반도체 기술의 한계를 한단계 진전시킨 의미 있는 연구 결과이다.

칩의 집적도를 높이기 위한 5nm급 나노소자 구현은 기존의 실리콘 기술이 아닌 탄소나노튜브나 분자소자 등과 같은 신소재를 사용해야 할 것으로 예상되었으나, 본 연구 결과는 실리콘 기술만으로도 5nm급 이하 소자 구현이 가능하고 ‘무어의 법칙’이 향후 20년 이상 계속 유지될 수 있다는 가능성을 제시했다.

현재까지 발표된 세계에서 가장 작은 소자는 2003년 12월 일본 NEC가 국제전자소자회의(IEDM)에서 발표한 ‘표준형 2차원 평면 소자구조를 이용한 4nm 소자’로 알려져 있으나, 이는 누설 전류가 크고 동작 시 충분한 전류를 얻지 못하는 등 만족스러운 소자 특성을 얻지는 못했다.

그러나 공동 개발된 3차원 구조(게이트가 채널의 전면을 감싸고 있는 구조)는 NEC의 4nm 소자에 비해 소자의 크기가 작을 뿐만 아니라 ‘단채널 효과’가 크게 개선된 결과를 얻었다.

이번에 공동 개발된 나노소자는 프로세서나 테라급 DRAM, SRAM, 플래시 메모리 소자로 응용이 가능하며, 휴대인터넷, 동영상 회의, 입는 컴퓨터 등의 차세대 정보처리 기기의 필수부품으로 사용될 것으로 전망되며, 컴퓨터의 두뇌에 해당되는 마이크로프로세서에 이 나노소자를 적용할 경우 처리속도가 100GHz (현재보다 25배 빠름)를 넘을 수 있을 것으로 예상된다.

전체 반도체 시장의 연평균 성장률을 7%로 가정할 경우 그 시장 규모가 2015년에는 480조로 예상되는데, 이 중 공동 개발된 3nm급 3차원 소자가 약 35% 정도를 차지할 것으로 기대된다.

이번 공동 연구개발을 통하여 얻은 차세대 나노 집적회로의 원천기술 및 응용기술은 앞으로도 우리나라가 세계 반도체 시장에서 유리한 입지를 확보하는데 기여할 것으로 평가된다.

이번 연구 성과는 오는 6월 13일 미국 하와이에서 개막되는 권위적인 국제 학술회의인 “초고집적회로 국제학회(Symposium on VLSI Technology)”에서 발표될 예정이다.

앞으로 한국과학기술원과 나노종합팹센터는 공동 프로젝트를 통하여 단위소자뿐만 아니라 3nm FinFET 제작 기술을 응용한 아날로그 및 디지털 RF 회로 등에 접목하는 양산성에 대한 추가적인 연구를 계속 진행할 예정이다.

※ 1테라 NAND 플래시는 엄지 손톱만한 크기의 칩 속에 12,500년분의 신문기사와 50만곡의 MP3 파일, 1,250편의 DVD 영화를 저장할 수 있고, 나노소자 칩을 가로, 세로에 각각 10개씩 배열하여 휴대하면 한 사람이 일생동안 보고 들은 것을 모두 저장할 수 있는 용량

2006.03.17 조회수 22661

세계에서 가장 작은 나노전자소자 공동 개발

KAIST 최양규 교수팀 / 나노종합팹센터 공동 연구

새로운 구조의 3차원 3nm급 나노전자소자(FinFET) 공동개발

현재 반도체소자 기술의 한계를 극복하여 향후 세계 반도체 시장에서 유리한 입지 확보

KAIST (총장 로버트 러플린) 최양규 교수팀과 나노종합팹센터(소장 이희철)가 테라급 차세대 반도체소자에 적용 가능한 세계에서 가장 작은 새로운 구조의 3차원 3nm급 ‘나노전자소자(FinFET)’를 공동 개발하는데 성공했다

이번에 공동 개발한 나노전자소자는 게이트가 채널의 전면을 감싸고 있는 새로운 형태의 3차원 구조를 고안하여 3nm급 트랜지스터를 개발한 것이다.

이것은 기존의 실리콘 반도체 기술의 한계를 한단계 진전시킨 의미 있는 연구 결과이다.

칩의 집적도를 높이기 위한 5nm급 나노소자 구현은 기존의 실리콘 기술이 아닌 탄소나노튜브나 분자소자 등과 같은 신소재를 사용해야 할 것으로 예상되었으나, 본 연구 결과는 실리콘 기술만으로도 5nm급 이하 소자 구현이 가능하고 ‘무어의 법칙’이 향후 20년 이상 계속 유지될 수 있다는 가능성을 제시했다.

현재까지 발표된 세계에서 가장 작은 소자는 2003년 12월 일본 NEC가 국제전자소자회의(IEDM)에서 발표한 ‘표준형 2차원 평면 소자구조를 이용한 4nm 소자’로 알려져 있으나, 이는 누설 전류가 크고 동작 시 충분한 전류를 얻지 못하는 등 만족스러운 소자 특성을 얻지는 못했다.

그러나 공동 개발된 3차원 구조(게이트가 채널의 전면을 감싸고 있는 구조)는 NEC의 4nm 소자에 비해 소자의 크기가 작을 뿐만 아니라 ‘단채널 효과’가 크게 개선된 결과를 얻었다.

이번에 공동 개발된 나노소자는 프로세서나 테라급 DRAM, SRAM, 플래시 메모리 소자로 응용이 가능하며, 휴대인터넷, 동영상 회의, 입는 컴퓨터 등의 차세대 정보처리 기기의 필수부품으로 사용될 것으로 전망되며, 컴퓨터의 두뇌에 해당되는 마이크로프로세서에 이 나노소자를 적용할 경우 처리속도가 100GHz (현재보다 25배 빠름)를 넘을 수 있을 것으로 예상된다.

전체 반도체 시장의 연평균 성장률을 7%로 가정할 경우 그 시장 규모가 2015년에는 480조로 예상되는데, 이 중 공동 개발된 3nm급 3차원 소자가 약 35% 정도를 차지할 것으로 기대된다.

이번 공동 연구개발을 통하여 얻은 차세대 나노 집적회로의 원천기술 및 응용기술은 앞으로도 우리나라가 세계 반도체 시장에서 유리한 입지를 확보하는데 기여할 것으로 평가된다.

이번 연구 성과는 오는 6월 13일 미국 하와이에서 개막되는 권위적인 국제 학술회의인 “초고집적회로 국제학회(Symposium on VLSI Technology)”에서 발표될 예정이다.

앞으로 한국과학기술원과 나노종합팹센터는 공동 프로젝트를 통하여 단위소자뿐만 아니라 3nm FinFET 제작 기술을 응용한 아날로그 및 디지털 RF 회로 등에 접목하는 양산성에 대한 추가적인 연구를 계속 진행할 예정이다.

※ 1테라 NAND 플래시는 엄지 손톱만한 크기의 칩 속에 12,500년분의 신문기사와 50만곡의 MP3 파일, 1,250편의 DVD 영화를 저장할 수 있고, 나노소자 칩을 가로, 세로에 각각 10개씩 배열하여 휴대하면 한 사람이 일생동안 보고 들은 것을 모두 저장할 수 있는 용량

2006.03.17 조회수 22661