%EB%B0%98%EB%8F%84%EC%B2%B4

-

KAIST, 인공지능 반도체 생태계를 선도하다

인공지능 반도체(이하 AI 반도체)가 국가적인 전략기술로 두드러지면서 KAIST의 관련 성과도 주목받고 있다. 과학기술정보통신부는 지난해 2030년 세계 AI 반도체 시장 20% 점유를 목표로 인공지능 반도체 지원사업에 본격적으로 착수한 바 있다. 올해에는 산학연 논의를 거쳐 5년간 1조 200억 원을 투입하는 `인공지능 반도체 산업 성장 지원대책'으로 지원을 확대했다. 이에 따라 AI 반도체 전문가 양성을 위해 주요 대학들의 행보도 분주해졌다.

KAIST는 반도체와 인공지능 양대 핵심 분야에서 최상급의 교육, 연구 역량을 쌓아 왔다. 반도체 분야에서는 지난 17년 동안 메사추세츠 공과대학(이하 MIT), 스탠퍼드(Stanford)와 같은 세계적인 학교를 제치고 국제반도체회로학회(이하 ISSCC, International Solid State Circuit Conference)에서 대학 중 1위를 지켜 왔다는 점이 돋보인다. ISSCC는 1954년 설립된 반도체 집적회로 설계 분야 세계 최고 권위 학회다. 참가자 중 60% 이상이 삼성, 퀄컴, TSMC, 인텔을 비롯한 산업계 소속일만큼 산업적인 실용성을 중시해서 `반도체 설계 올림픽'이라는 별명도 있다.

KAIST는 ISSCC에서 채택 논문 수 기준 매년 전 세계 대학교 중 1~2위를 유지했다. 최근 17년간 평균 채택 논문 수를 살펴보면 압도적인 선두다. 해당 기간 채택된 KAIST의 논문은 평균 8.4편으로, 경쟁자인 MIT(4.6편)와 캘리포니아대학교 로스앤젤레스(UCLA)(3.6편)에 비해 두 배 가까운 성과다. 국내에서는 반도체 설계 분야 부동의 1위인 삼성에 이어 종합 2위 자리를 유지하고 있다. 그럴 뿐만 아니라 ISSCC와 쌍벽을 이루는 집적회로 분야 학술대회인 초고밀도집적회로학회에서도 KAIST는 2022년 전 세계 대학 중 1위를 기록했다.

KAIST의 연구진들이 반도체 산업 핵심 분야 전반에서 신기술을 발표해 연구의 질적인 수준도 높다. 전기및전자공학부 정명수 교수 연구팀은 고성능 저전력을 추구하는 현재 업계의 수요에 대응해 전력 공급 없이도 동작을 유지하는 컴퓨터를 개발했다. 소재 분야에서는 신소재공학과의 박병국 교수 연구팀이 기존의 메모리에 비해 동작 속도가 10배 이상 빠른 `스핀궤도토크 자성메모리' 소자를 개발해서 기존 `폰노이만 구조'의 한계를 극복하는 방안을 제시하기도 했다.

이처럼 현재 반도체 산업의 주요 과제에 솔루션을 제공하는 한편으로 미래의 새로운 반도체 분야를 선점하는 데 필요한 신기술 개발도 활발하다. 암호 및 비선형 연산 분야에서 차세대 컴퓨팅으로 주목받는 양자컴퓨팅 분야에서는 전기및전자공학부 김상현 교수 연구팀이 3차원 집적 기술을 세계 최초로 선보였다. 신경계의 원리를 활용해 인공지능 분야에서 발군의 성능을 보일 것으로 기대되는 뉴로모픽 컴퓨팅에서는 전기및전자공학부 최신현 교수 연구팀이 신경세포를 모사하는 차세대 멤리스터를 개발 중이다.

인공지능 분야에서도 비약적으로 성장했다. 인공지능 분야의 양대 세계 최고 권위 학회인 국제머신러닝학회(ICML)과 인공신경망학회(NeurIPS) 논문 수 기준으로 KAIST는 2020년 세계 6위, 아시아에서는 1위를 기록했다. KAIST의 순위는 2012년부터 꾸준히 우상향 그래프를 그려 8년만에 37위에서 6위로, 무려 31계단이나 도약했다. 2021년에는 인공지능 분야 톱 학회 11개에 발표된 한국 논문 중 약 40%에 달하는 129편이 KAIST에서 나왔다. KAIST의 이러한 활약에 힘입어 2021년 한국은 글로벌 인공지능 톱 학회 등재 논문 수 기준으로 미국, 중국, 영국, 캐나다, 독일에 이어 6위에 올랐다.

내용 면에서도 KAIST의 인공지능 연구는 최전선에 있다. 전기및전자공학부 유회준 교수 연구팀은 모바일기기에서 인공지능 실시간 학습을 구현해 에지 네트워크의 단점을 보완했다. 인공지능을 구현하려면 데이터 축적관 막대한 양의 연산이 필요한데, 이를 위해 고성능 서버가 방대한 연산을 담당하고 사용자 단말은 데이터 수집과 간단한 연산만 하는 `에지 네트워크'가 사용된다. 유 교수의 연구는 사용자 단말에 학습 능력을 부여함으로써 인공지능의 처리 속도와 성능을 크게 높일 수 있다.

지난 6월에는 전산학부 김민수 교수 연구팀이 초대규모 인공지능 모델 처리에 꼭 필요한 솔루션을 제시했다. 연구팀이 개발한 초대규모 기계학습 시스템은 현재 업계에서 주로 사용되는 구글의 텐서플로우(Tensorflow)나 IBM의 시스템DS 대비 최대 8.8배나 빠른 속도를 달성할 수 있을 것으로 기대된다.

KAIST는 반도체와 인공지능이 결합된 AI 반도체 분야에서도 주목할만한 성과를 내고 있다. 2020년 전기및전자공학부 유민수 교수 연구팀은 세계 최초로 추천시스템에 최적화된 AI 반도체를 개발하는 데 성공했다. 인공지능 추천시스템은 방대한 콘텐츠와 사용자 정보를 다룬다는 특성상 범용 인공지능 시스템으로 운영하면 병목현상으로 성능에 한계가 있다. 유민수 교수팀은 `프로세싱-인-메모리(이하 PIM, Processing-In-Memory)' 기술을 기반으로 기존 시스템 대비 최대 21배 빠른 속도를 낼 수 있는 반도체를 개발했다. PIM은 처리할 데이터를 임시로 저장하기만 하던 `램'에서 연산까지 수행해 효율을 높이는 기술이다. PIM 기술이 본격적으로 상용화되면 메모리 분야에서 강세인 한국 기업의 AI 반도체 시장 경쟁력이 비약적으로 높아질 것으로 기대된다.

KAIST는 그간의 성과에 안주하지 않고 인공지능 및 반도체, 그리고 AI 반도체 분야 초격차를 유지하고자 다각적인 노력을 기울이고 있다. 1990년 국내 최초로 인공지능연구센터를 설립한 데 이어 2019년에는 김재철AI대학원을 개설해 전문인력을 양성 중이다. 2020년에는 인공지능과 반도체 연구를 융합해 ITRC 인공지능반도체시스템 연구센터가 출범했으며, 2021년에는 인공지능을 다양한 분야에 접목하는 `AI+X' 연구를 활성화하고자 김재철AI대학원과 별도로 AI 연구원을 설립했다.

KAIST는 이러한 노력으로 축적된 내적 역량을 바탕으로 네이버 등 기업과 공동연구센터를 설립하는 한편, 화성시와 같은 지자체와 협력해 동시다발적인 전문인력 양성에 나섰다. 지난 2021년에는 삼성전자와 함께 반도체시스템공학과 설립 협약을 체결하고 새로운 반도체 전문인력 교육과정을 준비하고 있다. 새로 설립되는 반도체시스템공학과는 2023년부터 매년 100명 내외의 신입생을 선발하고, 이들이 전문역량을 꽃피울 수 있도록 학생 전원에게 특별장학금을 지급할 예정이다. 또한 산업계와의 긴밀한 협력을 통해 삼성전자 견학과 인턴십, 공동 워크숍을 지원해 현장에 밀착한 교육을 제공할 예정이다.

KAIST는 국내 반도체 분야 박사 인력의 25%, 박사 출신 중견 및 벤처기업 CEO의 20%를 배출하며 한국 반도체 산업 생태계가 성장하는 데 중대한 공헌을 했다. 본격적으로 열린 AI 반도체 경쟁 체제를 앞두고 KAIST가 다시 산업 생태계의 구심점 역할을 할지 귀추가 주목된다.

2022.08.04 조회수 19023

KAIST, 인공지능 반도체 생태계를 선도하다

인공지능 반도체(이하 AI 반도체)가 국가적인 전략기술로 두드러지면서 KAIST의 관련 성과도 주목받고 있다. 과학기술정보통신부는 지난해 2030년 세계 AI 반도체 시장 20% 점유를 목표로 인공지능 반도체 지원사업에 본격적으로 착수한 바 있다. 올해에는 산학연 논의를 거쳐 5년간 1조 200억 원을 투입하는 `인공지능 반도체 산업 성장 지원대책'으로 지원을 확대했다. 이에 따라 AI 반도체 전문가 양성을 위해 주요 대학들의 행보도 분주해졌다.

KAIST는 반도체와 인공지능 양대 핵심 분야에서 최상급의 교육, 연구 역량을 쌓아 왔다. 반도체 분야에서는 지난 17년 동안 메사추세츠 공과대학(이하 MIT), 스탠퍼드(Stanford)와 같은 세계적인 학교를 제치고 국제반도체회로학회(이하 ISSCC, International Solid State Circuit Conference)에서 대학 중 1위를 지켜 왔다는 점이 돋보인다. ISSCC는 1954년 설립된 반도체 집적회로 설계 분야 세계 최고 권위 학회다. 참가자 중 60% 이상이 삼성, 퀄컴, TSMC, 인텔을 비롯한 산업계 소속일만큼 산업적인 실용성을 중시해서 `반도체 설계 올림픽'이라는 별명도 있다.

KAIST는 ISSCC에서 채택 논문 수 기준 매년 전 세계 대학교 중 1~2위를 유지했다. 최근 17년간 평균 채택 논문 수를 살펴보면 압도적인 선두다. 해당 기간 채택된 KAIST의 논문은 평균 8.4편으로, 경쟁자인 MIT(4.6편)와 캘리포니아대학교 로스앤젤레스(UCLA)(3.6편)에 비해 두 배 가까운 성과다. 국내에서는 반도체 설계 분야 부동의 1위인 삼성에 이어 종합 2위 자리를 유지하고 있다. 그럴 뿐만 아니라 ISSCC와 쌍벽을 이루는 집적회로 분야 학술대회인 초고밀도집적회로학회에서도 KAIST는 2022년 전 세계 대학 중 1위를 기록했다.

KAIST의 연구진들이 반도체 산업 핵심 분야 전반에서 신기술을 발표해 연구의 질적인 수준도 높다. 전기및전자공학부 정명수 교수 연구팀은 고성능 저전력을 추구하는 현재 업계의 수요에 대응해 전력 공급 없이도 동작을 유지하는 컴퓨터를 개발했다. 소재 분야에서는 신소재공학과의 박병국 교수 연구팀이 기존의 메모리에 비해 동작 속도가 10배 이상 빠른 `스핀궤도토크 자성메모리' 소자를 개발해서 기존 `폰노이만 구조'의 한계를 극복하는 방안을 제시하기도 했다.

이처럼 현재 반도체 산업의 주요 과제에 솔루션을 제공하는 한편으로 미래의 새로운 반도체 분야를 선점하는 데 필요한 신기술 개발도 활발하다. 암호 및 비선형 연산 분야에서 차세대 컴퓨팅으로 주목받는 양자컴퓨팅 분야에서는 전기및전자공학부 김상현 교수 연구팀이 3차원 집적 기술을 세계 최초로 선보였다. 신경계의 원리를 활용해 인공지능 분야에서 발군의 성능을 보일 것으로 기대되는 뉴로모픽 컴퓨팅에서는 전기및전자공학부 최신현 교수 연구팀이 신경세포를 모사하는 차세대 멤리스터를 개발 중이다.

인공지능 분야에서도 비약적으로 성장했다. 인공지능 분야의 양대 세계 최고 권위 학회인 국제머신러닝학회(ICML)과 인공신경망학회(NeurIPS) 논문 수 기준으로 KAIST는 2020년 세계 6위, 아시아에서는 1위를 기록했다. KAIST의 순위는 2012년부터 꾸준히 우상향 그래프를 그려 8년만에 37위에서 6위로, 무려 31계단이나 도약했다. 2021년에는 인공지능 분야 톱 학회 11개에 발표된 한국 논문 중 약 40%에 달하는 129편이 KAIST에서 나왔다. KAIST의 이러한 활약에 힘입어 2021년 한국은 글로벌 인공지능 톱 학회 등재 논문 수 기준으로 미국, 중국, 영국, 캐나다, 독일에 이어 6위에 올랐다.

내용 면에서도 KAIST의 인공지능 연구는 최전선에 있다. 전기및전자공학부 유회준 교수 연구팀은 모바일기기에서 인공지능 실시간 학습을 구현해 에지 네트워크의 단점을 보완했다. 인공지능을 구현하려면 데이터 축적관 막대한 양의 연산이 필요한데, 이를 위해 고성능 서버가 방대한 연산을 담당하고 사용자 단말은 데이터 수집과 간단한 연산만 하는 `에지 네트워크'가 사용된다. 유 교수의 연구는 사용자 단말에 학습 능력을 부여함으로써 인공지능의 처리 속도와 성능을 크게 높일 수 있다.

지난 6월에는 전산학부 김민수 교수 연구팀이 초대규모 인공지능 모델 처리에 꼭 필요한 솔루션을 제시했다. 연구팀이 개발한 초대규모 기계학습 시스템은 현재 업계에서 주로 사용되는 구글의 텐서플로우(Tensorflow)나 IBM의 시스템DS 대비 최대 8.8배나 빠른 속도를 달성할 수 있을 것으로 기대된다.

KAIST는 반도체와 인공지능이 결합된 AI 반도체 분야에서도 주목할만한 성과를 내고 있다. 2020년 전기및전자공학부 유민수 교수 연구팀은 세계 최초로 추천시스템에 최적화된 AI 반도체를 개발하는 데 성공했다. 인공지능 추천시스템은 방대한 콘텐츠와 사용자 정보를 다룬다는 특성상 범용 인공지능 시스템으로 운영하면 병목현상으로 성능에 한계가 있다. 유민수 교수팀은 `프로세싱-인-메모리(이하 PIM, Processing-In-Memory)' 기술을 기반으로 기존 시스템 대비 최대 21배 빠른 속도를 낼 수 있는 반도체를 개발했다. PIM은 처리할 데이터를 임시로 저장하기만 하던 `램'에서 연산까지 수행해 효율을 높이는 기술이다. PIM 기술이 본격적으로 상용화되면 메모리 분야에서 강세인 한국 기업의 AI 반도체 시장 경쟁력이 비약적으로 높아질 것으로 기대된다.

KAIST는 그간의 성과에 안주하지 않고 인공지능 및 반도체, 그리고 AI 반도체 분야 초격차를 유지하고자 다각적인 노력을 기울이고 있다. 1990년 국내 최초로 인공지능연구센터를 설립한 데 이어 2019년에는 김재철AI대학원을 개설해 전문인력을 양성 중이다. 2020년에는 인공지능과 반도체 연구를 융합해 ITRC 인공지능반도체시스템 연구센터가 출범했으며, 2021년에는 인공지능을 다양한 분야에 접목하는 `AI+X' 연구를 활성화하고자 김재철AI대학원과 별도로 AI 연구원을 설립했다.

KAIST는 이러한 노력으로 축적된 내적 역량을 바탕으로 네이버 등 기업과 공동연구센터를 설립하는 한편, 화성시와 같은 지자체와 협력해 동시다발적인 전문인력 양성에 나섰다. 지난 2021년에는 삼성전자와 함께 반도체시스템공학과 설립 협약을 체결하고 새로운 반도체 전문인력 교육과정을 준비하고 있다. 새로 설립되는 반도체시스템공학과는 2023년부터 매년 100명 내외의 신입생을 선발하고, 이들이 전문역량을 꽃피울 수 있도록 학생 전원에게 특별장학금을 지급할 예정이다. 또한 산업계와의 긴밀한 협력을 통해 삼성전자 견학과 인턴십, 공동 워크숍을 지원해 현장에 밀착한 교육을 제공할 예정이다.

KAIST는 국내 반도체 분야 박사 인력의 25%, 박사 출신 중견 및 벤처기업 CEO의 20%를 배출하며 한국 반도체 산업 생태계가 성장하는 데 중대한 공헌을 했다. 본격적으로 열린 AI 반도체 경쟁 체제를 앞두고 KAIST가 다시 산업 생태계의 구심점 역할을 할지 귀추가 주목된다.

2022.08.04 조회수 19023 -

무한대 화소 수준의 초고해상도 AR/VR 디스플레이 기술 개발

우리 대학 전기및전자공학부 김상현 교수 연구팀이 *모놀리식 3차원 집적의 장점을 활용한 1,600PPI*에 상응하는 마이크로LED 디스플레이를 구현하는 데 성공했다고 29일 밝혔다. 1,600 PPI는 초고해상도 증강현실(AR)/가상현실(VR) 디스플레이에 적용 가능한 해상도로써 2020년 출시된 오큘러스(Oculus) 社(現 메타(Meta))의 메타 퀘스트 2(Meta quest 2, 442 PPI)의 3.6배에 해당하는 디스플레이 해상도다.

☞ 모놀리식 3차원 집적: 하부 소자 공정 후, 상부의 박막층을 형성하고 상부 소자 공정을 순차적으로 진행함으로써 상하부 소자 간의 정렬도를 극대화할 수 있는 기술로 궁극적 3차원 집적 기술로 불린다.

☞ PPI: Pixel per Inch. 디스플레이에서 1인치에 포함되는 픽셀의 갯수

전기및전자공학부 박주혁 박사과정과 금대명 박사가 제1 저자로 주도하고 백우진 박사과정과 대만의 제스퍼 디스플레이(Jasper Display)의 존슨 쉬(Johnson Shieh) 박사와 협업으로 진행한 이번 연구는 반도체 올림픽이라 불리는 하와이 호놀롤루에서 열린 `VLSI 기술 & 회로 심포지엄 (2022 IEEE Symposium on VLSI Technology & Circuits)'에서 지난 6월 16일에 발표됐다. (논문명 : Monolithic 3D sequential integration realizing 1600-PPI red micro-LED display on Si CMOS driver IC)

VLSI 기술 심포지엄은 국제전자소자학회(International Electron Device Meetings, IEDM)와 더불어 대학 논문의 채택 비율이 25%가 되지 않는 저명한 반도체 소자 분야 최고 권위 학회다.

최근 디스플레이 분야는 각종 TV, 모니터 및 모바일 기기뿐만 아니라 스마트 워치, 스마트 글라스 등의 웨어러블 디바이스까지 그 응용처가 크게 확장됐다. 이처럼 디스플레이의 활용이 점차 다양화되고 고도화됨에 따라 요구되는 픽셀의 크기가 점점 작아지고 있는데, 특히 증강현실(AR)/가상현실(VR) 스마트 글라스 등과 같이 사람의 눈과 매우 가까운 거리를 유지하는 디스플레이의 경우 *픽셀화가 없는 완벽한 이미지의 구현을 위해서는 4K 이상의 고해상도가 요구된다.

☞ 픽셀화(Pixelation): 컴퓨터 그래픽에서 비트맵을 구성하는 작은 단색 정사각형 디스플레이 요소인 개별 픽셀이 보이는 현상.

앞서 언급한 초고해상도 디스플레이를 구현하기 위한 차세대 디스플레이 소자로서 무기물 기반의 인듐갈륨나이트라이드/갈륨나이트라이드(InGaN/GaN), 혹은 알루미늄 갈륨 인듐 인화물/갈륨 인듐 인화물(AlGaInP/GaInP)로 대표되는 3-5(III-V)족 화합물 반도체를 활용한 마이크로 LED 소자가 핵심 소재 및 부품으로써 주목받고 있다. 마이크로 LED는 현재 TV, 모바일 기기에 많이 사용되고 있는 OLED, LCD 디스플레이에 비해 높은 휘도와 명암비, 긴 픽셀 수명 등의 장점이 있어 차세대 디스플레이 소자로서 장점이 뚜렷하다.

☞ III-V 화합물 반도체: 주기율표 III족 원소와 V족 원소가 화합물을 이루고 있는 반도체로 전하 수송 특성 및 광 특성이 매우 우수한 소재.

하지만 무기물 기반 마이크로 LED를 활용해 디스플레이를 제작하기 위해서는 적색, 청색, 녹색의 각 색상의 픽셀을 각각의 기판에서 분리해 디스플레이 패널로 옮기는 패키징 작업이 필수적이다.

기존에 사용돼온 픽앤플레이스(Pick-and-place) 방법은 각각의 픽셀을 일일이 기계적으로 옮겨서 디스플레이 패널에 결합하는 방법으로 픽셀의 크기가 수십 마이크로미터 미만 수준으로 작아지게 되면 기계적인 정렬 정밀도가 저하되고 전사 수율이 감소해 초고해상도 디스플레이에는 적용이 어려울 것이라는 평가를 받고 있다.

연구팀은 이러한 문제의 해결을 위해 디스플레이 구동용 규소 상보적 금속산화물 반도체(이하 Si CMOS) 회로 기판 위에 적색 발광용 LED를 모놀리식 3차원 집적하는 방식을 적용했다. 위 방식은 Si CMOS 회로 위에 마이크로 LED 필름층을 먼저 웨이퍼 본딩을 통해 전사한 뒤, 포토리소그래피 공정으로 픽셀을 구현하는 방법으로, 기계적 픽셀 전사 공정이 제외된다. 이후 연구팀은 Si CMOS 회로상에서 상단에서 하단 방향으로(Top-down) 연속적인 반도체 공정 과정을 통해 고해상도 디스플레이 데모에 성공했다.

이 과정에서 연구팀은 조명용으로 활용돼왔던 무기물 기반 LED 반도체가 아닌 디스플레이용 LED 반도체층을 설계해 발광을 위한 활성층의 두께를 기존의 1/3로 감소시켜, 픽셀 형성에 필요한 식각 공정의 난도를 크게 낮추어 이번 연구성과를 얻어냈다.

또한, 연구팀은 하부 디스플레이 구동 회로의 성능 저하 방지를 위해 350oC 이하에서 상부 III-V 소자를 집적하는 웨이퍼 본딩 등의 초저온 공정을 활용해 상부 소자 집적 후에도 하부 드라이버 IC(Driver IC)의 성능을 그대로 유지할 수 있었다.

이번 연구 결과는 적색 마이크로 LED를 3차원 적층 방식으로 집적해 세계적인 수준의 해상도인 1,600 PPI 구현에 성공한 연구로서 연구에서 활용된 모놀리식 3차원 집적에 관한 연구 결과는 차세대 초고해상도 디스플레이 구현을 위한 좋은 가이드가 될 것으로 예상된다.

김상현 교수는 "향후 유사 공정을 확대 적용해 적색, 녹색, 청색이 모두 포함된 풀 컬러 디스플레이 제작도 가능할 것으로 생각한다ˮ라고 말했다.

한편 이번 연구는 삼성 미래기술육성센터의 지원을 받아 수행했다.

2022.07.29 조회수 11362

무한대 화소 수준의 초고해상도 AR/VR 디스플레이 기술 개발

우리 대학 전기및전자공학부 김상현 교수 연구팀이 *모놀리식 3차원 집적의 장점을 활용한 1,600PPI*에 상응하는 마이크로LED 디스플레이를 구현하는 데 성공했다고 29일 밝혔다. 1,600 PPI는 초고해상도 증강현실(AR)/가상현실(VR) 디스플레이에 적용 가능한 해상도로써 2020년 출시된 오큘러스(Oculus) 社(現 메타(Meta))의 메타 퀘스트 2(Meta quest 2, 442 PPI)의 3.6배에 해당하는 디스플레이 해상도다.

☞ 모놀리식 3차원 집적: 하부 소자 공정 후, 상부의 박막층을 형성하고 상부 소자 공정을 순차적으로 진행함으로써 상하부 소자 간의 정렬도를 극대화할 수 있는 기술로 궁극적 3차원 집적 기술로 불린다.

☞ PPI: Pixel per Inch. 디스플레이에서 1인치에 포함되는 픽셀의 갯수

전기및전자공학부 박주혁 박사과정과 금대명 박사가 제1 저자로 주도하고 백우진 박사과정과 대만의 제스퍼 디스플레이(Jasper Display)의 존슨 쉬(Johnson Shieh) 박사와 협업으로 진행한 이번 연구는 반도체 올림픽이라 불리는 하와이 호놀롤루에서 열린 `VLSI 기술 & 회로 심포지엄 (2022 IEEE Symposium on VLSI Technology & Circuits)'에서 지난 6월 16일에 발표됐다. (논문명 : Monolithic 3D sequential integration realizing 1600-PPI red micro-LED display on Si CMOS driver IC)

VLSI 기술 심포지엄은 국제전자소자학회(International Electron Device Meetings, IEDM)와 더불어 대학 논문의 채택 비율이 25%가 되지 않는 저명한 반도체 소자 분야 최고 권위 학회다.

최근 디스플레이 분야는 각종 TV, 모니터 및 모바일 기기뿐만 아니라 스마트 워치, 스마트 글라스 등의 웨어러블 디바이스까지 그 응용처가 크게 확장됐다. 이처럼 디스플레이의 활용이 점차 다양화되고 고도화됨에 따라 요구되는 픽셀의 크기가 점점 작아지고 있는데, 특히 증강현실(AR)/가상현실(VR) 스마트 글라스 등과 같이 사람의 눈과 매우 가까운 거리를 유지하는 디스플레이의 경우 *픽셀화가 없는 완벽한 이미지의 구현을 위해서는 4K 이상의 고해상도가 요구된다.

☞ 픽셀화(Pixelation): 컴퓨터 그래픽에서 비트맵을 구성하는 작은 단색 정사각형 디스플레이 요소인 개별 픽셀이 보이는 현상.

앞서 언급한 초고해상도 디스플레이를 구현하기 위한 차세대 디스플레이 소자로서 무기물 기반의 인듐갈륨나이트라이드/갈륨나이트라이드(InGaN/GaN), 혹은 알루미늄 갈륨 인듐 인화물/갈륨 인듐 인화물(AlGaInP/GaInP)로 대표되는 3-5(III-V)족 화합물 반도체를 활용한 마이크로 LED 소자가 핵심 소재 및 부품으로써 주목받고 있다. 마이크로 LED는 현재 TV, 모바일 기기에 많이 사용되고 있는 OLED, LCD 디스플레이에 비해 높은 휘도와 명암비, 긴 픽셀 수명 등의 장점이 있어 차세대 디스플레이 소자로서 장점이 뚜렷하다.

☞ III-V 화합물 반도체: 주기율표 III족 원소와 V족 원소가 화합물을 이루고 있는 반도체로 전하 수송 특성 및 광 특성이 매우 우수한 소재.

하지만 무기물 기반 마이크로 LED를 활용해 디스플레이를 제작하기 위해서는 적색, 청색, 녹색의 각 색상의 픽셀을 각각의 기판에서 분리해 디스플레이 패널로 옮기는 패키징 작업이 필수적이다.

기존에 사용돼온 픽앤플레이스(Pick-and-place) 방법은 각각의 픽셀을 일일이 기계적으로 옮겨서 디스플레이 패널에 결합하는 방법으로 픽셀의 크기가 수십 마이크로미터 미만 수준으로 작아지게 되면 기계적인 정렬 정밀도가 저하되고 전사 수율이 감소해 초고해상도 디스플레이에는 적용이 어려울 것이라는 평가를 받고 있다.

연구팀은 이러한 문제의 해결을 위해 디스플레이 구동용 규소 상보적 금속산화물 반도체(이하 Si CMOS) 회로 기판 위에 적색 발광용 LED를 모놀리식 3차원 집적하는 방식을 적용했다. 위 방식은 Si CMOS 회로 위에 마이크로 LED 필름층을 먼저 웨이퍼 본딩을 통해 전사한 뒤, 포토리소그래피 공정으로 픽셀을 구현하는 방법으로, 기계적 픽셀 전사 공정이 제외된다. 이후 연구팀은 Si CMOS 회로상에서 상단에서 하단 방향으로(Top-down) 연속적인 반도체 공정 과정을 통해 고해상도 디스플레이 데모에 성공했다.

이 과정에서 연구팀은 조명용으로 활용돼왔던 무기물 기반 LED 반도체가 아닌 디스플레이용 LED 반도체층을 설계해 발광을 위한 활성층의 두께를 기존의 1/3로 감소시켜, 픽셀 형성에 필요한 식각 공정의 난도를 크게 낮추어 이번 연구성과를 얻어냈다.

또한, 연구팀은 하부 디스플레이 구동 회로의 성능 저하 방지를 위해 350oC 이하에서 상부 III-V 소자를 집적하는 웨이퍼 본딩 등의 초저온 공정을 활용해 상부 소자 집적 후에도 하부 드라이버 IC(Driver IC)의 성능을 그대로 유지할 수 있었다.

이번 연구 결과는 적색 마이크로 LED를 3차원 적층 방식으로 집적해 세계적인 수준의 해상도인 1,600 PPI 구현에 성공한 연구로서 연구에서 활용된 모놀리식 3차원 집적에 관한 연구 결과는 차세대 초고해상도 디스플레이 구현을 위한 좋은 가이드가 될 것으로 예상된다.

김상현 교수는 "향후 유사 공정을 확대 적용해 적색, 녹색, 청색이 모두 포함된 풀 컬러 디스플레이 제작도 가능할 것으로 생각한다ˮ라고 말했다.

한편 이번 연구는 삼성 미래기술육성센터의 지원을 받아 수행했다.

2022.07.29 조회수 11362 -

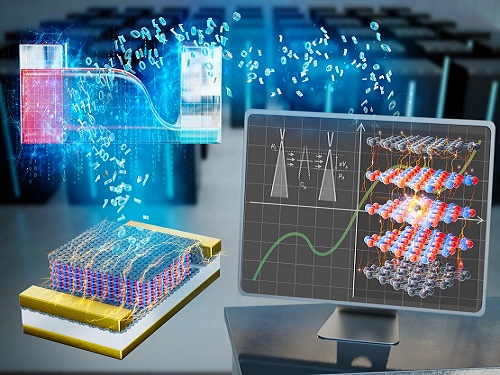

고정확도 실시간 학습 가능한 모바일 인공지능 반도체 칩 세계 최초 개발

우리 대학 전기및전자공학부 유회준 교수 연구팀이 인공지능의 실시간 학습을 모바일 기기에서 구현, 고정확도 인공지능(AI: Artificial Intelligent) 반도체*를 세계 최초로 개발했다고 23일 밝혔다.

* 인공지능 반도체 : 인식·추론·학습·판단 등 인공지능 처리 기능을 탑재하고, 초지능·초저전력·초신뢰 기반의 최적화된 기술로 구현한 반도체

연구팀이 개발한 인공지능 반도체는 저비트 학습과 저지연 학습 방식을 적용해, 모바일 기기에서도 학습할 수 있다. 특히 이번 반도체 칩은 인공지능의 예상치 못한 성능 저하를 막을 수 있는 실시간 학습 기술을 성공적으로 구현했다.

전기및전자공학부 한동현 박사과정이 제1 저자로 참여한 이번 연구는 지난 6월 12일부터 15일까지 인천 연수구 송도 컨벤시아에서 개최된 국제 인공지능 회로 및 시스템 학술대회(AICAS)에서 발표됐으며 응용 예시를 현장에서 시연했고, 최우수 논문상과 최우수 데모상을 모두 석권해 그 우수성을 널리 알렸다. (논문명 : A 0.95 mJ/frame DNN Training Processor for Robust Object Detection with Real-World Environmental Adaptation (저자: 한동현, 임동석, 박광태, 김영우, 송석찬, 이주형, 유회준))

인공지능 (AI) 반도체 기술을 망라하는 국제 학술 대회 ‘AICAS 2022’는 인공지능 반도체 분야 세계 최고 권위를 가진 IEEE(미국 전기 전자 기술자 협회)학회로 평가받으며, 삼성, SK를 필두로, 한국전자통신연구원(ETRI), 엔비디아(NVIDIA), 케이던스(Cadence) 등 국내외 저명한 기업과 기관 등이 참석해 인공지능 반도체 회로와 시스템 전 분야, 인공지능 반도체와 관련된 연구성과를 공유하는 행사다.

기존 인공지능은 사전에 학습된 지능만으로 추론을 진행했기 때문에 학습하지 않은 새로운 환경 혹은 물체에 대해서는 물체 검출이 어려웠다. 하지만 유회준 교수 연구팀이 개발한 실시간 학습은 추론만 수행하던 기존 모바일 인공지능 반도체에 학습 기능을 부여함으로써, 인공지능의 지능 수준을 크게 끌어올렸다.

유 교수팀의 새로운 인공지능 반도체는 사전에 학습한 지식과 애플리케이션 수행 중에 학습한 지식을 함께 활용해 고정확도 물체검출 성능을 보였다. 특히 유회준 교수 연구팀은 렌즈가 깨지거나, 기계 오류로 인한 인공지능의 예상치 못한 정확도 감소도 자동으로 인지하고 이를 실시간 학습을 통해 보정, 기존 인공지능의 문제점을 해결했다.

유 교수팀은 실시간 학습 기능에 더해, 모바일 기기에서 저전력으로 학습이 가능할 수 있도록, 저비트 인공지능 학습 방법, 직접 오류 전사 기반 저지연 학습 방식을 제안, 이를 최적화할 수 있는 반도체(HNPU) 와 응용 시스템을 모두 개발했다.

저전력, 실시간 학습을 수행할 수 있는 모바일 인공지능 전용 반도체, HNPU는 다음과 같이 6가지 핵심 기술이 도입됐다.

○ 확률적 동적 고정 소수점 활용 저비트 학습 방식 (SDFXP: Stochastic Dynamic Fixed-point Representation)

- 동적 고정 소수점에 확률적 표현을 결합하고 확률적 반올림을 도입하여 인공지능 학습에 필요한 비트 정밀도를 최소화 할 수 있는 방법

○ 레이어별 자동 정밀도 검색 알고리즘 및 하드웨어 (LAPS: Layer-wise Adaptive Precision Scaling)

- 학습의 난이도를 자동으로 파악하고 심층신경망의 레이어별로 최적의 비트수를 자동으로 찾아주는 알고리즘 및 이를 가속하는 하드웨어

○ 입력 비트 슬라이스 희소성 활용* (ISS: Input Slice Skipping or Bit-slice Level Sparsity Exploitation)

- 데이터를 이진수로 표현했을 때 중간중간 나타나는 ‘0’ 비트를 활용하여, 데이터 처리량을 높이는 방식

○ 내재적 순수 난수 생성기 (iTRNG: Intrinsic True Random Number Generator)

인공지능 연산을 활용한 순수 난수 생성기를 설계, 데이터의 암호화 및 확률적 반올림을 구현

○ 다중 학습 단계 할당을 통한 고속 학습 알고리즘 및 하드웨어 (MLTA: Multi Learning Task Allocation & Backward Unlocking)

기존 역전파 (Back-propagation) 알고리즘에서 탈피해, 직접 오류 전사를 통한 저지연 학습 구현

○ 실시간 인공지능 학습 기반 자동 오류 검출 기능 저하 보정 시스템 개발 (Real-time DNN Training based Automatic Performance Monitor and Performance Recovery System)

평상시 물체 검출 결과를 주기적으로 모니터링하면서, 갑작스러운 확률 변화를 자동으로 인식, 정확도 저하를 보정하기 위해 실시간 학습을 적용

* 희소성 활용 (Sparsity Exploitation) : 심층 신경망 모델의 연산은 수많은 곱셈누적(MAC: Multiply-And-Accumulate)연산의 연속이다. 연산자에 0이 존재할 시, 굳이 연산을 해보지 않아도 결과는 0임을 알기에 이를 뛰어넘는 방식으로 연산 속도를 높이는 방식.

이러한 기술을 사용해 HNPU는 저전력 물체검출을 구현하여, 다른 모바일 물체검출 시스템과 비교해 75% 높은 속도, 44% 낮은 에너지 소모를 달성하면서도, 실시간 학습으로 고정확도 물체검출을 개발해 주목을 받았다.

연구팀은 HNPU의 활용 예시로 카메라 렌즈가 깨지거나, 기계 오류, 조명, 밝기 변화로 인공지능의 추론 능력이 떨어졌을 때, 실시간 학습을 통해 다시 정확도를 높이는 고정확도 물체검출 시스템을 개발했다. 이는 이후 자율 주행, 로봇 등 다양한 곳에 활용될 것으로 기대된다.

특히 연구팀의 HNPU 연구는 2022 국제인공지능회로및시스템학술대회(AICAS 2022)에서 발표돼, 최우수 논문상과 최우수 데모상을 모두 석권하여 그 우수성을 널리 알렸다.

연구를 주도한 KAIST 전기및전자공학부 유회준 교수는 “현재 인공지능은 사전에 학습한 지식만으로 주어진 문제를 해결하고 있으며, 이는 변화하는 환경과 상황에 맞춰 계속 학습하는 인간의 지능과 뚜렷한 차이를 보인다”라며 “이번 연구는 실시간 학습 인공지능 반도체를 통해 인공지능의 지능 수준을 사람 수준으로 한층 더 끌어올리는 연구”라고 본 연구의 의의를 밝혔다.

2022.06.23 조회수 9951

고정확도 실시간 학습 가능한 모바일 인공지능 반도체 칩 세계 최초 개발

우리 대학 전기및전자공학부 유회준 교수 연구팀이 인공지능의 실시간 학습을 모바일 기기에서 구현, 고정확도 인공지능(AI: Artificial Intelligent) 반도체*를 세계 최초로 개발했다고 23일 밝혔다.

* 인공지능 반도체 : 인식·추론·학습·판단 등 인공지능 처리 기능을 탑재하고, 초지능·초저전력·초신뢰 기반의 최적화된 기술로 구현한 반도체

연구팀이 개발한 인공지능 반도체는 저비트 학습과 저지연 학습 방식을 적용해, 모바일 기기에서도 학습할 수 있다. 특히 이번 반도체 칩은 인공지능의 예상치 못한 성능 저하를 막을 수 있는 실시간 학습 기술을 성공적으로 구현했다.

전기및전자공학부 한동현 박사과정이 제1 저자로 참여한 이번 연구는 지난 6월 12일부터 15일까지 인천 연수구 송도 컨벤시아에서 개최된 국제 인공지능 회로 및 시스템 학술대회(AICAS)에서 발표됐으며 응용 예시를 현장에서 시연했고, 최우수 논문상과 최우수 데모상을 모두 석권해 그 우수성을 널리 알렸다. (논문명 : A 0.95 mJ/frame DNN Training Processor for Robust Object Detection with Real-World Environmental Adaptation (저자: 한동현, 임동석, 박광태, 김영우, 송석찬, 이주형, 유회준))

인공지능 (AI) 반도체 기술을 망라하는 국제 학술 대회 ‘AICAS 2022’는 인공지능 반도체 분야 세계 최고 권위를 가진 IEEE(미국 전기 전자 기술자 협회)학회로 평가받으며, 삼성, SK를 필두로, 한국전자통신연구원(ETRI), 엔비디아(NVIDIA), 케이던스(Cadence) 등 국내외 저명한 기업과 기관 등이 참석해 인공지능 반도체 회로와 시스템 전 분야, 인공지능 반도체와 관련된 연구성과를 공유하는 행사다.

기존 인공지능은 사전에 학습된 지능만으로 추론을 진행했기 때문에 학습하지 않은 새로운 환경 혹은 물체에 대해서는 물체 검출이 어려웠다. 하지만 유회준 교수 연구팀이 개발한 실시간 학습은 추론만 수행하던 기존 모바일 인공지능 반도체에 학습 기능을 부여함으로써, 인공지능의 지능 수준을 크게 끌어올렸다.

유 교수팀의 새로운 인공지능 반도체는 사전에 학습한 지식과 애플리케이션 수행 중에 학습한 지식을 함께 활용해 고정확도 물체검출 성능을 보였다. 특히 유회준 교수 연구팀은 렌즈가 깨지거나, 기계 오류로 인한 인공지능의 예상치 못한 정확도 감소도 자동으로 인지하고 이를 실시간 학습을 통해 보정, 기존 인공지능의 문제점을 해결했다.

유 교수팀은 실시간 학습 기능에 더해, 모바일 기기에서 저전력으로 학습이 가능할 수 있도록, 저비트 인공지능 학습 방법, 직접 오류 전사 기반 저지연 학습 방식을 제안, 이를 최적화할 수 있는 반도체(HNPU) 와 응용 시스템을 모두 개발했다.

저전력, 실시간 학습을 수행할 수 있는 모바일 인공지능 전용 반도체, HNPU는 다음과 같이 6가지 핵심 기술이 도입됐다.

○ 확률적 동적 고정 소수점 활용 저비트 학습 방식 (SDFXP: Stochastic Dynamic Fixed-point Representation)

- 동적 고정 소수점에 확률적 표현을 결합하고 확률적 반올림을 도입하여 인공지능 학습에 필요한 비트 정밀도를 최소화 할 수 있는 방법

○ 레이어별 자동 정밀도 검색 알고리즘 및 하드웨어 (LAPS: Layer-wise Adaptive Precision Scaling)

- 학습의 난이도를 자동으로 파악하고 심층신경망의 레이어별로 최적의 비트수를 자동으로 찾아주는 알고리즘 및 이를 가속하는 하드웨어

○ 입력 비트 슬라이스 희소성 활용* (ISS: Input Slice Skipping or Bit-slice Level Sparsity Exploitation)

- 데이터를 이진수로 표현했을 때 중간중간 나타나는 ‘0’ 비트를 활용하여, 데이터 처리량을 높이는 방식

○ 내재적 순수 난수 생성기 (iTRNG: Intrinsic True Random Number Generator)

인공지능 연산을 활용한 순수 난수 생성기를 설계, 데이터의 암호화 및 확률적 반올림을 구현

○ 다중 학습 단계 할당을 통한 고속 학습 알고리즘 및 하드웨어 (MLTA: Multi Learning Task Allocation & Backward Unlocking)

기존 역전파 (Back-propagation) 알고리즘에서 탈피해, 직접 오류 전사를 통한 저지연 학습 구현

○ 실시간 인공지능 학습 기반 자동 오류 검출 기능 저하 보정 시스템 개발 (Real-time DNN Training based Automatic Performance Monitor and Performance Recovery System)

평상시 물체 검출 결과를 주기적으로 모니터링하면서, 갑작스러운 확률 변화를 자동으로 인식, 정확도 저하를 보정하기 위해 실시간 학습을 적용

* 희소성 활용 (Sparsity Exploitation) : 심층 신경망 모델의 연산은 수많은 곱셈누적(MAC: Multiply-And-Accumulate)연산의 연속이다. 연산자에 0이 존재할 시, 굳이 연산을 해보지 않아도 결과는 0임을 알기에 이를 뛰어넘는 방식으로 연산 속도를 높이는 방식.

이러한 기술을 사용해 HNPU는 저전력 물체검출을 구현하여, 다른 모바일 물체검출 시스템과 비교해 75% 높은 속도, 44% 낮은 에너지 소모를 달성하면서도, 실시간 학습으로 고정확도 물체검출을 개발해 주목을 받았다.

연구팀은 HNPU의 활용 예시로 카메라 렌즈가 깨지거나, 기계 오류, 조명, 밝기 변화로 인공지능의 추론 능력이 떨어졌을 때, 실시간 학습을 통해 다시 정확도를 높이는 고정확도 물체검출 시스템을 개발했다. 이는 이후 자율 주행, 로봇 등 다양한 곳에 활용될 것으로 기대된다.

특히 연구팀의 HNPU 연구는 2022 국제인공지능회로및시스템학술대회(AICAS 2022)에서 발표돼, 최우수 논문상과 최우수 데모상을 모두 석권하여 그 우수성을 널리 알렸다.

연구를 주도한 KAIST 전기및전자공학부 유회준 교수는 “현재 인공지능은 사전에 학습한 지식만으로 주어진 문제를 해결하고 있으며, 이는 변화하는 환경과 상황에 맞춰 계속 학습하는 인간의 지능과 뚜렷한 차이를 보인다”라며 “이번 연구는 실시간 학습 인공지능 반도체를 통해 인공지능의 지능 수준을 사람 수준으로 한층 더 끌어올리는 연구”라고 본 연구의 의의를 밝혔다.

2022.06.23 조회수 9951 -

차세대 반도체 나노구조 공정을 혁신하는 새로운 3차원 노광 공정 개발

우리 대학 신소재공학과 전석우 교수와 신종화 교수 공동연구팀이 차세대 반도체 공정 핵심기술인 3차원의 나노구조를 단일 노광으로 효율적으로 제작하는 방법을 개발했다고 27일 밝혔다. 노광 공정이란 빛을 이용해 실리콘 웨이퍼에 전자 회로를 새기는 공정을 말한다.

이번 연구 성과는 갈수록 복잡해지는 반도체 구조와 배선구조 등을 기존 2차원 평면 노광 방식으로 건물을 한층 한층 제작하듯이 진행하던 방식에 비해 훨씬 더 낮은 비용과 공정으로 제작할 수 있는 근거를 마련한 획기적인 연구 결과로 판단된다.

전석우 교수와 신종화 교수가 교신 저자로, 남상현 박사와 김명준, 김나영 박사과정이 공동 제1 저자로 참여한 이번 연구는 저명한 국제 학술지 `사이언스 어드밴시스(Science Advances)' 5월 25일 字 온라인판에 게재됐다. (논문명: Photolithographic Realization of Target Nanostructures in 3D Space by Inverse Design of Phase Modulation)

공동연구팀은 수반행렬 방법(Adjoint method) 기반 역설계 알고리즘을 활용해, 적은 연산으로 원하는 형태의 나노 홀로그램을 생성하는 위상 마스크의 격자구조를 효율적으로 찾아내는 방법론을 제시했다. 이는 기존의 반도체 리소그래피 공정에 적용됐으며, 연구팀은 광감응성 물질에 단 한 번의 빛을 쏘아 목표하는 나노 홀로그램을 형성하고, 물질화해 원하는 3차원 나노구조를 단 한 번의 노광으로 구현할 수 있음을 실험적으로 증명했다.

최근 리소그래피 및 패터닝 기술의 발달로 소재의 형상을 나노스케일에서 구현하는 기술이 발달함에 따라 기존 소재의 물성을 극복하는 메타 소재 및 3차원 프린팅 연구가 주목받고 있다. 특히 3차원 나노소재를 구현하기 위해 활용되는 기존 공정들은 구현하는 구조의 자유도, 생산성, 정밀도를 모두 만족하기 어려운 점이 있어 이를 개선하기 위한 다양한 시도가 진행 중이다.

다양한 3차원 패터닝 공정 가운데, 근접장 나노패터닝(PnP, Proximity-field nanoPatterning)은 단일 노광으로 주기적인 3차원의 나노구조를 정확하고 생산성 있게 구현할 수 있다. 하지만, 현재까지 주기적인 위상 마스크 패턴을 활용해 구현할 수 있는 구조의 자유도는 제한돼왔으며, 이를 극복하기 위해서는 감광물질에 원하는 형태의 홀로그램을 구현하는 위상 마스크의 디자인을 계산하는 과정이 필요하다.

기존 연구에서는 유전 알고리즘(Genetic Algorithm)을 통해 이러한 역계산을 수행했으나, 비효율적인 계산방식, 많은 계산량 등의 문제로 활용이 제한된다. 최근 주목받는 머신러닝도 학습을 위한 데이터양이 최소 수천 개 이상으로 많이 요구돼 현실적으로 이를 역계산에 활용하기에는 아직 요원한 상황이다.

연구팀은 수학적 방법론인 수반행렬 방법(Adjoint Method) 기반 알고리즘을 위상 마스크의 패턴이 빛과 상호작용하는 광학현상에 적용해, 원하는 홀로그램 형상을 광감응성 소재에 효율적으로 계산해 그 형상을 얻어내는 데 성공했다. 이 알고리즘은 수식으로 표현된 목표 디자인을 최소한의 계산 경로로 찾아내는 알고리즘이며, 행렬 연산을 활용해 많은 계산량을 효율적으로 처리한다는 장점이 있다. 기존의 단순한 주기적 위상 마스크 패턴은 수직 입사하는 빛으로 특정 배열의 나노구조만을 발생시켰다. 연구팀은 해당 연구에서 위상 마스크에 반도체 공정에 적용 가능한 수직 입사 빔 방식으로 기존의 마스크로 얻어내는 것이 불가능했던 새로운 배열의 3차원 나노구조를 얻어내는 데 성공했다. 이번 연구는 이를 통해 기존의 반도체 노광공정이 갖는 자유도의 한계를 극복하고 더 나아가 보다 복잡한 나노구조를 구현할 수 있다는 것을 이론적, 실험적으로 증명한 주요 연구라 할 수 있다.

이렇게 제작된 3차원의 나노구조는 원자층 증착법을 활용해 구조에 따라 물질의 주입 및 치환으로 다양한 소재를 원하는 구조로 제작할 가능성을 열어준다. 이번 기술이 차세대 반도체 소자인 GAA(Gate All Around) 소자나 3차원 반도체 집적기술에 적용된다면 현재 국가적으로 많은 노력을 기울이고 있는 차세대 반도체 역량 강화에 크게 이바지할 것으로 기대된다. 더 나아가 소재의 물성이 소재를 구성하는 원자나 결합이 아닌 순수한 나노구조에서 기인하는 새로운 물성을 확보하는 메타 소재 연구에서 원하는 나노구조를 낮은 비용으로 대면적에 생산함으로 국내의 소재 경쟁력을 크게 강화할 원천기술이 될 것이다.

이번 연구는 한국연구재단 원천기술개발사업의 미래소재디스커버리 사업과(NRF-2020M3D1A1110522) 삼성전자의(G01190420) 지원을 통해 수행됐다.

2022.05.27 조회수 10860

차세대 반도체 나노구조 공정을 혁신하는 새로운 3차원 노광 공정 개발

우리 대학 신소재공학과 전석우 교수와 신종화 교수 공동연구팀이 차세대 반도체 공정 핵심기술인 3차원의 나노구조를 단일 노광으로 효율적으로 제작하는 방법을 개발했다고 27일 밝혔다. 노광 공정이란 빛을 이용해 실리콘 웨이퍼에 전자 회로를 새기는 공정을 말한다.

이번 연구 성과는 갈수록 복잡해지는 반도체 구조와 배선구조 등을 기존 2차원 평면 노광 방식으로 건물을 한층 한층 제작하듯이 진행하던 방식에 비해 훨씬 더 낮은 비용과 공정으로 제작할 수 있는 근거를 마련한 획기적인 연구 결과로 판단된다.

전석우 교수와 신종화 교수가 교신 저자로, 남상현 박사와 김명준, 김나영 박사과정이 공동 제1 저자로 참여한 이번 연구는 저명한 국제 학술지 `사이언스 어드밴시스(Science Advances)' 5월 25일 字 온라인판에 게재됐다. (논문명: Photolithographic Realization of Target Nanostructures in 3D Space by Inverse Design of Phase Modulation)

공동연구팀은 수반행렬 방법(Adjoint method) 기반 역설계 알고리즘을 활용해, 적은 연산으로 원하는 형태의 나노 홀로그램을 생성하는 위상 마스크의 격자구조를 효율적으로 찾아내는 방법론을 제시했다. 이는 기존의 반도체 리소그래피 공정에 적용됐으며, 연구팀은 광감응성 물질에 단 한 번의 빛을 쏘아 목표하는 나노 홀로그램을 형성하고, 물질화해 원하는 3차원 나노구조를 단 한 번의 노광으로 구현할 수 있음을 실험적으로 증명했다.

최근 리소그래피 및 패터닝 기술의 발달로 소재의 형상을 나노스케일에서 구현하는 기술이 발달함에 따라 기존 소재의 물성을 극복하는 메타 소재 및 3차원 프린팅 연구가 주목받고 있다. 특히 3차원 나노소재를 구현하기 위해 활용되는 기존 공정들은 구현하는 구조의 자유도, 생산성, 정밀도를 모두 만족하기 어려운 점이 있어 이를 개선하기 위한 다양한 시도가 진행 중이다.

다양한 3차원 패터닝 공정 가운데, 근접장 나노패터닝(PnP, Proximity-field nanoPatterning)은 단일 노광으로 주기적인 3차원의 나노구조를 정확하고 생산성 있게 구현할 수 있다. 하지만, 현재까지 주기적인 위상 마스크 패턴을 활용해 구현할 수 있는 구조의 자유도는 제한돼왔으며, 이를 극복하기 위해서는 감광물질에 원하는 형태의 홀로그램을 구현하는 위상 마스크의 디자인을 계산하는 과정이 필요하다.

기존 연구에서는 유전 알고리즘(Genetic Algorithm)을 통해 이러한 역계산을 수행했으나, 비효율적인 계산방식, 많은 계산량 등의 문제로 활용이 제한된다. 최근 주목받는 머신러닝도 학습을 위한 데이터양이 최소 수천 개 이상으로 많이 요구돼 현실적으로 이를 역계산에 활용하기에는 아직 요원한 상황이다.

연구팀은 수학적 방법론인 수반행렬 방법(Adjoint Method) 기반 알고리즘을 위상 마스크의 패턴이 빛과 상호작용하는 광학현상에 적용해, 원하는 홀로그램 형상을 광감응성 소재에 효율적으로 계산해 그 형상을 얻어내는 데 성공했다. 이 알고리즘은 수식으로 표현된 목표 디자인을 최소한의 계산 경로로 찾아내는 알고리즘이며, 행렬 연산을 활용해 많은 계산량을 효율적으로 처리한다는 장점이 있다. 기존의 단순한 주기적 위상 마스크 패턴은 수직 입사하는 빛으로 특정 배열의 나노구조만을 발생시켰다. 연구팀은 해당 연구에서 위상 마스크에 반도체 공정에 적용 가능한 수직 입사 빔 방식으로 기존의 마스크로 얻어내는 것이 불가능했던 새로운 배열의 3차원 나노구조를 얻어내는 데 성공했다. 이번 연구는 이를 통해 기존의 반도체 노광공정이 갖는 자유도의 한계를 극복하고 더 나아가 보다 복잡한 나노구조를 구현할 수 있다는 것을 이론적, 실험적으로 증명한 주요 연구라 할 수 있다.

이렇게 제작된 3차원의 나노구조는 원자층 증착법을 활용해 구조에 따라 물질의 주입 및 치환으로 다양한 소재를 원하는 구조로 제작할 가능성을 열어준다. 이번 기술이 차세대 반도체 소자인 GAA(Gate All Around) 소자나 3차원 반도체 집적기술에 적용된다면 현재 국가적으로 많은 노력을 기울이고 있는 차세대 반도체 역량 강화에 크게 이바지할 것으로 기대된다. 더 나아가 소재의 물성이 소재를 구성하는 원자나 결합이 아닌 순수한 나노구조에서 기인하는 새로운 물성을 확보하는 메타 소재 연구에서 원하는 나노구조를 낮은 비용으로 대면적에 생산함으로 국내의 소재 경쟁력을 크게 강화할 원천기술이 될 것이다.

이번 연구는 한국연구재단 원천기술개발사업의 미래소재디스커버리 사업과(NRF-2020M3D1A1110522) 삼성전자의(G01190420) 지원을 통해 수행됐다.

2022.05.27 조회수 10860 -

그래핀 기반 2차원 반도체 소자 시뮬레이션의 양자 도약 달성

반도체 연구 개발에서 소자의 미세화에 따라 원자 수준에서 전류의 흐름을 이해하고 제어하는 것이 핵심적 요소가 되고 있는 상황에서, 우리 연구진이 기존에는 불가능했던 원자만큼 얇은 2차원 반도체 소자의 엄밀한 양자 역학적 컴퓨터 시뮬레이션을 성공적으로 구현하고 이를 기반으로 원자 결함에 의해 발생하는 특이한 소자 특성을 세계 최초로 보고했다.

우리 대학 전기및전자공학부 김용훈 교수 연구팀이 자체적으로 개발한 양자 수송 이론을 통해 세계 최초로 그래핀 전극 간 전자의 터널링 현상(전자가 포텐셜 장벽을 투과하는 현상)으로 작동하는 *2차원 터널링 트랜지스터의 **제1 원리 시뮬레이션을 수행하는 데 성공했다고 4일 밝혔다.

* 2차원 터널링 트랜지스터: 그래핀을 전극으로 하여 전극 간 전자의 터널링(tunneling) 현상을 통해 소자가 작동하는 반도체 소자이다. 소자의 동작 특성을 결정하는 그래핀 전극간 전자의 터널링 현상은 소스-드레인(source-drain) 전극 및 게이트(gate) 전압에 의해 결정된다.

**제1 원리 시뮬레이션: 제1원리 계산은 물질 내 전자들의 거동을 해석할 때 실험적 데이터나 경험적 모델을 도입하지 않고 지배방정식인 슈뢰딩거 방정식을 원자 정보를 포함시켜 직접 푸는 양자역학적 물질 시뮬레이션 방법으로 대표적인 방법론은 밀도 범함수론(density functional theory, DFT)이 있음

전기및전자공학부 김태형 박사과정과 이주호 박사가 공동 제1 저자로 참여한 이번 연구는 소재 계산 분야의 권위 있는 학술지 `네이쳐 파트너 저널 컴퓨테이셔널 머터리얼즈(Npj Computational Materials)' (IF 13.20) 3월 25일 字 온라인판에 게재됐다. (논문명: Gate-versus defect-induced voltage drop and negative differential resistance in vertical graphene heterostructures)

제1 원리 시뮬레이션이란 슈퍼컴퓨터에서 원자 수준의 양자역학 계산을 수행해 실험적 데이터나 경험적 모델의 도움 없이 물질의 특성을 도출하는 방법으로 제1 원리 계산을 통한 평형 상태의 소재 연구는 1998년 월터 콘(Walter Khon) 교수가 노벨상을 받은 `밀도 범함수론(density functional theory: DFT)'을 기반으로 다방면으로 수행돼왔다.

반면 전압 인가에 따른 비평형 상태에서 작동하는 나노 소자의 제1 원리 계산은 DFT 이론을 적용하기 어렵고 그 대안으로 제시된 이론들에도 한계가 있어 현재 그래핀 기반 2차원 반도체 소자의 엄밀한 양자역학적 시뮬레이션은 불가능한 상황이었다.

연구팀은 먼저 이러한 어려움을 극복하기 위해 자체적으로 수립한 새로운 양자 수송 계산 체계인 다공간 DFT 이론을 발전시켜 그래핀 기반 2차원 터널링 트랜지스터의 제1 원리 시뮬레이션을 가능하게 했다.

다음으로 이를 그래핀 전극-육각형 질화붕소 채널-그래핀 전극 소자 구조에 적용해 질화붕소 층에 존재하는 원자 결함이 다양한 비선형 소자 특성들을 도출시킬 수 있음을 보여 원자 결함의 종류와 위치에 대한 정보가 신뢰성 있는 2차원 소자의 구현에 매우 중요함 요소을 입증했다.

한편 이러한 비선형 소자 특성은 연구진이 기존에 세계 최초로 제안했던 양자 혼성화(quantum hybridization) 소자 원리(device principle)에 따라 발현됨을 보여 2차원 소자의 양자적 특성을 활용하는 한 방향을 제시했다.

김 교수는 "나날이 치열해지는 반도체 연구/개발 분야에서 세계적으로 경쟁력 있는 나노 소자 전산 설계 원천기술을 확보했다ˮ고 연구의 의미를 소개하며 "양자 효과가 극대화될 수밖에 없는 차세대 반도체 연구/개발에서 양자역학적 제1 원리 컴퓨터 시뮬레이션의 역할이 더욱 중요해질 것”이라고 강조했다.

한편 이번 연구는 삼성전자 미래기술 육성센터의 지원을 받아 수행됐다.

2022.04.04 조회수 14521

그래핀 기반 2차원 반도체 소자 시뮬레이션의 양자 도약 달성

반도체 연구 개발에서 소자의 미세화에 따라 원자 수준에서 전류의 흐름을 이해하고 제어하는 것이 핵심적 요소가 되고 있는 상황에서, 우리 연구진이 기존에는 불가능했던 원자만큼 얇은 2차원 반도체 소자의 엄밀한 양자 역학적 컴퓨터 시뮬레이션을 성공적으로 구현하고 이를 기반으로 원자 결함에 의해 발생하는 특이한 소자 특성을 세계 최초로 보고했다.

우리 대학 전기및전자공학부 김용훈 교수 연구팀이 자체적으로 개발한 양자 수송 이론을 통해 세계 최초로 그래핀 전극 간 전자의 터널링 현상(전자가 포텐셜 장벽을 투과하는 현상)으로 작동하는 *2차원 터널링 트랜지스터의 **제1 원리 시뮬레이션을 수행하는 데 성공했다고 4일 밝혔다.

* 2차원 터널링 트랜지스터: 그래핀을 전극으로 하여 전극 간 전자의 터널링(tunneling) 현상을 통해 소자가 작동하는 반도체 소자이다. 소자의 동작 특성을 결정하는 그래핀 전극간 전자의 터널링 현상은 소스-드레인(source-drain) 전극 및 게이트(gate) 전압에 의해 결정된다.

**제1 원리 시뮬레이션: 제1원리 계산은 물질 내 전자들의 거동을 해석할 때 실험적 데이터나 경험적 모델을 도입하지 않고 지배방정식인 슈뢰딩거 방정식을 원자 정보를 포함시켜 직접 푸는 양자역학적 물질 시뮬레이션 방법으로 대표적인 방법론은 밀도 범함수론(density functional theory, DFT)이 있음

전기및전자공학부 김태형 박사과정과 이주호 박사가 공동 제1 저자로 참여한 이번 연구는 소재 계산 분야의 권위 있는 학술지 `네이쳐 파트너 저널 컴퓨테이셔널 머터리얼즈(Npj Computational Materials)' (IF 13.20) 3월 25일 字 온라인판에 게재됐다. (논문명: Gate-versus defect-induced voltage drop and negative differential resistance in vertical graphene heterostructures)

제1 원리 시뮬레이션이란 슈퍼컴퓨터에서 원자 수준의 양자역학 계산을 수행해 실험적 데이터나 경험적 모델의 도움 없이 물질의 특성을 도출하는 방법으로 제1 원리 계산을 통한 평형 상태의 소재 연구는 1998년 월터 콘(Walter Khon) 교수가 노벨상을 받은 `밀도 범함수론(density functional theory: DFT)'을 기반으로 다방면으로 수행돼왔다.

반면 전압 인가에 따른 비평형 상태에서 작동하는 나노 소자의 제1 원리 계산은 DFT 이론을 적용하기 어렵고 그 대안으로 제시된 이론들에도 한계가 있어 현재 그래핀 기반 2차원 반도체 소자의 엄밀한 양자역학적 시뮬레이션은 불가능한 상황이었다.

연구팀은 먼저 이러한 어려움을 극복하기 위해 자체적으로 수립한 새로운 양자 수송 계산 체계인 다공간 DFT 이론을 발전시켜 그래핀 기반 2차원 터널링 트랜지스터의 제1 원리 시뮬레이션을 가능하게 했다.

다음으로 이를 그래핀 전극-육각형 질화붕소 채널-그래핀 전극 소자 구조에 적용해 질화붕소 층에 존재하는 원자 결함이 다양한 비선형 소자 특성들을 도출시킬 수 있음을 보여 원자 결함의 종류와 위치에 대한 정보가 신뢰성 있는 2차원 소자의 구현에 매우 중요함 요소을 입증했다.

한편 이러한 비선형 소자 특성은 연구진이 기존에 세계 최초로 제안했던 양자 혼성화(quantum hybridization) 소자 원리(device principle)에 따라 발현됨을 보여 2차원 소자의 양자적 특성을 활용하는 한 방향을 제시했다.

김 교수는 "나날이 치열해지는 반도체 연구/개발 분야에서 세계적으로 경쟁력 있는 나노 소자 전산 설계 원천기술을 확보했다ˮ고 연구의 의미를 소개하며 "양자 효과가 극대화될 수밖에 없는 차세대 반도체 연구/개발에서 양자역학적 제1 원리 컴퓨터 시뮬레이션의 역할이 더욱 중요해질 것”이라고 강조했다.

한편 이번 연구는 삼성전자 미래기술 육성센터의 지원을 받아 수행됐다.

2022.04.04 조회수 14521 -

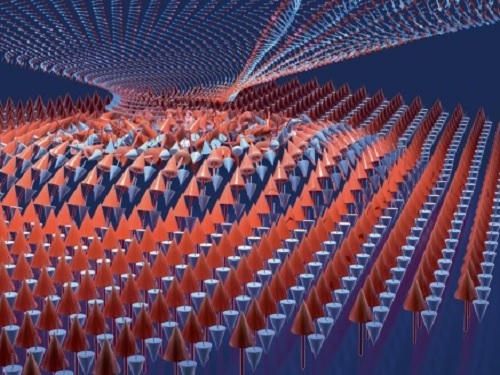

준강자성체를 이용한 차세대 반도체 기술의 발전방향 제시

우리 대학 물리학과 이경진 교수, 김세권 교수 연구팀이 스핀 기반 차세대 반도체 기술(스핀트로닉스)의 최신 연구 동향 및 미래 발전 전략을 정리한 `*준강자성체 기반 스핀트로닉스' 리뷰 논문을 물리 및 재료 분야의 세계적인 학술지 `네이처 머터리얼스 (Nature Materials)' 2022년 1월호에 표지논문으로 게재했다고 6일 밝혔다.

※ 준강자성체: 반강자성체와 같이 서로 이웃하는 자성 이온이 반대 방향으로 정렬되지만, 서로 자성의 크기가 달라서 물질 전체적으로는 자발적인 자성이 남아있는 물체

스핀트로닉스는 성장 한계에 다다른 기존 반도체 기술의 근본적인 문제점들을 전자의 양자적 성질인 스핀을 이용해 해결하고자 하는 연구 분야다. 이는 기존 정보처리 기술을 혁신적으로 발전시켜 초고속 초고집적 차세대 반도체 기술을 구현할 것으로 기대되고 있다. 스핀트로닉스 장치의 핵심 구성 요소는 자성체이기 때문에, 스핀 기반의 초고속 초고집적 정보처리를 구현하기 위해서는 최적의 자성 물질을 규명하는 것이 필수적이다.

지난 수십 년간 스핀트로닉스에서 주로 사용돼왔던 강자성체는 스핀 동역학 속도가 기존 정보 처리 기술의 수준과 유사한 기가헤르츠(GHz) 수준에 머물러 정보 처리 속도 향상에 어려움을 겪고 있었다. 또한, 강자성체가 생성하는 강력한 주위 자기장으로 인해 강자성체 기반 장치들이 서로 강하게 간섭해, 스핀 장치의 집적률을 증가시키는 데도 어려움이 있었다.

물리학과 이경진 교수와 김세권 교수는 지난 수년간의 연구를 통해 새로운 자성체인 준강자성체를 이용하면 강자성체가 갖는 문제점들을 해결해 초고속 초고집적 스핀 기반 정보 처리 장치를 개발할 수 있음을 밝혀왔고, 이를 기반으로 이번 리뷰 논문을 게재했다.

과거 2017년 연구팀은 준강자성체의 스핀 동역학 속도가 기존 정보 처리 기술보다 약 천배 빠른 테라헤르츠(THz) 수준이라는 점을 주목하고, 이를 이용해 스핀 메모리로 활용되는 자구벽을 강자성체보다 월등히 빠른 속도로 구동할 수 있음을 보여 네이처 머터리얼스에 논문을 게재했다. 또한, 2018년 이경진 교수는 반강자성체를 이용하면 스핀 양자 정보의 장거리 전송이 가능함을 밝혀 네이처 머터리얼스에 보고했다. 수년간에 걸친 꾸준한 연구성과로 인해 준강자성체 기반의 초고속 초고집적 스핀트로닉스에 대한 관심이 고조돼, 현재 세계적으로 관련 연구가 활발히 진행중이다.

최신 연구 동향 정리와 더불어, 연구팀은 준강자성체 기반 스핀트로닉스의 미래 발전 방향도 제시했다. 준강자성체 기반의 초고속 자기광학 장치 개발, 준강자성체가 갖는 독특한 스핀파 성질을 이용한 파동/양자 정보처리 장치 개발, 그리고 준강자성체를 이용한 뇌 모사 컴퓨팅 개발 등이 기대된다. 또한, 새로 개발된 준강자성체는 기존의 자성체와 근본적으로 다른 흥미로운 물리현상을 보일 것으로 기대돼 준강자성체 기반의 근본 자성 연구에 대한 발전 방향도 제시했다.

이경진 교수는 "이번 리뷰논문은 그동안 강자성체에만 집중돼왔던 스핀트로닉스 연구를 준강자성체로 확장시키는 데 중요한 이정표가 될 것ˮ이라고 기대감을 내비쳤다.

이번 연구는 이경진 교수, 김세권 교수, 그리고 미국 MIT Geoffrey Beach 교수, 일본 교토대학 Teruo Ono 교수, 네덜란드 Radboud 대학 Theo Rasing, 싱가포르국립대 양현수 교수의 공동 연구로 진행되었으며, 삼성미래기술육성재단과 한국연구재단의 지원을 받아 수행됐다.

2022.01.06 조회수 11024

준강자성체를 이용한 차세대 반도체 기술의 발전방향 제시

우리 대학 물리학과 이경진 교수, 김세권 교수 연구팀이 스핀 기반 차세대 반도체 기술(스핀트로닉스)의 최신 연구 동향 및 미래 발전 전략을 정리한 `*준강자성체 기반 스핀트로닉스' 리뷰 논문을 물리 및 재료 분야의 세계적인 학술지 `네이처 머터리얼스 (Nature Materials)' 2022년 1월호에 표지논문으로 게재했다고 6일 밝혔다.

※ 준강자성체: 반강자성체와 같이 서로 이웃하는 자성 이온이 반대 방향으로 정렬되지만, 서로 자성의 크기가 달라서 물질 전체적으로는 자발적인 자성이 남아있는 물체

스핀트로닉스는 성장 한계에 다다른 기존 반도체 기술의 근본적인 문제점들을 전자의 양자적 성질인 스핀을 이용해 해결하고자 하는 연구 분야다. 이는 기존 정보처리 기술을 혁신적으로 발전시켜 초고속 초고집적 차세대 반도체 기술을 구현할 것으로 기대되고 있다. 스핀트로닉스 장치의 핵심 구성 요소는 자성체이기 때문에, 스핀 기반의 초고속 초고집적 정보처리를 구현하기 위해서는 최적의 자성 물질을 규명하는 것이 필수적이다.

지난 수십 년간 스핀트로닉스에서 주로 사용돼왔던 강자성체는 스핀 동역학 속도가 기존 정보 처리 기술의 수준과 유사한 기가헤르츠(GHz) 수준에 머물러 정보 처리 속도 향상에 어려움을 겪고 있었다. 또한, 강자성체가 생성하는 강력한 주위 자기장으로 인해 강자성체 기반 장치들이 서로 강하게 간섭해, 스핀 장치의 집적률을 증가시키는 데도 어려움이 있었다.

물리학과 이경진 교수와 김세권 교수는 지난 수년간의 연구를 통해 새로운 자성체인 준강자성체를 이용하면 강자성체가 갖는 문제점들을 해결해 초고속 초고집적 스핀 기반 정보 처리 장치를 개발할 수 있음을 밝혀왔고, 이를 기반으로 이번 리뷰 논문을 게재했다.

과거 2017년 연구팀은 준강자성체의 스핀 동역학 속도가 기존 정보 처리 기술보다 약 천배 빠른 테라헤르츠(THz) 수준이라는 점을 주목하고, 이를 이용해 스핀 메모리로 활용되는 자구벽을 강자성체보다 월등히 빠른 속도로 구동할 수 있음을 보여 네이처 머터리얼스에 논문을 게재했다. 또한, 2018년 이경진 교수는 반강자성체를 이용하면 스핀 양자 정보의 장거리 전송이 가능함을 밝혀 네이처 머터리얼스에 보고했다. 수년간에 걸친 꾸준한 연구성과로 인해 준강자성체 기반의 초고속 초고집적 스핀트로닉스에 대한 관심이 고조돼, 현재 세계적으로 관련 연구가 활발히 진행중이다.

최신 연구 동향 정리와 더불어, 연구팀은 준강자성체 기반 스핀트로닉스의 미래 발전 방향도 제시했다. 준강자성체 기반의 초고속 자기광학 장치 개발, 준강자성체가 갖는 독특한 스핀파 성질을 이용한 파동/양자 정보처리 장치 개발, 그리고 준강자성체를 이용한 뇌 모사 컴퓨팅 개발 등이 기대된다. 또한, 새로 개발된 준강자성체는 기존의 자성체와 근본적으로 다른 흥미로운 물리현상을 보일 것으로 기대돼 준강자성체 기반의 근본 자성 연구에 대한 발전 방향도 제시했다.

이경진 교수는 "이번 리뷰논문은 그동안 강자성체에만 집중돼왔던 스핀트로닉스 연구를 준강자성체로 확장시키는 데 중요한 이정표가 될 것ˮ이라고 기대감을 내비쳤다.

이번 연구는 이경진 교수, 김세권 교수, 그리고 미국 MIT Geoffrey Beach 교수, 일본 교토대학 Teruo Ono 교수, 네덜란드 Radboud 대학 Theo Rasing, 싱가포르국립대 양현수 교수의 공동 연구로 진행되었으며, 삼성미래기술육성재단과 한국연구재단의 지원을 받아 수행됐다.

2022.01.06 조회수 11024 -

모트 전이 반도체로 진성 난수 생성기 개발

우리 대학 신소재공학과 김경민 교수 연구팀이 모트 전이 반도체의 확률적 거동을 이용한 진성 난수(True Random Number) 생성기 개발에 성공했다고 18일 밝혔다.

전자기기들이 초연결되는 메타버스 시대에는 전자기기 간에 대량의 데이터가 실시간으로 오가게 되는데, 이때 더욱 고도화된 데이터의 보안과 암호화 기술이 뒷받침돼야 한다. 현재 대부분의 난수는 소프트웨어로 생성되고 있는데, 이렇게 생성된 일반적인 난수는 소프트웨어의 해독을 통해 쉽게 예측할 수 있고 이는 데이터 보안 및 개인 정보 침해에 매우 큰 위협이 될 수 있다.

이에 반해 진성 난수는 자연의 무작위적인 물리적 현상으로부터 얻어지는 인간이 예측할 수 없는 난수로 이를 얻는 것은 궁극의 보안 기술을 구현하기 위해 필수적이다.

김경민 교수 연구팀은 진성 난수를 추출하기 위해 모트 전이 소재에 주목했다. 모트 전이 소재는 특정 온도에서 전기전도도가 부도체에서 도체로 전이하는 소재로, 이 소재에 전류를 흘려주어 가열하면 부도체 상태와 도체 상태가 주기적으로 변하는 상태의 진동 현상을 관찰할 수 있음이 잘 알려져 있었다. 연구팀은 이 과정에서 주기적으로 소재의 가열과 냉각이 반복될 때 열의 생성과 발산이 예측 불가능함을 이론적으로 입증했다.

연구팀은 이와 같은 모트 전이 소재에서의 예측 불가능한 특성을 진성 난수로 변환해주는 프로토타입의 진성 난수 생성기를 설계 및 제작하여 진성 난수를 성공적으로 수집했다.

공동 제1 저자인 신소재공학과 김광민 석사과정과 인재현 박사과정은 "모트 전이 반도체를 기반으로 하는 진성 난수 생성기는 25 마이크로초(μs) 마다 5.22 나노줄(nJ)의 에너지로 1개의 난수를 생성할 수 있는데 이는 기존 기술에 대비 최소 2.5배 이상 빠르고, 1,800분의 1 수준의 에너지로 저전력 동작이 가능하다ˮ며 "이는 저항 변화 메모리의 셀렉터 등 제한된 분야에서만 사용되던 모트 전이 소재를 진성 난수 생성기에 적합하다는 것을 입증한 결과로 새로운 하드웨어 보안용 소재 개발 분야를 개척한 의의가 있다ˮ 라고 말했다.

이러한 진성 난수 생성기는 반도체 칩의 형태로 제작해 기존 전자기기와 호환할 수 있으며 휴대전화 등 전자기기의 보안을 위한 암호화 하드웨어로 사용할 수 있을 것으로 기대된다.

이번 연구는 국제 학술지 `네이처 커뮤니케이션즈(Nature Communications)' 지난 5월 18일 字에 게재됐으며 산업통상자원부, 한국반도체연구조합, KAIST의 지원을 받아 수행됐다. (논문명 : Self-clocking fast and variation tolerant true random number generator based on a stochastic mott memristor)

2021.08.18 조회수 14809

모트 전이 반도체로 진성 난수 생성기 개발

우리 대학 신소재공학과 김경민 교수 연구팀이 모트 전이 반도체의 확률적 거동을 이용한 진성 난수(True Random Number) 생성기 개발에 성공했다고 18일 밝혔다.

전자기기들이 초연결되는 메타버스 시대에는 전자기기 간에 대량의 데이터가 실시간으로 오가게 되는데, 이때 더욱 고도화된 데이터의 보안과 암호화 기술이 뒷받침돼야 한다. 현재 대부분의 난수는 소프트웨어로 생성되고 있는데, 이렇게 생성된 일반적인 난수는 소프트웨어의 해독을 통해 쉽게 예측할 수 있고 이는 데이터 보안 및 개인 정보 침해에 매우 큰 위협이 될 수 있다.

이에 반해 진성 난수는 자연의 무작위적인 물리적 현상으로부터 얻어지는 인간이 예측할 수 없는 난수로 이를 얻는 것은 궁극의 보안 기술을 구현하기 위해 필수적이다.

김경민 교수 연구팀은 진성 난수를 추출하기 위해 모트 전이 소재에 주목했다. 모트 전이 소재는 특정 온도에서 전기전도도가 부도체에서 도체로 전이하는 소재로, 이 소재에 전류를 흘려주어 가열하면 부도체 상태와 도체 상태가 주기적으로 변하는 상태의 진동 현상을 관찰할 수 있음이 잘 알려져 있었다. 연구팀은 이 과정에서 주기적으로 소재의 가열과 냉각이 반복될 때 열의 생성과 발산이 예측 불가능함을 이론적으로 입증했다.

연구팀은 이와 같은 모트 전이 소재에서의 예측 불가능한 특성을 진성 난수로 변환해주는 프로토타입의 진성 난수 생성기를 설계 및 제작하여 진성 난수를 성공적으로 수집했다.

공동 제1 저자인 신소재공학과 김광민 석사과정과 인재현 박사과정은 "모트 전이 반도체를 기반으로 하는 진성 난수 생성기는 25 마이크로초(μs) 마다 5.22 나노줄(nJ)의 에너지로 1개의 난수를 생성할 수 있는데 이는 기존 기술에 대비 최소 2.5배 이상 빠르고, 1,800분의 1 수준의 에너지로 저전력 동작이 가능하다ˮ며 "이는 저항 변화 메모리의 셀렉터 등 제한된 분야에서만 사용되던 모트 전이 소재를 진성 난수 생성기에 적합하다는 것을 입증한 결과로 새로운 하드웨어 보안용 소재 개발 분야를 개척한 의의가 있다ˮ 라고 말했다.

이러한 진성 난수 생성기는 반도체 칩의 형태로 제작해 기존 전자기기와 호환할 수 있으며 휴대전화 등 전자기기의 보안을 위한 암호화 하드웨어로 사용할 수 있을 것으로 기대된다.

이번 연구는 국제 학술지 `네이처 커뮤니케이션즈(Nature Communications)' 지난 5월 18일 字에 게재됐으며 산업통상자원부, 한국반도체연구조합, KAIST의 지원을 받아 수행됐다. (논문명 : Self-clocking fast and variation tolerant true random number generator based on a stochastic mott memristor)

2021.08.18 조회수 14809 -

인간의 뇌를 모방한 뉴로모픽 반도체 개발

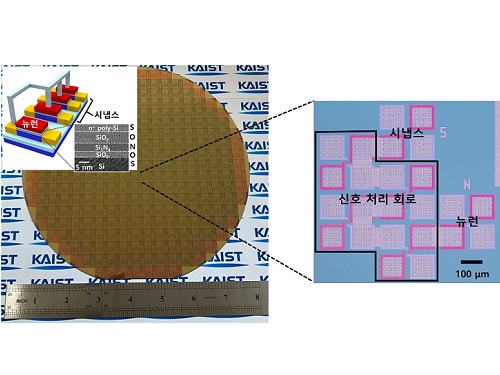

우리 대학 전기및전자공학부 최양규, 최성율 교수 공동연구팀이 인간의 뇌를 모방한 고집적 뉴로모픽 반도체를 개발했다고 5일 밝혔다.

뉴로모픽(neuromorphic) 하드웨어는, 인간의 뇌가 매우 복잡한 기능을 수행하지만 소비하는 에너지는 20와트(W) 밖에 되지 않는다는 것에 착안해, 인간의 뇌를 모방해 인공지능 기능을 하드웨어로 구현하는 방식이다. 뉴로모픽 하드웨어는 기존의 폰 노이만(von Neumann) 방식과 다르게 인공지능 기능을 초저전력으로 수행할 수 있어 많은 주목을 받고 있다.

공동연구팀은 단일 트랜지스터를 이용해 인간의 뇌를 모방한 뉴런과 시냅스로 구성된 뉴로모픽 반도체를 구현했다. 이 반도체는 상용화된 실리콘 표준 공정으로 제작되어, 뉴로모픽 하드웨어 시스템의 상용화 가능성을 획기적으로 높였다.

우리 대학 전기및전자공학부 한준규 박사과정이 제1 저자로, 같은 학부 오정엽 박사과정이 제2 저자로 참여한 이번 연구는 저명 국제 학술지 `사이언스 어드벤시스(Science Advances)' 8월 온라인판에 출판됐다. (논문명 : Co-integration of single transistor neurons and synapses by nanoscale CMOS fabrication for highly scalable neuromorphic hardware).

뉴로모픽 하드웨어를 구현하기 위해서는, 생물학적 뇌와 동일하게 일정 신호가 통합되었을 때 스파이크를 발생하는 뉴런과 두 뉴런 사이의 연결성을 기억하는 시냅스가 필요하다. 하지만, 디지털 또는 아날로그 회로를 기반으로 구성된 뉴런과 시냅스는 큰 면적을 차지하기 때문에 집적도 측면에서 한계가 있다. 인간의 뇌가 약 천억 개(1011)의 뉴런과 백조 개(1014)의 시냅스로 구성된다는 점에서, 실제 모바일 및 사물인터넷(IoT) 장치에 사용되기 위해서는 집적도를 개선할 필요가 있다.

이를 개선하기 위해 다양한 소재 및 구조 기반의 뉴런과 시냅스가 제안되었지만, 대부분 표준 실리콘 미세 공정 기술로 제작될 수 없어 상용화가 어렵고 양산 적용에 문제가 많았다.

연구팀은 문제 해결을 위해 이미 널리 쓰이고 있는 표준 실리콘 미세 공정 기술로 제작될 수 있는 단일 트랜지스터로 생물학적 뉴런과 시냅스의 동작을 모방했으며, 이를 동일 웨이퍼(8 인치) 상에 동시 집적해 뉴로모픽 반도체를 제작했다.

제작된 뉴로모픽 트랜지스터는 현재 양산되고 있는 메모리 및 시스템 반도체용 트랜지스터와 같은 구조로, 트랜지스터가 메모리 기능 및 논리 연산을 수행하는 것은 물론, 새로운 뉴로모픽 동작이 가능함을 실험적으로 보여 준 것에 가장 큰 의미가 있다. 기존 양산 트랜지스터에 새로운 동작원리를 적용해, 구조는 같으나 기능이 전혀 다른 뉴로모픽 트랜지스터를 제작했다. 뉴로모픽 트랜지스터는 마치 동전에 앞면과 뒷면이 동시에 있는 것처럼, 뉴런 기능도 하고 시냅스 기능도 수행하는 야누스(Janus) 구조로 구현 가능함을 세계 최초로 입증했다.

연구팀의 기술은 복잡한 디지털 및 아날로그 회로를 기반으로 구성되던 뉴런을 단일 트랜지스터로 대체 구현해 집적도를 획기적으로 높였고, 더 나아가 같은 구조의 시냅스와 함께 집적해 공정 단순화에 따른 비용 절감을 할 수 있는 신기술이다. 기존 뉴런 회로 구성에 필요한 평면적이 21,000 단위인 반면, 새로 개발된 뉴로모픽 트랜지스터는 6 단위 이하이므로 집적도가 약 3,500 배 이상 높다.

연구팀은 제작된 뉴로모픽 반도체를 바탕으로 증폭 이득 조절, 동시성 판단 등의 뇌의 기능을 일부 모방했고, 글자 이미지 및 얼굴 이미지 인식이 가능함을 보였다.

연구팀이 개발한 뉴로모픽 반도체는 집적도 개선과 비용 절감 등에 이바지하며, 뉴로모픽 하드웨어의 상용화를 앞당길 수 있을 것으로 기대된다.

한준규 박사과정은 "상보성 금속 산화막 반도체(CMOS) 기반 단일 트랜지스터를 이용해 뉴런과 시냅스 동작이 가능함을 보였다ˮ 라며 "상용화된 CMOS 공정을 이용해 뉴런, 시냅스, 그리고 부가적인 신호 처리 회로를 동일 웨이퍼 상에 동시에 집적함으로써, 뉴로모픽 반도체의 집적도를 개선했고, 이는 뉴로모픽 하드웨어의 상용화를 한 단계 앞당길 수 있을 것이다ˮ 라고 말했다.

한편 이번 연구는 한국연구재단 차세대지능형반도체기술개발사업, 중견연구사업, 미래반도체사업 및 반도체설계교육센터의 지원을 받아 수행됐다.

2021.08.06 조회수 15142

인간의 뇌를 모방한 뉴로모픽 반도체 개발

우리 대학 전기및전자공학부 최양규, 최성율 교수 공동연구팀이 인간의 뇌를 모방한 고집적 뉴로모픽 반도체를 개발했다고 5일 밝혔다.

뉴로모픽(neuromorphic) 하드웨어는, 인간의 뇌가 매우 복잡한 기능을 수행하지만 소비하는 에너지는 20와트(W) 밖에 되지 않는다는 것에 착안해, 인간의 뇌를 모방해 인공지능 기능을 하드웨어로 구현하는 방식이다. 뉴로모픽 하드웨어는 기존의 폰 노이만(von Neumann) 방식과 다르게 인공지능 기능을 초저전력으로 수행할 수 있어 많은 주목을 받고 있다.

공동연구팀은 단일 트랜지스터를 이용해 인간의 뇌를 모방한 뉴런과 시냅스로 구성된 뉴로모픽 반도체를 구현했다. 이 반도체는 상용화된 실리콘 표준 공정으로 제작되어, 뉴로모픽 하드웨어 시스템의 상용화 가능성을 획기적으로 높였다.

우리 대학 전기및전자공학부 한준규 박사과정이 제1 저자로, 같은 학부 오정엽 박사과정이 제2 저자로 참여한 이번 연구는 저명 국제 학술지 `사이언스 어드벤시스(Science Advances)' 8월 온라인판에 출판됐다. (논문명 : Co-integration of single transistor neurons and synapses by nanoscale CMOS fabrication for highly scalable neuromorphic hardware).

뉴로모픽 하드웨어를 구현하기 위해서는, 생물학적 뇌와 동일하게 일정 신호가 통합되었을 때 스파이크를 발생하는 뉴런과 두 뉴런 사이의 연결성을 기억하는 시냅스가 필요하다. 하지만, 디지털 또는 아날로그 회로를 기반으로 구성된 뉴런과 시냅스는 큰 면적을 차지하기 때문에 집적도 측면에서 한계가 있다. 인간의 뇌가 약 천억 개(1011)의 뉴런과 백조 개(1014)의 시냅스로 구성된다는 점에서, 실제 모바일 및 사물인터넷(IoT) 장치에 사용되기 위해서는 집적도를 개선할 필요가 있다.

이를 개선하기 위해 다양한 소재 및 구조 기반의 뉴런과 시냅스가 제안되었지만, 대부분 표준 실리콘 미세 공정 기술로 제작될 수 없어 상용화가 어렵고 양산 적용에 문제가 많았다.

연구팀은 문제 해결을 위해 이미 널리 쓰이고 있는 표준 실리콘 미세 공정 기술로 제작될 수 있는 단일 트랜지스터로 생물학적 뉴런과 시냅스의 동작을 모방했으며, 이를 동일 웨이퍼(8 인치) 상에 동시 집적해 뉴로모픽 반도체를 제작했다.

제작된 뉴로모픽 트랜지스터는 현재 양산되고 있는 메모리 및 시스템 반도체용 트랜지스터와 같은 구조로, 트랜지스터가 메모리 기능 및 논리 연산을 수행하는 것은 물론, 새로운 뉴로모픽 동작이 가능함을 실험적으로 보여 준 것에 가장 큰 의미가 있다. 기존 양산 트랜지스터에 새로운 동작원리를 적용해, 구조는 같으나 기능이 전혀 다른 뉴로모픽 트랜지스터를 제작했다. 뉴로모픽 트랜지스터는 마치 동전에 앞면과 뒷면이 동시에 있는 것처럼, 뉴런 기능도 하고 시냅스 기능도 수행하는 야누스(Janus) 구조로 구현 가능함을 세계 최초로 입증했다.

연구팀의 기술은 복잡한 디지털 및 아날로그 회로를 기반으로 구성되던 뉴런을 단일 트랜지스터로 대체 구현해 집적도를 획기적으로 높였고, 더 나아가 같은 구조의 시냅스와 함께 집적해 공정 단순화에 따른 비용 절감을 할 수 있는 신기술이다. 기존 뉴런 회로 구성에 필요한 평면적이 21,000 단위인 반면, 새로 개발된 뉴로모픽 트랜지스터는 6 단위 이하이므로 집적도가 약 3,500 배 이상 높다.

연구팀은 제작된 뉴로모픽 반도체를 바탕으로 증폭 이득 조절, 동시성 판단 등의 뇌의 기능을 일부 모방했고, 글자 이미지 및 얼굴 이미지 인식이 가능함을 보였다.

연구팀이 개발한 뉴로모픽 반도체는 집적도 개선과 비용 절감 등에 이바지하며, 뉴로모픽 하드웨어의 상용화를 앞당길 수 있을 것으로 기대된다.

한준규 박사과정은 "상보성 금속 산화막 반도체(CMOS) 기반 단일 트랜지스터를 이용해 뉴런과 시냅스 동작이 가능함을 보였다ˮ 라며 "상용화된 CMOS 공정을 이용해 뉴런, 시냅스, 그리고 부가적인 신호 처리 회로를 동일 웨이퍼 상에 동시에 집적함으로써, 뉴로모픽 반도체의 집적도를 개선했고, 이는 뉴로모픽 하드웨어의 상용화를 한 단계 앞당길 수 있을 것이다ˮ 라고 말했다.

한편 이번 연구는 한국연구재단 차세대지능형반도체기술개발사업, 중견연구사업, 미래반도체사업 및 반도체설계교육센터의 지원을 받아 수행됐다.

2021.08.06 조회수 15142 -

날숨 속 황화수소 가스 검출을 통한 구취 센서 개발

우리 대학 신소재공학과 김일두 교수 연구팀이 삼성전자 종합기술원과 공동연구를 통해 극소량의 나트륨과 백금 촉매를 금속산화물에 기능화하여 호흡으로 질병을 진단할 수 있는 가스 센서 플랫폼을 개발했다고 28일 밝혔다.

이 가스 센서 플랫폼은 사람의 날숨에 포함된 다양한 질병과 관련된 미량의 생체지표(biomarker) 가스를 선택적으로 감지해 관련된 특정 질병을 실시간 모니터링할 수 있는 기술이다.

혈액 채취나 영상 촬영 없이 내뱉는 숨(호기)만으로 각종 질병 여부를 파악하는 비침습적 호흡 지문 센서 기술은 핵심 미래 기술이다. 호기 속 특정 가스들의 농도변화를 검사해 건강 이상 여부를 판단할 수 있다.

이번 기술은 구취의 생체지표 가스인 황화수소 가스와 높은 반응성을 갖는 나트륨 촉매를 금속산화물 나노섬유 감지 소재 층에 도입해 가스 선택성을 극도로 향상하고, 활성도가 좋은 백금 촉매를 추가로 기능화해 세계 최고 수준의 황화수소 감지 성능을 구현한 기술이다.

호기 가스의 성분에는 수분 외에도 아세톤, 톨루엔, 암모니아, 수소뿐만 아니라 구취의 생체지표 가스인 황화수소(hydrogen sulfide), 메틸머캅탄(methyl mercaptan), 디메틸설파이드(dimethyl sulfide)의 3종 황 화합물이 포함된다. 그중에서 황화수소 가스는 구취 환자에게서 높은 농도로 배출되는 생체지표 가스로서 상기 3종 황화합물 가스 중에서 선택적으로 감지하는 것이 매우 중요하다.

호흡을 이용한 질병 진단은 테들라(Tedlar) 백에 포집된 날숨 가스를 소형 센서 장치로 주입한 후 수분 이내의 빠른 속도로 분석할 수 있는 비침습 진단 방법으로 최근 조명을 받고 있다. 또한, 질병 대사가 일어나는 시점에서 검출할 수 있어 조기 진단이 용이하다.

하지만 생체지표 가스들은 매우 미량의 농도인 10억분의 1(ppb)에서 100만분의 1(ppm) 수준으로 호흡 속에서 배출되기 때문에 정확한 분석을 위해서는 기술의 진보가 필요하다. 호기 속 수백 종 이상의 방해 가스들 속에서 목표 가스만을 선택적으로 분석하는 것은 저항 변화식 센서의 취약점으로 남아있다.

기존 가스 센서는 산화물 감지 소재 표면에 백금, 팔라듐 등 특정 촉매를 결합하거나 n-형 반도체식 금속산화물과 p-형 반도체식 금속산화물의 헤테로 접합 구조를 도입해 감지 특성을 높이려는 등의 시도가 있었으나 여전히 ppb 농도에서 생체지표 가스 감지 특성이 높지 않다는 한계가 있다.

연구팀은 미량의 염화 나트륨(NaCl)과 백금 촉매를 전기방사를 통해 넓은 비표면적과 다공성 구조를 갖는 금속산화물 나노섬유에 결착시켜 특정 생체지표 가스에 선택적으로 반응하는 감지 소재를 개발했다. 나트륨과 백금의 복합촉매가 결착된 나노섬유 센서는 백금 촉매만 결착되거나 촉매가 결착되지 않은 센서 대비 각각 10배 및 200배 이상 감지 특성이 향상됨을 확인했다.

특히 1 ppm의 황화수소 가스에 대해 감도가 780배 수준으로 바뀌는 세계 최고 수준의 감도 특성을 확인했고, 호기 속 방해 가스 중 반응성이 좋다고 알려진 에탄올 가스 대비 약 277배 수준의 선택도가 관찰됐다.

연구팀은 기존에도 호흡으로 질병을 진단하는 센서를 개발했으나 이번 기술은 가스 감지 성능 및 정확도와 신뢰도가 큰 폭으로 향상됐다는 특징이 있다. 또한, 연구팀은 이번에 개발한 초고성능의 가스 센서를 상용화된 압력센서, 온도센서, 습도센서와 결합해 간단하게 날숨을 불어넣는 것(호기 가스 직접 측정)만으로도 개개인의 호흡을 분석해 일반인도 쉽게 건강 이상을 판별할 수 있는 휴대용 복합센서 디바이스 플랫폼을 개발했다.

연구팀은 가스 크로마토그래피-질량분석법 기반 상용 구취 진단기를 활용한 호기 가스의 정성적 정량적 비교분석을 바탕으로 80건의 날숨 분석을 진행한 결과, 이번 복합센서 플랫폼이 86.3%의 정확도로 구취 유무를 판별할 수 있음을 확인했다. 이번 기술은 구취 유무를 지속적으로 모니터링하는 헬스케어 기기에 손쉽게 적용할 수 있다.

김일두 교수는 "기존 센서에 사용되지 않은 알칼리 금속 기반 촉매를 잘 알려진 백금 촉매와 함께 도입함으로써, 질병과 연관된 생체지표 가스에 초고감도 및 고 선택성으로 반응하는 센서 소재를 구현할 수 있었다ˮ며 "감지 소재 개발에 머물지 않고 실제 센서 디바이스 구현 및 호기 가스 임상시험을 통해 높은 정확도로 구취 유무를 판별할 수 있다는 측면에서 매우 의미가 있는 연구 결과다. 누구나 손쉽게 스스로 진단할 수 있는 자가 진단 기기의 진보는 의료비 지출 상승을 막고 지속적인 건강관리에 큰 도움이 될 것이다ˮ고 밝혔다.

이번 연구는 공동 제1 저자인 신하민, 김동하 박사과정(KAIST 신소재)과 정원종 전문연구원(삼성전자 종합기술원)의 주도하에 진행됐으며, 남궁각 전문연구원(삼성전자 종합기술원)과 김일두 교수(KAIST 신소재)가 교신저자로 참여했다.

연구 결과는 나노과학 분야의 권위적인 학술지 `에이씨에스 나노(ACS Nano)' 8월호 표지 논문으로 발행될 예정이며, `미국화학학회(ACS) 위클리 프레스팩(Weekly PressPac)'에 7월 21일 자로 소개되어 전 세계 수천 명의 기자단에게 홍보됐다. 또한, 관련 기술은 국내를 포함해 유럽, 미국, 중국에 특허로 출원됐다.

2021.07.29 조회수 15193

날숨 속 황화수소 가스 검출을 통한 구취 센서 개발

우리 대학 신소재공학과 김일두 교수 연구팀이 삼성전자 종합기술원과 공동연구를 통해 극소량의 나트륨과 백금 촉매를 금속산화물에 기능화하여 호흡으로 질병을 진단할 수 있는 가스 센서 플랫폼을 개발했다고 28일 밝혔다.

이 가스 센서 플랫폼은 사람의 날숨에 포함된 다양한 질병과 관련된 미량의 생체지표(biomarker) 가스를 선택적으로 감지해 관련된 특정 질병을 실시간 모니터링할 수 있는 기술이다.

혈액 채취나 영상 촬영 없이 내뱉는 숨(호기)만으로 각종 질병 여부를 파악하는 비침습적 호흡 지문 센서 기술은 핵심 미래 기술이다. 호기 속 특정 가스들의 농도변화를 검사해 건강 이상 여부를 판단할 수 있다.

이번 기술은 구취의 생체지표 가스인 황화수소 가스와 높은 반응성을 갖는 나트륨 촉매를 금속산화물 나노섬유 감지 소재 층에 도입해 가스 선택성을 극도로 향상하고, 활성도가 좋은 백금 촉매를 추가로 기능화해 세계 최고 수준의 황화수소 감지 성능을 구현한 기술이다.

호기 가스의 성분에는 수분 외에도 아세톤, 톨루엔, 암모니아, 수소뿐만 아니라 구취의 생체지표 가스인 황화수소(hydrogen sulfide), 메틸머캅탄(methyl mercaptan), 디메틸설파이드(dimethyl sulfide)의 3종 황 화합물이 포함된다. 그중에서 황화수소 가스는 구취 환자에게서 높은 농도로 배출되는 생체지표 가스로서 상기 3종 황화합물 가스 중에서 선택적으로 감지하는 것이 매우 중요하다.

호흡을 이용한 질병 진단은 테들라(Tedlar) 백에 포집된 날숨 가스를 소형 센서 장치로 주입한 후 수분 이내의 빠른 속도로 분석할 수 있는 비침습 진단 방법으로 최근 조명을 받고 있다. 또한, 질병 대사가 일어나는 시점에서 검출할 수 있어 조기 진단이 용이하다.

하지만 생체지표 가스들은 매우 미량의 농도인 10억분의 1(ppb)에서 100만분의 1(ppm) 수준으로 호흡 속에서 배출되기 때문에 정확한 분석을 위해서는 기술의 진보가 필요하다. 호기 속 수백 종 이상의 방해 가스들 속에서 목표 가스만을 선택적으로 분석하는 것은 저항 변화식 센서의 취약점으로 남아있다.

기존 가스 센서는 산화물 감지 소재 표면에 백금, 팔라듐 등 특정 촉매를 결합하거나 n-형 반도체식 금속산화물과 p-형 반도체식 금속산화물의 헤테로 접합 구조를 도입해 감지 특성을 높이려는 등의 시도가 있었으나 여전히 ppb 농도에서 생체지표 가스 감지 특성이 높지 않다는 한계가 있다.

연구팀은 미량의 염화 나트륨(NaCl)과 백금 촉매를 전기방사를 통해 넓은 비표면적과 다공성 구조를 갖는 금속산화물 나노섬유에 결착시켜 특정 생체지표 가스에 선택적으로 반응하는 감지 소재를 개발했다. 나트륨과 백금의 복합촉매가 결착된 나노섬유 센서는 백금 촉매만 결착되거나 촉매가 결착되지 않은 센서 대비 각각 10배 및 200배 이상 감지 특성이 향상됨을 확인했다.

특히 1 ppm의 황화수소 가스에 대해 감도가 780배 수준으로 바뀌는 세계 최고 수준의 감도 특성을 확인했고, 호기 속 방해 가스 중 반응성이 좋다고 알려진 에탄올 가스 대비 약 277배 수준의 선택도가 관찰됐다.

연구팀은 기존에도 호흡으로 질병을 진단하는 센서를 개발했으나 이번 기술은 가스 감지 성능 및 정확도와 신뢰도가 큰 폭으로 향상됐다는 특징이 있다. 또한, 연구팀은 이번에 개발한 초고성능의 가스 센서를 상용화된 압력센서, 온도센서, 습도센서와 결합해 간단하게 날숨을 불어넣는 것(호기 가스 직접 측정)만으로도 개개인의 호흡을 분석해 일반인도 쉽게 건강 이상을 판별할 수 있는 휴대용 복합센서 디바이스 플랫폼을 개발했다.

연구팀은 가스 크로마토그래피-질량분석법 기반 상용 구취 진단기를 활용한 호기 가스의 정성적 정량적 비교분석을 바탕으로 80건의 날숨 분석을 진행한 결과, 이번 복합센서 플랫폼이 86.3%의 정확도로 구취 유무를 판별할 수 있음을 확인했다. 이번 기술은 구취 유무를 지속적으로 모니터링하는 헬스케어 기기에 손쉽게 적용할 수 있다.

김일두 교수는 "기존 센서에 사용되지 않은 알칼리 금속 기반 촉매를 잘 알려진 백금 촉매와 함께 도입함으로써, 질병과 연관된 생체지표 가스에 초고감도 및 고 선택성으로 반응하는 센서 소재를 구현할 수 있었다ˮ며 "감지 소재 개발에 머물지 않고 실제 센서 디바이스 구현 및 호기 가스 임상시험을 통해 높은 정확도로 구취 유무를 판별할 수 있다는 측면에서 매우 의미가 있는 연구 결과다. 누구나 손쉽게 스스로 진단할 수 있는 자가 진단 기기의 진보는 의료비 지출 상승을 막고 지속적인 건강관리에 큰 도움이 될 것이다ˮ고 밝혔다.

이번 연구는 공동 제1 저자인 신하민, 김동하 박사과정(KAIST 신소재)과 정원종 전문연구원(삼성전자 종합기술원)의 주도하에 진행됐으며, 남궁각 전문연구원(삼성전자 종합기술원)과 김일두 교수(KAIST 신소재)가 교신저자로 참여했다.

연구 결과는 나노과학 분야의 권위적인 학술지 `에이씨에스 나노(ACS Nano)' 8월호 표지 논문으로 발행될 예정이며, `미국화학학회(ACS) 위클리 프레스팩(Weekly PressPac)'에 7월 21일 자로 소개되어 전 세계 수천 명의 기자단에게 홍보됐다. 또한, 관련 기술은 국내를 포함해 유럽, 미국, 중국에 특허로 출원됐다.

2021.07.29 조회수 15193 -

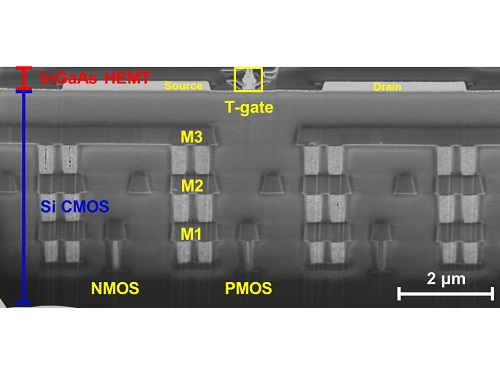

3차원 적층형 화합물 반도체 소자 제작 성공

우리 대학 전기및전자공학부 김상현 교수 연구팀이 *모놀리식 3차원 집적의 장점을 극대화해 기존의 통신 소자의 단점을 극복하는 화합물 반도체 소자 집적 기술을 개발했다고 14일 밝혔다.

☞ 모놀리식 3차원 집적: 하부 소자 공정 후, 상부의 박막층을 형성하고 상부 소자 공정을 순차적으로 진행함으로써 상하부 소자 간의 정렬도를 극대화할 수 있는 기술로 궁극적 3차원 집적 기술로 불린다.

우리 대학 전기및전자공학부 정재용 박사과정이 제1 저자로 주도하고 한국나노기술원 김종민 박사, 광주과학기술원 장재형 교수 연구팀과의 협업으로 진행한 이번 연구는 반도체 올림픽이라 불리는 ‘VLSI 기술 심포지엄(Symposium on VLSI Technology)’에서 발표됐다. (논문명 : High-performance InGaAs-On-Insulator HEMTs on Si CMOS for Substrate Coupling Noise-free Monolithic 3D Mixed-Signal IC).

VLSI 기술 심포지엄은 국제전자소자학회(International Electron Device Meetings, IEDM)와 더불어 대학 논문의 채택비율이 25%가 되지 않는 저명한 반도체 소자 분야 최고 권위 학회다.

반도체 소자는 4차 산업 혁명의 특징인 초연결성 구현을 위한 핵심 통신 소재 및 부품으로서 주목받고 있다.

특히 통신 신호, 양자 신호는 아날로그 형태의 신호이고 신호전달 과정에서 신호의 크기가 약해지거나 잡음이 생겨 신호의 왜곡이 생기기도 한다. 따라서 이러한 신호를 주고받을 때 고속으로 신호의 증폭이 필요한데 이러한 증폭 소자에서는 초고속, 고출력, 저전력, 저잡음 등의 특성이 매우 중요하다. 또한 통신 기술이 발전함에 따라 이를 구성하는 시스템은 점점 더 복잡해져 고집적 소자 제작기술이 매우 중요하다.

통신 소자는 통상적으로 두 가지 방식으로 구현된다. 실리콘(Si)을 사용해 집적도 높은 Si CMOS를 이용해 증폭 소자를 구현하는 방법과 *III-V 화합물 반도체를 증폭 소자로 제작하고 기타 소자들을 Si CMOS로 제작해 패키징 하는 방식이 있다. 그러나 각각의 방식은 단점이 존재한다. 기존의 실리콘(Si) 기술은 물성적 한계로 인해 차단주파수 특성 등 통신 소자에 중요한 소자 성능 향상이 어려우며 기판 커플링 잡음 등 복잡한 신호 간섭에 의한 잡음 증가 문제가 존재한다. 반면, III-V 화합물 반도체 기술은 소자 자체의 잡음 특성은 우수하지만 다른 부품과의 집적/패키징 공정이 복잡하고 이러한 패키징 공정으로 인해 신호의 손실이 발생하는 문제가 존재한다.

☞ III-V 화합물 반도체: 주기율표 III족 원소와 V족 원소가 화합물을 이루고 있는 반도체로 전하 수송 특성 및 광 특성이 매우 우수한 소재

연구팀은 이러한 문제 해결을 위해 증폭 소자 이외의 소자 및 디지털 회로에서 좋은 성능을 낼 수 있는 Si CMOS 기판 위에 아날로그 신호 증폭 성능이 매우 우수한 III-V 화합물 반도체 *HEMT를 3차원 집적해 Si CMOS와 III-V HEMT의 장점을 극대화하는 공정 및 소자 구조를 제시했다. 3층으로 소자를 쌓아나감으로써 같은 기판 위에 집적할 수 있는 방식이다. 이와 동시에 기판 신호 간섭에 의한 잡음을 제거할 수 있음을 증명했다.

☞ HEMT: High-Electron Mobility Transistor

연구팀은 하부 Si CMOS의 성능 저하 방지를 위해 300oC 이하에서 상부 III-V 소자를 집적하는 웨이퍼 본딩 등의 초저온 공정을 활용해 상부 소자 집적 후에도 하부 Si CMOS의 성능을 그대로 유지할 수 있었다.

또한 고성능 상부 III-V 소자 제작을 위해서 InGaAs/InAs/InGaAs의 양자우물 구조를 도입해 높은 전자 수송 특성을 실현했으며 100 나노미터(nm) 노드 공정 수준으로도 세계 최고 수준의 차단 주파수 특성을 달성했다. 이는 10 나노미터(nm) 이하 급의 최첨단 공정을 사용하지 않고도 그 이상의 우수한 성능을 낼 수 있는 융합 기술로 향후 기존과 다른 형태의 파운드리 비즈니스 방식의 도입 가능성을 증명했다고 할 수 있다.

더불어 연구진은 이러한 3차원 집적 형태로 소자를 제작함으로써 기존에 SI CMOS에서 존재하는 기판 간섭에 의한 잡음을 해결할 수 있음을 실험을 통해 최초로 증명했다.

김상현 교수는 “디지털 회로 및 다양한 수동소자 제작에 최적화된 Si CMOS 기판 위에 증폭기 등의 능동소자 특성이 현존하는 어떤 물질보다 우수한 III-V 화합물 반도체 소자를 동시 집적할 가능성을 최초로 입증한 연구로, 향후 통신 소자 등에 응용이 가능할 것으로 생각한다”라며 “이번 기술은 향후 양자 큐빗의 해독 회로에도 응용할 수 있어 그 확장성이 매우 큰 기술이다. 다양한 분야에서 활용할 수 있도록 후속 연구에 힘쓰겠다”라고 말했다.

한편 이번 연구는 한국연구재단 지능형반도체기술개발사업, 경기도 시스템반도체 국산화 연구지원 사업 등의 지원을 받아 수행됐다.

2021.06.14 조회수 55144

3차원 적층형 화합물 반도체 소자 제작 성공

우리 대학 전기및전자공학부 김상현 교수 연구팀이 *모놀리식 3차원 집적의 장점을 극대화해 기존의 통신 소자의 단점을 극복하는 화합물 반도체 소자 집적 기술을 개발했다고 14일 밝혔다.

☞ 모놀리식 3차원 집적: 하부 소자 공정 후, 상부의 박막층을 형성하고 상부 소자 공정을 순차적으로 진행함으로써 상하부 소자 간의 정렬도를 극대화할 수 있는 기술로 궁극적 3차원 집적 기술로 불린다.

우리 대학 전기및전자공학부 정재용 박사과정이 제1 저자로 주도하고 한국나노기술원 김종민 박사, 광주과학기술원 장재형 교수 연구팀과의 협업으로 진행한 이번 연구는 반도체 올림픽이라 불리는 ‘VLSI 기술 심포지엄(Symposium on VLSI Technology)’에서 발표됐다. (논문명 : High-performance InGaAs-On-Insulator HEMTs on Si CMOS for Substrate Coupling Noise-free Monolithic 3D Mixed-Signal IC).

VLSI 기술 심포지엄은 국제전자소자학회(International Electron Device Meetings, IEDM)와 더불어 대학 논문의 채택비율이 25%가 되지 않는 저명한 반도체 소자 분야 최고 권위 학회다.

반도체 소자는 4차 산업 혁명의 특징인 초연결성 구현을 위한 핵심 통신 소재 및 부품으로서 주목받고 있다.

특히 통신 신호, 양자 신호는 아날로그 형태의 신호이고 신호전달 과정에서 신호의 크기가 약해지거나 잡음이 생겨 신호의 왜곡이 생기기도 한다. 따라서 이러한 신호를 주고받을 때 고속으로 신호의 증폭이 필요한데 이러한 증폭 소자에서는 초고속, 고출력, 저전력, 저잡음 등의 특성이 매우 중요하다. 또한 통신 기술이 발전함에 따라 이를 구성하는 시스템은 점점 더 복잡해져 고집적 소자 제작기술이 매우 중요하다.

통신 소자는 통상적으로 두 가지 방식으로 구현된다. 실리콘(Si)을 사용해 집적도 높은 Si CMOS를 이용해 증폭 소자를 구현하는 방법과 *III-V 화합물 반도체를 증폭 소자로 제작하고 기타 소자들을 Si CMOS로 제작해 패키징 하는 방식이 있다. 그러나 각각의 방식은 단점이 존재한다. 기존의 실리콘(Si) 기술은 물성적 한계로 인해 차단주파수 특성 등 통신 소자에 중요한 소자 성능 향상이 어려우며 기판 커플링 잡음 등 복잡한 신호 간섭에 의한 잡음 증가 문제가 존재한다. 반면, III-V 화합물 반도체 기술은 소자 자체의 잡음 특성은 우수하지만 다른 부품과의 집적/패키징 공정이 복잡하고 이러한 패키징 공정으로 인해 신호의 손실이 발생하는 문제가 존재한다.

☞ III-V 화합물 반도체: 주기율표 III족 원소와 V족 원소가 화합물을 이루고 있는 반도체로 전하 수송 특성 및 광 특성이 매우 우수한 소재

연구팀은 이러한 문제 해결을 위해 증폭 소자 이외의 소자 및 디지털 회로에서 좋은 성능을 낼 수 있는 Si CMOS 기판 위에 아날로그 신호 증폭 성능이 매우 우수한 III-V 화합물 반도체 *HEMT를 3차원 집적해 Si CMOS와 III-V HEMT의 장점을 극대화하는 공정 및 소자 구조를 제시했다. 3층으로 소자를 쌓아나감으로써 같은 기판 위에 집적할 수 있는 방식이다. 이와 동시에 기판 신호 간섭에 의한 잡음을 제거할 수 있음을 증명했다.

☞ HEMT: High-Electron Mobility Transistor

연구팀은 하부 Si CMOS의 성능 저하 방지를 위해 300oC 이하에서 상부 III-V 소자를 집적하는 웨이퍼 본딩 등의 초저온 공정을 활용해 상부 소자 집적 후에도 하부 Si CMOS의 성능을 그대로 유지할 수 있었다.

또한 고성능 상부 III-V 소자 제작을 위해서 InGaAs/InAs/InGaAs의 양자우물 구조를 도입해 높은 전자 수송 특성을 실현했으며 100 나노미터(nm) 노드 공정 수준으로도 세계 최고 수준의 차단 주파수 특성을 달성했다. 이는 10 나노미터(nm) 이하 급의 최첨단 공정을 사용하지 않고도 그 이상의 우수한 성능을 낼 수 있는 융합 기술로 향후 기존과 다른 형태의 파운드리 비즈니스 방식의 도입 가능성을 증명했다고 할 수 있다.

더불어 연구진은 이러한 3차원 집적 형태로 소자를 제작함으로써 기존에 SI CMOS에서 존재하는 기판 간섭에 의한 잡음을 해결할 수 있음을 실험을 통해 최초로 증명했다.

김상현 교수는 “디지털 회로 및 다양한 수동소자 제작에 최적화된 Si CMOS 기판 위에 증폭기 등의 능동소자 특성이 현존하는 어떤 물질보다 우수한 III-V 화합물 반도체 소자를 동시 집적할 가능성을 최초로 입증한 연구로, 향후 통신 소자 등에 응용이 가능할 것으로 생각한다”라며 “이번 기술은 향후 양자 큐빗의 해독 회로에도 응용할 수 있어 그 확장성이 매우 큰 기술이다. 다양한 분야에서 활용할 수 있도록 후속 연구에 힘쓰겠다”라고 말했다.

한편 이번 연구는 한국연구재단 지능형반도체기술개발사업, 경기도 시스템반도체 국산화 연구지원 사업 등의 지원을 받아 수행됐다.

2021.06.14 조회수 55144 -

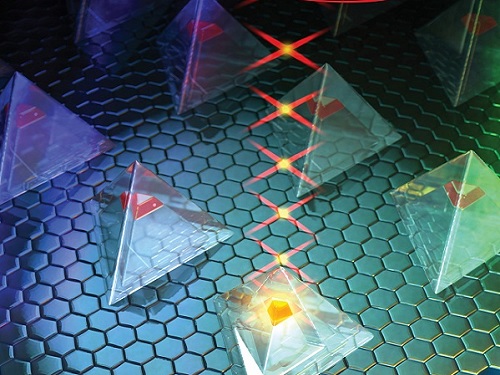

차세대 양자광원을 위한 반도체 양자점 대칭성 제어기술 개발

우리 대학 물리학과 조용훈 교수 연구팀이 LED에 널리 사용되는 질소화합물 반도체를 이용해 대칭성이 매우 높은 삼각형 형태의 양자점(퀀텀닷)을 형성하고 제어하는 데 성공, 광자들 사이에 얽힘을 발생시키는 차세대 양자광원 개발에 핵심적인 양자점 제어 기술을 갖추게 됐다고 13일 밝혔다.

‘얽힘(entanglement)’은 입자들이 쌍으로 상관관계를 가져 거리에 상관없이 얽혀 있는 쌍의 한쪽 특성을 측정하면 나머지 한쪽의 특성을 즉시 알게 되는 현상으로, 전문가들은 얽힘이라는 양자역학적인 현상을 활용하면 양자통신과 양자컴퓨팅과 같은 양자정보에 필요한 기술 개발과 함께 물리학적으로 새로운 주제들이 개척될 것으로 기대하고 있다.

반도체 양자점(Quantum Dot)은 원하는 순간에 광자를 한 개씩 방출하는 대표적인 고체 기반의 양자광 방출 소자로써 널리 연구되고 있다. 특히, 반도체 양자점의 대칭성을 제어해 양자점 내부의 미세 에너지 구조를 정교하게 조절할 수 있다면, 두 개의 광자를 양자얽힘 상태로 만드는 편광얽힘 광자쌍 방출이 원리적으로 가능하므로 이를 이용한 양자통신 및 양자컴퓨팅 분야에서 주목받고 있다.

격자구조를 갖는 반도체는 일반적으로 원자들을 한 층씩 천천히 쌓아 올리는 박막 증착기술을 통해 제작된다. 이때 발광층을 형성하기 위해 격자크기가 다른 층을 쌓게 돼 반도체 내부에 응력이 발생하게 되는데, 발광층이 갖는 응력을 에너지로 사용해 양자점이 무작위적으로 형성되므로 양자점의 크기의 균질성과 대칭성이 떨어지고 근본적으로 양자점의 위치와 모양을 제어할 수 없는 한계를 가진다. 따라서 얽힘 광자쌍 방출소자를 제작하기 위해서는 제작단계에서 위치와 대칭성을 제어할 수 있는 기술이 필수적이다.

한편, 청⦁녹색 LED에 사용되는 물질로 잘 알려진 질소화합물 반도체는 상온에서도 양자적인 특성을 유지할 수 있어 상온에서 안정적으로 구현할 수 있는 양자광원 소자의 후보 물질로도 주목받고 있다. 그러나, 이 물질계는 양자점의 대칭성이 조금만 무너져도 양자역학적 얽힘 특성을 쉽게 잃어버리게 되므로 높은 수준의 대칭성 제어 기술을 확보하지 않고는 실질적으로 구현이 쉽지 않은 한계가 있었다.

조용훈 교수 연구팀은 양자점의 위치와 대칭성을 높은 수준으로 제어하기 위해, 삼각형 형태의 나노 배열 패턴을 갖는 기판 위에 삼각 피라미드 형태를 갖는 질소화합물 반도체 나노 구조를 우선 제작했다. 이후 양자점을 성장하는 단계에서 나노 피라미드 꼭지점 부분의 기하학적 형태를 조절하면서, 열역학적 안정성에 의해 자체적으로 성장 방식이 조절되는 자기제한적 성장메커니즘을 적용했다.

그 결과 육각형 결정구조를 갖는 질소화합물 반도체에서 일반적으로 나타나는 육각 대칭성을 갖는 비균일한 양자점 대신, 삼각 대칭성을 갖는 고품위의 양자점을 최초로 구현함으로써 질소화합물 반도체 양자점의 대칭성을 정교하게 제어하는 데 성공했다.

연구팀은 제작된 나노 구조체의 발광을 분석하기 위해 공간분해능이 수 나노미터 수준으로 좋은 주사전자현미경을 이용해 발광을 측정, 삼각 피라미드의 꼭지점에 양자점이 안정적으로 형성되었음을 확인했고, 시간에 따른 광자 간 상관관계 측정을 통해 양자광이 방출되는 것을 실험적으로 관측했다.

또한, 성장된 양자점의 비대칭성 정도를 가늠할 수 있는 양자광의 편광도와 미세구조 분리 정도를 측정해 높은 대칭성을 갖는 삼각 양자점이 형성되었음을 실험적으로 확인했으며, 이를 이론적 계산 결과와 비교함으로써 측정 결과의 타당성을 확보했다.

이번 연구에서는 기존에 질화물 반도체 양자점의 비대칭성과 높은 편광도를 이용해 상온 단일광자 방출기 제작에 집중해 오던 방식에서 벗어나, 양자점의 대칭성을 정밀하게 조절해 편광얽힘 광자쌍 방출기로도 응용 가능함을 제안했다. 또한 범용 반도체 박막 증착장비와 미세 패턴 기술을 사용했기 때문에 산업적인 측면에서 확장성이 높을 것으로 기대된다.

연구를 주도한 조용훈 교수는 "반도체 양자점을 제작하는 과정에서 발생하는 양자점의 비대칭성을 효과적으로 제어하여 양자점 내부의 미세 에너지 구조를 정교하게 조절할 수 있음을 보여준 결과”라며, “상온에서도 동작이 가능한 질소화합물 반도체 양자점을 이용해 편광얽힘 광자쌍 방출소자와 같은 차세대 양자광원 개발에 활용될 수 있을 것”이라고 의미를 말했다.

우리 대학 물리학과 여환섭 박사가 제1 저자로 참여한 이번 연구 결과는 삼성미래기술육성사업 등의 지원을 받아 수행됐으며, 나노분야 국제 학술지인 `나노 레터스(Nano Letters)' 12월 9일 字에 보충 표지와 함께 정식 출간됐다. (논문명: Control of 3-fold symmetric shape of group III-nitride quantum dots: Suppression of fine structure splitting / 질소화합물 반도체 양자점의 삼각 대칭적 모양 제어: 미세구조 분리현상의 완화)

2020.12.14 조회수 52083

차세대 양자광원을 위한 반도체 양자점 대칭성 제어기술 개발

우리 대학 물리학과 조용훈 교수 연구팀이 LED에 널리 사용되는 질소화합물 반도체를 이용해 대칭성이 매우 높은 삼각형 형태의 양자점(퀀텀닷)을 형성하고 제어하는 데 성공, 광자들 사이에 얽힘을 발생시키는 차세대 양자광원 개발에 핵심적인 양자점 제어 기술을 갖추게 됐다고 13일 밝혔다.

‘얽힘(entanglement)’은 입자들이 쌍으로 상관관계를 가져 거리에 상관없이 얽혀 있는 쌍의 한쪽 특성을 측정하면 나머지 한쪽의 특성을 즉시 알게 되는 현상으로, 전문가들은 얽힘이라는 양자역학적인 현상을 활용하면 양자통신과 양자컴퓨팅과 같은 양자정보에 필요한 기술 개발과 함께 물리학적으로 새로운 주제들이 개척될 것으로 기대하고 있다.

반도체 양자점(Quantum Dot)은 원하는 순간에 광자를 한 개씩 방출하는 대표적인 고체 기반의 양자광 방출 소자로써 널리 연구되고 있다. 특히, 반도체 양자점의 대칭성을 제어해 양자점 내부의 미세 에너지 구조를 정교하게 조절할 수 있다면, 두 개의 광자를 양자얽힘 상태로 만드는 편광얽힘 광자쌍 방출이 원리적으로 가능하므로 이를 이용한 양자통신 및 양자컴퓨팅 분야에서 주목받고 있다.

격자구조를 갖는 반도체는 일반적으로 원자들을 한 층씩 천천히 쌓아 올리는 박막 증착기술을 통해 제작된다. 이때 발광층을 형성하기 위해 격자크기가 다른 층을 쌓게 돼 반도체 내부에 응력이 발생하게 되는데, 발광층이 갖는 응력을 에너지로 사용해 양자점이 무작위적으로 형성되므로 양자점의 크기의 균질성과 대칭성이 떨어지고 근본적으로 양자점의 위치와 모양을 제어할 수 없는 한계를 가진다. 따라서 얽힘 광자쌍 방출소자를 제작하기 위해서는 제작단계에서 위치와 대칭성을 제어할 수 있는 기술이 필수적이다.

한편, 청⦁녹색 LED에 사용되는 물질로 잘 알려진 질소화합물 반도체는 상온에서도 양자적인 특성을 유지할 수 있어 상온에서 안정적으로 구현할 수 있는 양자광원 소자의 후보 물질로도 주목받고 있다. 그러나, 이 물질계는 양자점의 대칭성이 조금만 무너져도 양자역학적 얽힘 특성을 쉽게 잃어버리게 되므로 높은 수준의 대칭성 제어 기술을 확보하지 않고는 실질적으로 구현이 쉽지 않은 한계가 있었다.

조용훈 교수 연구팀은 양자점의 위치와 대칭성을 높은 수준으로 제어하기 위해, 삼각형 형태의 나노 배열 패턴을 갖는 기판 위에 삼각 피라미드 형태를 갖는 질소화합물 반도체 나노 구조를 우선 제작했다. 이후 양자점을 성장하는 단계에서 나노 피라미드 꼭지점 부분의 기하학적 형태를 조절하면서, 열역학적 안정성에 의해 자체적으로 성장 방식이 조절되는 자기제한적 성장메커니즘을 적용했다.

그 결과 육각형 결정구조를 갖는 질소화합물 반도체에서 일반적으로 나타나는 육각 대칭성을 갖는 비균일한 양자점 대신, 삼각 대칭성을 갖는 고품위의 양자점을 최초로 구현함으로써 질소화합물 반도체 양자점의 대칭성을 정교하게 제어하는 데 성공했다.

연구팀은 제작된 나노 구조체의 발광을 분석하기 위해 공간분해능이 수 나노미터 수준으로 좋은 주사전자현미경을 이용해 발광을 측정, 삼각 피라미드의 꼭지점에 양자점이 안정적으로 형성되었음을 확인했고, 시간에 따른 광자 간 상관관계 측정을 통해 양자광이 방출되는 것을 실험적으로 관측했다.

또한, 성장된 양자점의 비대칭성 정도를 가늠할 수 있는 양자광의 편광도와 미세구조 분리 정도를 측정해 높은 대칭성을 갖는 삼각 양자점이 형성되었음을 실험적으로 확인했으며, 이를 이론적 계산 결과와 비교함으로써 측정 결과의 타당성을 확보했다.

이번 연구에서는 기존에 질화물 반도체 양자점의 비대칭성과 높은 편광도를 이용해 상온 단일광자 방출기 제작에 집중해 오던 방식에서 벗어나, 양자점의 대칭성을 정밀하게 조절해 편광얽힘 광자쌍 방출기로도 응용 가능함을 제안했다. 또한 범용 반도체 박막 증착장비와 미세 패턴 기술을 사용했기 때문에 산업적인 측면에서 확장성이 높을 것으로 기대된다.

연구를 주도한 조용훈 교수는 "반도체 양자점을 제작하는 과정에서 발생하는 양자점의 비대칭성을 효과적으로 제어하여 양자점 내부의 미세 에너지 구조를 정교하게 조절할 수 있음을 보여준 결과”라며, “상온에서도 동작이 가능한 질소화합물 반도체 양자점을 이용해 편광얽힘 광자쌍 방출소자와 같은 차세대 양자광원 개발에 활용될 수 있을 것”이라고 의미를 말했다.

우리 대학 물리학과 여환섭 박사가 제1 저자로 참여한 이번 연구 결과는 삼성미래기술육성사업 등의 지원을 받아 수행됐으며, 나노분야 국제 학술지인 `나노 레터스(Nano Letters)' 12월 9일 字에 보충 표지와 함께 정식 출간됐다. (논문명: Control of 3-fold symmetric shape of group III-nitride quantum dots: Suppression of fine structure splitting / 질소화합물 반도체 양자점의 삼각 대칭적 모양 제어: 미세구조 분리현상의 완화)

2020.12.14 조회수 52083 -

메모리-중심 인공지능 가속기 시스템 개발

삼성미래기술육성재단이 지원한 우리 대학 연구진이 세계 최초로 `프로세싱-인-메모리(Processing-In-Memory, 이하 PIM)' 기술을 기반으로 한 인공지능 추천시스템 학습 알고리즘 가속에 최적화된 지능형 반도체 시스템 개발에 성공했다.

전기및전자공학부 유민수 교수 연구팀은 PIM 기술 기반의 메모리-중심 인공지능 가속기 반도체 시스템을 개발했다고 16일 밝혔다. 유 교수는 관련 분야에서 그동안의 탁월한 연구 성과를 인정받아 올해 아시아에서 유일하게 페이스북 패컬티 리서치 어워드(Facebook Faculty Research Award)를 수상했다.

인공지능 기술을 기반으로 고안된 추천시스템 알고리즘은 구글(Google), 페이스북(Facebook), 유튜브(YouTube), 아마존(Amazon) 등 빅테크 기업들이 콘텐츠 추천 및 개인 맞춤형 광고를 제작하는데 기반이 되는 핵심 인공지능 (AI) 기술이다. 온라인 광고를 통한 수입은 구글과 페이스북과 같은 실리콘밸리의 빅테크 기업의 주 수익 모델인 만큼 고도화된 추천 인공지능 기술에 대한 수요는 최근 들어 급상승하는 추세다.

페이스북이 최근 공개한 자료에 따르면 페이스북 데이터센터에서 처리되는 인공지능 연산의 70%가 추천 알고리즘을 처리하는 데에 사용되며, 인공지능 알고리즘 학습을 위한 컴퓨팅 자원의 50%를 추천 알고리즘을 학습하는 데 사용하고 있다.

유민수 교수 연구팀은 최근 메모리 반도체에 인공지능 연산 기능이 추가된 프로세싱-인-메모리(PIM) 기술 기반의 지능형 반도체 시스템을 개발하는 데 성공했다. 유 교수팀이 개발한 이 시스템은 인공지능 추천시스템 알고리즘의 학습 과정을 엔비디아(NVIDIA)의 그래픽카드(GPU)를 사용하는 기존 인공지능 가속 시스템 대비 최대 21배까지 빠르다고 연구팀 관계자는 설명했다.

지능형 메모리 반도체 기술은 우리나라의 AI 반도체 세계시장 공략을 위한 핵심기술로 주목받고 있다. 특히 정부에서도 `AI 종합 반도체 강국 실현'이라는 비전 아래 막대한 국가적 투자를 아끼지 않는 핵심 투자 분야다. 따라서 유 교수팀의 연구 성과는 향후 막대한 수요와 급성장이 예상되는 세계 AI 반도체 시장에서 메모리-중심으로 설계된 PIM 기술의 상용화 및 성공 가능성을 시사한다는 점에서 의미가 크다고 전문가들은 평가하고 있다.

유민수 교수는 서강대와 KAIST에서 각각 학사와 석사를 거쳐 미국 텍사스 오스틴 주립대에서 박사학위를 취득한 후 지난 2014년 인공지능 컴퓨팅 기술 기업인 미국 엔비디아(NVIDIA) 본사에 입사했다. 엔비디아에 입사한 이후 줄곧 인공지능 컴퓨팅 가속을 위한 다양한 하드웨어 및 소프트웨어 시스템 연구를 주도했으며 지난 2018년부터 우리 대학 전기및전자공학부 교수로 재직 중이다.

전기및전자공학부 권영은 박사과정이 제1 저자, 이윤재 석사과정이 제2 저자로 참여한 이번 연구 결과는 세계 최초의 추천시스템 학습용 가속기 시스템 개발 성과라는 학술 가치를 인정받아 컴퓨터 시스템 구조 분야 최우수 국제 학술대회인 IEEE International Symposium on High-Performance Computer Architecture(HPCA)에서 `Tensor Casting: Co-Designing Algorithm-Architecture for Personalized Recommendation Training' 이라는 논문 제목으로 내년 2월에 발표된다.

2020.11.16 조회수 36337

메모리-중심 인공지능 가속기 시스템 개발

삼성미래기술육성재단이 지원한 우리 대학 연구진이 세계 최초로 `프로세싱-인-메모리(Processing-In-Memory, 이하 PIM)' 기술을 기반으로 한 인공지능 추천시스템 학습 알고리즘 가속에 최적화된 지능형 반도체 시스템 개발에 성공했다.

전기및전자공학부 유민수 교수 연구팀은 PIM 기술 기반의 메모리-중심 인공지능 가속기 반도체 시스템을 개발했다고 16일 밝혔다. 유 교수는 관련 분야에서 그동안의 탁월한 연구 성과를 인정받아 올해 아시아에서 유일하게 페이스북 패컬티 리서치 어워드(Facebook Faculty Research Award)를 수상했다.

인공지능 기술을 기반으로 고안된 추천시스템 알고리즘은 구글(Google), 페이스북(Facebook), 유튜브(YouTube), 아마존(Amazon) 등 빅테크 기업들이 콘텐츠 추천 및 개인 맞춤형 광고를 제작하는데 기반이 되는 핵심 인공지능 (AI) 기술이다. 온라인 광고를 통한 수입은 구글과 페이스북과 같은 실리콘밸리의 빅테크 기업의 주 수익 모델인 만큼 고도화된 추천 인공지능 기술에 대한 수요는 최근 들어 급상승하는 추세다.

페이스북이 최근 공개한 자료에 따르면 페이스북 데이터센터에서 처리되는 인공지능 연산의 70%가 추천 알고리즘을 처리하는 데에 사용되며, 인공지능 알고리즘 학습을 위한 컴퓨팅 자원의 50%를 추천 알고리즘을 학습하는 데 사용하고 있다.

유민수 교수 연구팀은 최근 메모리 반도체에 인공지능 연산 기능이 추가된 프로세싱-인-메모리(PIM) 기술 기반의 지능형 반도체 시스템을 개발하는 데 성공했다. 유 교수팀이 개발한 이 시스템은 인공지능 추천시스템 알고리즘의 학습 과정을 엔비디아(NVIDIA)의 그래픽카드(GPU)를 사용하는 기존 인공지능 가속 시스템 대비 최대 21배까지 빠르다고 연구팀 관계자는 설명했다.

지능형 메모리 반도체 기술은 우리나라의 AI 반도체 세계시장 공략을 위한 핵심기술로 주목받고 있다. 특히 정부에서도 `AI 종합 반도체 강국 실현'이라는 비전 아래 막대한 국가적 투자를 아끼지 않는 핵심 투자 분야다. 따라서 유 교수팀의 연구 성과는 향후 막대한 수요와 급성장이 예상되는 세계 AI 반도체 시장에서 메모리-중심으로 설계된 PIM 기술의 상용화 및 성공 가능성을 시사한다는 점에서 의미가 크다고 전문가들은 평가하고 있다.

유민수 교수는 서강대와 KAIST에서 각각 학사와 석사를 거쳐 미국 텍사스 오스틴 주립대에서 박사학위를 취득한 후 지난 2014년 인공지능 컴퓨팅 기술 기업인 미국 엔비디아(NVIDIA) 본사에 입사했다. 엔비디아에 입사한 이후 줄곧 인공지능 컴퓨팅 가속을 위한 다양한 하드웨어 및 소프트웨어 시스템 연구를 주도했으며 지난 2018년부터 우리 대학 전기및전자공학부 교수로 재직 중이다.

전기및전자공학부 권영은 박사과정이 제1 저자, 이윤재 석사과정이 제2 저자로 참여한 이번 연구 결과는 세계 최초의 추천시스템 학습용 가속기 시스템 개발 성과라는 학술 가치를 인정받아 컴퓨터 시스템 구조 분야 최우수 국제 학술대회인 IEEE International Symposium on High-Performance Computer Architecture(HPCA)에서 `Tensor Casting: Co-Designing Algorithm-Architecture for Personalized Recommendation Training' 이라는 논문 제목으로 내년 2월에 발표된다.

2020.11.16 조회수 36337