%EA%B3%A0%EC%A7%91%EC%A0%81

-

강유전체 활용 차세대 반도체 메모리 혁신

강유전체는 메모리 소자에서 전하를 잘 저장하기 때문에 "전기를 기억하는 소재"와 같다는 특성으로 차세대 반도체 기술 개발에 있어 핵심 소재로 부각되고 있다. 우리 연구진이 이러한 강유전체 소재를 활용해 현재 메모리 반도체 산업의 양대 산맥인 디램(DRAM)과 낸드 플래시(NAND Flash) 메모리의 한계를 극복한 고성능, 고집적 차세대 메모리 소자를 개발하는데 성공했다.

우리 대학 전상훈 교수 연구팀이 하프니아 강유전체 소재*를 활용한 차세대 메모리 및 스토리지 메모리 기술을 개발했다고 6일 밝혔다.

*하프니아 강유전체 소재: 비휘발성 절연막으로, CMOS 공정 호환성, 동작 속도, 내구성 등의 우수한 물리적 특성을 바탕으로 차세대 반도체의 핵심 소재로 활발하게 연구되고 있는 물질

디램 메모리는 우리가 스마트폰, 컴퓨터, USB 등에서 사용하는 데이터를 저장하는 휘발성 메모리다. 휘발성 특성으로 인해, 외부 전력이 끊어지면 저장된 데이터가 손실되지만, 공정 단가가 낮고 집적도가 높아 메인 메모리로 활용돼 왔다. 하지만 디램 메모리 기술은 소자의 크기가 작아질수록 디램 소자가 정보를 저장하는 저장 커패시터의 용량도 작아지게 되고, 더 이상 메모리 동작을 수행하기 어렵다.

연구팀은 저장 커패시터는 정보를 저장하는 디램 기술의 한계를 극복하고자 이러한 저장 커패시터가 물리적으로 작은 면적에서도 높은 저장 용량을 달성할 수 있도록 개선하는 데에 집중했다. 이를 위해 하프니아 강유전체 기반 극박막의 고유전율 물질을 개발했다. 연구 결과 현재까지 보고된 디램 커패시터 중, 가장 낮은 2.4 Å (머리카락 굵기의 약 10만분의 1)의 SiO2(실리콘 산화물) 유효 두께와 같이 얇은 층에 저장하는 것을 달성했다.

또한 연구팀은 디램 메모리 기술을 잠재적으로 대체할 수 있는 후보군으로 주목받고 있는 강유전체 메모리 FRAM 메모리도 개발하였다. 현 DRAM 수준의 1V 이하의 낮은 전압에서도 비 휘발성 정보 저장과 삭제가 확실히 이루어지는 기술은 에너지 효율성을 크게 향상시켜 차세대 메모리에 필수적이다.

디램 메모리 기술에 이어 연구팀은 낸드 플래시 메모리의 한계를 극복할 하프니아 강유전체 기반의 차세대 메모리 기술을 개발했다. 낸드 플래시 메모리는 우리가 스마트폰, 컴퓨터, USB 등에서 사용하는 데이터를 저장하는 비휘발성 메모리이다. 현재, 낸드플래시 메모리의 저장 용량을 늘리기 위해 여러 층을 쌓아 올리는 방식으로 발전해 왔지만, 물리적인 한계로 인해 500층, 1000층 이상으로 쌓기가 어려운 상황이다.

이에 연구팀은 강유전체라는 새로운 소재를 낸드 플래시에 적용하는 방식을 연구한 결과, 소재 계면에 TiO2 층이라는 얇은 층을 추가함으로써 1000단 이상의 수직 적층 3차원이며 외부 환경의 간섭에도 데이터를 안정적으로 유지하도록 설계했다.

마지막으로 기존의 낸드 플래시 기술에서 산화물 채널 기반의 메모리 소자는 데이터를 완전히 지울 수 없는 한계가 있어 새로운 구조의 고성능 산화물 채널 기반 낸드 플래시 소자를 개발하는 데 성공했다. 이 소자는 더 많은 데이터를 저장할 수 있고 데이터를 10년 이상 안정적으로 보존할 수 있는 특징을 가진다.

전상훈 교수는 “이번 연구 결과들은 스케일링 이슈로 인해 답보상태에 있는 메모리 반도체 기술 개발에 돌파구가 되는 기술이 될 것으로 판단되며, 향후 다양한 인공지능 컴퓨팅 및 엣지 컴퓨팅 기술 상용화에 기여할 수 있을 것”이라고 설명했다.

벤카테스왈루 가담(Venkateswarlu Gaddam) 연구 교수, 김기욱 박사 과정, 조홍래 박사 과정, 황정현 박사 과정, 이상호 박사 과정, 최효준 석사 과정, 강현준 석사 과정이 공동 제1 저자로 참여했고 이러한 연구 성과를 국제적으로 인정받아 반도체 산업계 최고 수준의(Top-tier) 컨퍼런스에 2024년 5편의 논문을 발표했다. (2024 VLSI 2편, 2024 IEDM 3편)

- In-depth analysis of the Hafnia ferroelectrics as a key enabler for low voltage & QLC 3D VNAND beyond 1K layers: Experimental demonstration and modeling VLSI 24 DOI: 10.1109/VLSITechnologyandCir46783.2024

- Low-Damage Processed and High-Pressure Annealed High-k Hafnium Zirconium Oxide Capacitors near Morphotropic Phase Boundary with Record-Low EOT of 2.4 Å & high-k of 70 for DRAM … VLSI 24 DOI: 10.1109/VLSITechnologyandCir46783.2024

- Unveiling the Origin of Disturbance in FeFET and the Potential of Multifunctional TiO2 as a Breakthrough for Disturb-free 3D NAND Cell: Experimental and Modeling https://iedm24.mapyourshow.com/8_0/sessions/session-details.cfm?scheduleid=4

- Oxide Channel Ferroelectric NAND Device with Source- tied Covering Metal Structure: Wide Memory Window (14.3 V), Reliable Retention (> 10 years) and Disturbance Immunity (△Vth ≤ 0.1 V) for QLC Operation

https://iedm24.mapyourshow.com/8_0/sessions/session-details.cfm?scheduleid=47

- Design Methodology for Low-Voltage Operational (≤1 V) FRAM Cell Capacitors and Approaches for Overcoming Disturb Issues in 1T-nC Arrays: Experimental & Modeling:

https://iedm24.mapyourshow.com/8_0/sessions/session-details.cfm?scheduleid=54

참고로, IEEE VLSI와 IEEE IEDM 학회는 삼성전자, SK 하이닉스, 마이크론, 인텔 등 굴지의 반도체 업계와 세계적인 석학들이 최신 기술 개발을 공유하고 미래 기술의 지향점을 논의하는 학회로 반도체 올림픽이라고 불린다.

한편, 이 연구는 삼성전자, 한양대학교와 협업을 통해서 수행되었으며, 한국산업기술평가원 (KEIT) 민관공동투자 반도체 고급인력양성사업, 과학기술정보통신부 혁신연구센터(IRC) 지원 사업, 삼성전자(Samsung Electronics)의 지원을 받아 진행됐다.

2025.01.06 조회수 5461

강유전체 활용 차세대 반도체 메모리 혁신

강유전체는 메모리 소자에서 전하를 잘 저장하기 때문에 "전기를 기억하는 소재"와 같다는 특성으로 차세대 반도체 기술 개발에 있어 핵심 소재로 부각되고 있다. 우리 연구진이 이러한 강유전체 소재를 활용해 현재 메모리 반도체 산업의 양대 산맥인 디램(DRAM)과 낸드 플래시(NAND Flash) 메모리의 한계를 극복한 고성능, 고집적 차세대 메모리 소자를 개발하는데 성공했다.

우리 대학 전상훈 교수 연구팀이 하프니아 강유전체 소재*를 활용한 차세대 메모리 및 스토리지 메모리 기술을 개발했다고 6일 밝혔다.

*하프니아 강유전체 소재: 비휘발성 절연막으로, CMOS 공정 호환성, 동작 속도, 내구성 등의 우수한 물리적 특성을 바탕으로 차세대 반도체의 핵심 소재로 활발하게 연구되고 있는 물질

디램 메모리는 우리가 스마트폰, 컴퓨터, USB 등에서 사용하는 데이터를 저장하는 휘발성 메모리다. 휘발성 특성으로 인해, 외부 전력이 끊어지면 저장된 데이터가 손실되지만, 공정 단가가 낮고 집적도가 높아 메인 메모리로 활용돼 왔다. 하지만 디램 메모리 기술은 소자의 크기가 작아질수록 디램 소자가 정보를 저장하는 저장 커패시터의 용량도 작아지게 되고, 더 이상 메모리 동작을 수행하기 어렵다.

연구팀은 저장 커패시터는 정보를 저장하는 디램 기술의 한계를 극복하고자 이러한 저장 커패시터가 물리적으로 작은 면적에서도 높은 저장 용량을 달성할 수 있도록 개선하는 데에 집중했다. 이를 위해 하프니아 강유전체 기반 극박막의 고유전율 물질을 개발했다. 연구 결과 현재까지 보고된 디램 커패시터 중, 가장 낮은 2.4 Å (머리카락 굵기의 약 10만분의 1)의 SiO2(실리콘 산화물) 유효 두께와 같이 얇은 층에 저장하는 것을 달성했다.

또한 연구팀은 디램 메모리 기술을 잠재적으로 대체할 수 있는 후보군으로 주목받고 있는 강유전체 메모리 FRAM 메모리도 개발하였다. 현 DRAM 수준의 1V 이하의 낮은 전압에서도 비 휘발성 정보 저장과 삭제가 확실히 이루어지는 기술은 에너지 효율성을 크게 향상시켜 차세대 메모리에 필수적이다.

디램 메모리 기술에 이어 연구팀은 낸드 플래시 메모리의 한계를 극복할 하프니아 강유전체 기반의 차세대 메모리 기술을 개발했다. 낸드 플래시 메모리는 우리가 스마트폰, 컴퓨터, USB 등에서 사용하는 데이터를 저장하는 비휘발성 메모리이다. 현재, 낸드플래시 메모리의 저장 용량을 늘리기 위해 여러 층을 쌓아 올리는 방식으로 발전해 왔지만, 물리적인 한계로 인해 500층, 1000층 이상으로 쌓기가 어려운 상황이다.

이에 연구팀은 강유전체라는 새로운 소재를 낸드 플래시에 적용하는 방식을 연구한 결과, 소재 계면에 TiO2 층이라는 얇은 층을 추가함으로써 1000단 이상의 수직 적층 3차원이며 외부 환경의 간섭에도 데이터를 안정적으로 유지하도록 설계했다.

마지막으로 기존의 낸드 플래시 기술에서 산화물 채널 기반의 메모리 소자는 데이터를 완전히 지울 수 없는 한계가 있어 새로운 구조의 고성능 산화물 채널 기반 낸드 플래시 소자를 개발하는 데 성공했다. 이 소자는 더 많은 데이터를 저장할 수 있고 데이터를 10년 이상 안정적으로 보존할 수 있는 특징을 가진다.

전상훈 교수는 “이번 연구 결과들은 스케일링 이슈로 인해 답보상태에 있는 메모리 반도체 기술 개발에 돌파구가 되는 기술이 될 것으로 판단되며, 향후 다양한 인공지능 컴퓨팅 및 엣지 컴퓨팅 기술 상용화에 기여할 수 있을 것”이라고 설명했다.

벤카테스왈루 가담(Venkateswarlu Gaddam) 연구 교수, 김기욱 박사 과정, 조홍래 박사 과정, 황정현 박사 과정, 이상호 박사 과정, 최효준 석사 과정, 강현준 석사 과정이 공동 제1 저자로 참여했고 이러한 연구 성과를 국제적으로 인정받아 반도체 산업계 최고 수준의(Top-tier) 컨퍼런스에 2024년 5편의 논문을 발표했다. (2024 VLSI 2편, 2024 IEDM 3편)

- In-depth analysis of the Hafnia ferroelectrics as a key enabler for low voltage & QLC 3D VNAND beyond 1K layers: Experimental demonstration and modeling VLSI 24 DOI: 10.1109/VLSITechnologyandCir46783.2024

- Low-Damage Processed and High-Pressure Annealed High-k Hafnium Zirconium Oxide Capacitors near Morphotropic Phase Boundary with Record-Low EOT of 2.4 Å & high-k of 70 for DRAM … VLSI 24 DOI: 10.1109/VLSITechnologyandCir46783.2024

- Unveiling the Origin of Disturbance in FeFET and the Potential of Multifunctional TiO2 as a Breakthrough for Disturb-free 3D NAND Cell: Experimental and Modeling https://iedm24.mapyourshow.com/8_0/sessions/session-details.cfm?scheduleid=4

- Oxide Channel Ferroelectric NAND Device with Source- tied Covering Metal Structure: Wide Memory Window (14.3 V), Reliable Retention (> 10 years) and Disturbance Immunity (△Vth ≤ 0.1 V) for QLC Operation

https://iedm24.mapyourshow.com/8_0/sessions/session-details.cfm?scheduleid=47

- Design Methodology for Low-Voltage Operational (≤1 V) FRAM Cell Capacitors and Approaches for Overcoming Disturb Issues in 1T-nC Arrays: Experimental & Modeling:

https://iedm24.mapyourshow.com/8_0/sessions/session-details.cfm?scheduleid=54

참고로, IEEE VLSI와 IEEE IEDM 학회는 삼성전자, SK 하이닉스, 마이크론, 인텔 등 굴지의 반도체 업계와 세계적인 석학들이 최신 기술 개발을 공유하고 미래 기술의 지향점을 논의하는 학회로 반도체 올림픽이라고 불린다.

한편, 이 연구는 삼성전자, 한양대학교와 협업을 통해서 수행되었으며, 한국산업기술평가원 (KEIT) 민관공동투자 반도체 고급인력양성사업, 과학기술정보통신부 혁신연구센터(IRC) 지원 사업, 삼성전자(Samsung Electronics)의 지원을 받아 진행됐다.

2025.01.06 조회수 5461 -

인간의 뇌를 모방한 뉴로모픽 반도체 개발

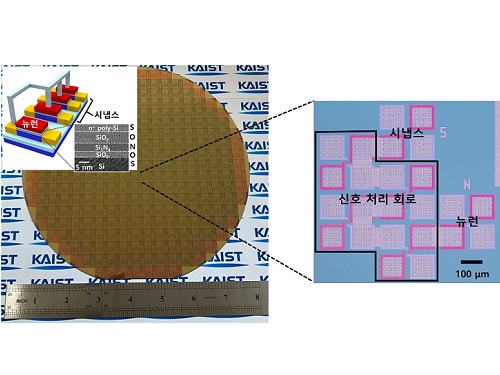

우리 대학 전기및전자공학부 최양규, 최성율 교수 공동연구팀이 인간의 뇌를 모방한 고집적 뉴로모픽 반도체를 개발했다고 5일 밝혔다.

뉴로모픽(neuromorphic) 하드웨어는, 인간의 뇌가 매우 복잡한 기능을 수행하지만 소비하는 에너지는 20와트(W) 밖에 되지 않는다는 것에 착안해, 인간의 뇌를 모방해 인공지능 기능을 하드웨어로 구현하는 방식이다. 뉴로모픽 하드웨어는 기존의 폰 노이만(von Neumann) 방식과 다르게 인공지능 기능을 초저전력으로 수행할 수 있어 많은 주목을 받고 있다.

공동연구팀은 단일 트랜지스터를 이용해 인간의 뇌를 모방한 뉴런과 시냅스로 구성된 뉴로모픽 반도체를 구현했다. 이 반도체는 상용화된 실리콘 표준 공정으로 제작되어, 뉴로모픽 하드웨어 시스템의 상용화 가능성을 획기적으로 높였다.

우리 대학 전기및전자공학부 한준규 박사과정이 제1 저자로, 같은 학부 오정엽 박사과정이 제2 저자로 참여한 이번 연구는 저명 국제 학술지 `사이언스 어드벤시스(Science Advances)' 8월 온라인판에 출판됐다. (논문명 : Co-integration of single transistor neurons and synapses by nanoscale CMOS fabrication for highly scalable neuromorphic hardware).

뉴로모픽 하드웨어를 구현하기 위해서는, 생물학적 뇌와 동일하게 일정 신호가 통합되었을 때 스파이크를 발생하는 뉴런과 두 뉴런 사이의 연결성을 기억하는 시냅스가 필요하다. 하지만, 디지털 또는 아날로그 회로를 기반으로 구성된 뉴런과 시냅스는 큰 면적을 차지하기 때문에 집적도 측면에서 한계가 있다. 인간의 뇌가 약 천억 개(1011)의 뉴런과 백조 개(1014)의 시냅스로 구성된다는 점에서, 실제 모바일 및 사물인터넷(IoT) 장치에 사용되기 위해서는 집적도를 개선할 필요가 있다.

이를 개선하기 위해 다양한 소재 및 구조 기반의 뉴런과 시냅스가 제안되었지만, 대부분 표준 실리콘 미세 공정 기술로 제작될 수 없어 상용화가 어렵고 양산 적용에 문제가 많았다.

연구팀은 문제 해결을 위해 이미 널리 쓰이고 있는 표준 실리콘 미세 공정 기술로 제작될 수 있는 단일 트랜지스터로 생물학적 뉴런과 시냅스의 동작을 모방했으며, 이를 동일 웨이퍼(8 인치) 상에 동시 집적해 뉴로모픽 반도체를 제작했다.

제작된 뉴로모픽 트랜지스터는 현재 양산되고 있는 메모리 및 시스템 반도체용 트랜지스터와 같은 구조로, 트랜지스터가 메모리 기능 및 논리 연산을 수행하는 것은 물론, 새로운 뉴로모픽 동작이 가능함을 실험적으로 보여 준 것에 가장 큰 의미가 있다. 기존 양산 트랜지스터에 새로운 동작원리를 적용해, 구조는 같으나 기능이 전혀 다른 뉴로모픽 트랜지스터를 제작했다. 뉴로모픽 트랜지스터는 마치 동전에 앞면과 뒷면이 동시에 있는 것처럼, 뉴런 기능도 하고 시냅스 기능도 수행하는 야누스(Janus) 구조로 구현 가능함을 세계 최초로 입증했다.

연구팀의 기술은 복잡한 디지털 및 아날로그 회로를 기반으로 구성되던 뉴런을 단일 트랜지스터로 대체 구현해 집적도를 획기적으로 높였고, 더 나아가 같은 구조의 시냅스와 함께 집적해 공정 단순화에 따른 비용 절감을 할 수 있는 신기술이다. 기존 뉴런 회로 구성에 필요한 평면적이 21,000 단위인 반면, 새로 개발된 뉴로모픽 트랜지스터는 6 단위 이하이므로 집적도가 약 3,500 배 이상 높다.

연구팀은 제작된 뉴로모픽 반도체를 바탕으로 증폭 이득 조절, 동시성 판단 등의 뇌의 기능을 일부 모방했고, 글자 이미지 및 얼굴 이미지 인식이 가능함을 보였다.

연구팀이 개발한 뉴로모픽 반도체는 집적도 개선과 비용 절감 등에 이바지하며, 뉴로모픽 하드웨어의 상용화를 앞당길 수 있을 것으로 기대된다.

한준규 박사과정은 "상보성 금속 산화막 반도체(CMOS) 기반 단일 트랜지스터를 이용해 뉴런과 시냅스 동작이 가능함을 보였다ˮ 라며 "상용화된 CMOS 공정을 이용해 뉴런, 시냅스, 그리고 부가적인 신호 처리 회로를 동일 웨이퍼 상에 동시에 집적함으로써, 뉴로모픽 반도체의 집적도를 개선했고, 이는 뉴로모픽 하드웨어의 상용화를 한 단계 앞당길 수 있을 것이다ˮ 라고 말했다.

한편 이번 연구는 한국연구재단 차세대지능형반도체기술개발사업, 중견연구사업, 미래반도체사업 및 반도체설계교육센터의 지원을 받아 수행됐다.

2021.08.06 조회수 14958

인간의 뇌를 모방한 뉴로모픽 반도체 개발

우리 대학 전기및전자공학부 최양규, 최성율 교수 공동연구팀이 인간의 뇌를 모방한 고집적 뉴로모픽 반도체를 개발했다고 5일 밝혔다.

뉴로모픽(neuromorphic) 하드웨어는, 인간의 뇌가 매우 복잡한 기능을 수행하지만 소비하는 에너지는 20와트(W) 밖에 되지 않는다는 것에 착안해, 인간의 뇌를 모방해 인공지능 기능을 하드웨어로 구현하는 방식이다. 뉴로모픽 하드웨어는 기존의 폰 노이만(von Neumann) 방식과 다르게 인공지능 기능을 초저전력으로 수행할 수 있어 많은 주목을 받고 있다.

공동연구팀은 단일 트랜지스터를 이용해 인간의 뇌를 모방한 뉴런과 시냅스로 구성된 뉴로모픽 반도체를 구현했다. 이 반도체는 상용화된 실리콘 표준 공정으로 제작되어, 뉴로모픽 하드웨어 시스템의 상용화 가능성을 획기적으로 높였다.

우리 대학 전기및전자공학부 한준규 박사과정이 제1 저자로, 같은 학부 오정엽 박사과정이 제2 저자로 참여한 이번 연구는 저명 국제 학술지 `사이언스 어드벤시스(Science Advances)' 8월 온라인판에 출판됐다. (논문명 : Co-integration of single transistor neurons and synapses by nanoscale CMOS fabrication for highly scalable neuromorphic hardware).

뉴로모픽 하드웨어를 구현하기 위해서는, 생물학적 뇌와 동일하게 일정 신호가 통합되었을 때 스파이크를 발생하는 뉴런과 두 뉴런 사이의 연결성을 기억하는 시냅스가 필요하다. 하지만, 디지털 또는 아날로그 회로를 기반으로 구성된 뉴런과 시냅스는 큰 면적을 차지하기 때문에 집적도 측면에서 한계가 있다. 인간의 뇌가 약 천억 개(1011)의 뉴런과 백조 개(1014)의 시냅스로 구성된다는 점에서, 실제 모바일 및 사물인터넷(IoT) 장치에 사용되기 위해서는 집적도를 개선할 필요가 있다.

이를 개선하기 위해 다양한 소재 및 구조 기반의 뉴런과 시냅스가 제안되었지만, 대부분 표준 실리콘 미세 공정 기술로 제작될 수 없어 상용화가 어렵고 양산 적용에 문제가 많았다.

연구팀은 문제 해결을 위해 이미 널리 쓰이고 있는 표준 실리콘 미세 공정 기술로 제작될 수 있는 단일 트랜지스터로 생물학적 뉴런과 시냅스의 동작을 모방했으며, 이를 동일 웨이퍼(8 인치) 상에 동시 집적해 뉴로모픽 반도체를 제작했다.

제작된 뉴로모픽 트랜지스터는 현재 양산되고 있는 메모리 및 시스템 반도체용 트랜지스터와 같은 구조로, 트랜지스터가 메모리 기능 및 논리 연산을 수행하는 것은 물론, 새로운 뉴로모픽 동작이 가능함을 실험적으로 보여 준 것에 가장 큰 의미가 있다. 기존 양산 트랜지스터에 새로운 동작원리를 적용해, 구조는 같으나 기능이 전혀 다른 뉴로모픽 트랜지스터를 제작했다. 뉴로모픽 트랜지스터는 마치 동전에 앞면과 뒷면이 동시에 있는 것처럼, 뉴런 기능도 하고 시냅스 기능도 수행하는 야누스(Janus) 구조로 구현 가능함을 세계 최초로 입증했다.

연구팀의 기술은 복잡한 디지털 및 아날로그 회로를 기반으로 구성되던 뉴런을 단일 트랜지스터로 대체 구현해 집적도를 획기적으로 높였고, 더 나아가 같은 구조의 시냅스와 함께 집적해 공정 단순화에 따른 비용 절감을 할 수 있는 신기술이다. 기존 뉴런 회로 구성에 필요한 평면적이 21,000 단위인 반면, 새로 개발된 뉴로모픽 트랜지스터는 6 단위 이하이므로 집적도가 약 3,500 배 이상 높다.

연구팀은 제작된 뉴로모픽 반도체를 바탕으로 증폭 이득 조절, 동시성 판단 등의 뇌의 기능을 일부 모방했고, 글자 이미지 및 얼굴 이미지 인식이 가능함을 보였다.

연구팀이 개발한 뉴로모픽 반도체는 집적도 개선과 비용 절감 등에 이바지하며, 뉴로모픽 하드웨어의 상용화를 앞당길 수 있을 것으로 기대된다.

한준규 박사과정은 "상보성 금속 산화막 반도체(CMOS) 기반 단일 트랜지스터를 이용해 뉴런과 시냅스 동작이 가능함을 보였다ˮ 라며 "상용화된 CMOS 공정을 이용해 뉴런, 시냅스, 그리고 부가적인 신호 처리 회로를 동일 웨이퍼 상에 동시에 집적함으로써, 뉴로모픽 반도체의 집적도를 개선했고, 이는 뉴로모픽 하드웨어의 상용화를 한 단계 앞당길 수 있을 것이다ˮ 라고 말했다.

한편 이번 연구는 한국연구재단 차세대지능형반도체기술개발사업, 중견연구사업, 미래반도체사업 및 반도체설계교육센터의 지원을 받아 수행됐다.

2021.08.06 조회수 14958 -

이건재 교수, 유연고집적회로의 연속적패키징 기술 개발

〈 이 건 재 교수 〉

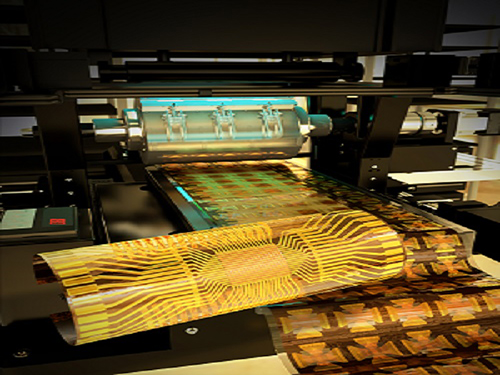

우리 대학 신소재공학과 이건재 교수와 한국기계연구원 김재현 박사 공동 연구팀이 롤 기반 공정을 통해 플렉서블 기기의 핵심기술인 유연 고집적회로를 연속적으로 패키징(소자와 전자기기를 연결하는 전기적 포장) 및 전사(轉寫)할 수 있는 기술을 개발했다.

또한 개발된 롤 기반 전사 및 패키징 기술을 유연 낸드플래시 메모리(전원이 끊겨도 저장된 데이터를 잃어버리지 않는 비휘발성 메모리의 일종)에 적용하는데 성공했다.

이번 연구 결과는 재료과학 분야 학술지인 ‘어드밴스드 머티리얼즈(Advanced Materials)’ 7월 20일자 온라인 판에 게재됐다.

롤 공정(유연기판을 회전하는 롤에 감으며 동시에 공정을 진행하는 방식) 기반의 유연전자 생산기술은 높은 생산효율을 바탕으로 웨어러블 및 플렉서블 기기 상용화에 중요한 역할을 할 것으로 기대되고 있다.

그러나 지금까지는 고집적회로를 롤 공정으로 구현하는 방법 및 주변회로와 상호 연결하는 패키징 기술이 해결되지 않아 실용화에 한계가 있었다.

문제 해결을 위해 연구팀은 기존 반도체 공정을 이용해 실리콘 기판에 낸드 플래시 메모리를 형성한 후 수백 나노미터(10분의 1m) 두께로 얇게 만들었다.

그 후 개발한 롤 기반 전사 및 패키징 기술을 통해 소자를 유연기판에 옮기는 동시에 이방성 전도 필름을 이용해 상호 연결하는 기술을 구현했다.

연구팀의 최종적인 실리콘 기반 유연 낸드플래시 메모리는 반복적인 휘어짐에도 모든 기능이 정상적으로 동작했고 외부와의 상호연결도 매우 안정적으로 유지됐다.

개발된 롤 기반 유연 고집적회로 기술은 유연 어플리케이션 프로세서(AP), 고집적 메모리, 고속 통신소자 등의 양산에 응용 가능할 것으로 기대된다.

이 교수는 “높은 생산성을 지닌 롤 기반 전사 기술을 이용해 단결정 실리콘 박막 고집적회로를 유연한 인쇄회로 기판 위에 패키징하는 생산기술을 확보했다”며 “향후 유연 디스플레이 및 배터리 기술과 함께 휘어지는 컴퓨터 구현의 핵심 생산 기술이 될 것으로 기대된다”고 말했다.

김재현 박사는 “한국기계연구원이 보유한 롤 기반 전사 기술을 이용해 단결정 실리콘 고집적소자를 유연한 폴리머 인쇄회로 기판 상에 손상 없이 전사함과 동시에 소자와 인쇄회로기판이 전기적으로 연결되도록 하는 롤 기반의 생산 공정 기술을 개발하였다”며 “이 기술은 향후 고성능 전자 소자를 유연 기판 위에 형성해 사물인터넷 및 웨어러블용 고성능 전자기기를 제조하는 핵심 생산 기술이 될 것으로 전망한다.”라고 말했다.

이건재 교수는 2013년도에 0.18 씨모스(CMOS) 공정기반으로 컴퓨터의 두뇌에 해당하는 휘어지는 유연 고집적회로를 최초로 구현했다. 특히 반도체분야 최고 권위학회인 국제반도체소자학회(IEDM)에서 초청받아 발표하는 등 세계적인 주목을 받았다.

한국기계연구원 김재현 박사 연구팀은 2009년부터 롤 스탬프를 이용해 박막소자를 옮기는 기술을 연구하고 있다. 관련 롤 전사 장비 기술을 디스플레이 및 반도체 용도의 롤 장비 회사에 기술이전하기도 했다.

이번 연구는 2013년부터 진행된 한국기계연구원의 나노소재 응용 고성능 유연소자기술 기반구축사업의 일환으로 수행됐다. 이건재 교수는 교원창업을 통해 유연한 고집적회로 관련 기술 상용화를 계획 중이다.

□ 그림 설명

그림1. 연속 롤-패키징 공정의 개요 모식도

그림2. 제작된 유연 실리콘 낸드 플래시메모리

2016.09.01 조회수 19091

이건재 교수, 유연고집적회로의 연속적패키징 기술 개발

〈 이 건 재 교수 〉

우리 대학 신소재공학과 이건재 교수와 한국기계연구원 김재현 박사 공동 연구팀이 롤 기반 공정을 통해 플렉서블 기기의 핵심기술인 유연 고집적회로를 연속적으로 패키징(소자와 전자기기를 연결하는 전기적 포장) 및 전사(轉寫)할 수 있는 기술을 개발했다.

또한 개발된 롤 기반 전사 및 패키징 기술을 유연 낸드플래시 메모리(전원이 끊겨도 저장된 데이터를 잃어버리지 않는 비휘발성 메모리의 일종)에 적용하는데 성공했다.

이번 연구 결과는 재료과학 분야 학술지인 ‘어드밴스드 머티리얼즈(Advanced Materials)’ 7월 20일자 온라인 판에 게재됐다.

롤 공정(유연기판을 회전하는 롤에 감으며 동시에 공정을 진행하는 방식) 기반의 유연전자 생산기술은 높은 생산효율을 바탕으로 웨어러블 및 플렉서블 기기 상용화에 중요한 역할을 할 것으로 기대되고 있다.

그러나 지금까지는 고집적회로를 롤 공정으로 구현하는 방법 및 주변회로와 상호 연결하는 패키징 기술이 해결되지 않아 실용화에 한계가 있었다.

문제 해결을 위해 연구팀은 기존 반도체 공정을 이용해 실리콘 기판에 낸드 플래시 메모리를 형성한 후 수백 나노미터(10분의 1m) 두께로 얇게 만들었다.

그 후 개발한 롤 기반 전사 및 패키징 기술을 통해 소자를 유연기판에 옮기는 동시에 이방성 전도 필름을 이용해 상호 연결하는 기술을 구현했다.

연구팀의 최종적인 실리콘 기반 유연 낸드플래시 메모리는 반복적인 휘어짐에도 모든 기능이 정상적으로 동작했고 외부와의 상호연결도 매우 안정적으로 유지됐다.

개발된 롤 기반 유연 고집적회로 기술은 유연 어플리케이션 프로세서(AP), 고집적 메모리, 고속 통신소자 등의 양산에 응용 가능할 것으로 기대된다.

이 교수는 “높은 생산성을 지닌 롤 기반 전사 기술을 이용해 단결정 실리콘 박막 고집적회로를 유연한 인쇄회로 기판 위에 패키징하는 생산기술을 확보했다”며 “향후 유연 디스플레이 및 배터리 기술과 함께 휘어지는 컴퓨터 구현의 핵심 생산 기술이 될 것으로 기대된다”고 말했다.

김재현 박사는 “한국기계연구원이 보유한 롤 기반 전사 기술을 이용해 단결정 실리콘 고집적소자를 유연한 폴리머 인쇄회로 기판 상에 손상 없이 전사함과 동시에 소자와 인쇄회로기판이 전기적으로 연결되도록 하는 롤 기반의 생산 공정 기술을 개발하였다”며 “이 기술은 향후 고성능 전자 소자를 유연 기판 위에 형성해 사물인터넷 및 웨어러블용 고성능 전자기기를 제조하는 핵심 생산 기술이 될 것으로 전망한다.”라고 말했다.

이건재 교수는 2013년도에 0.18 씨모스(CMOS) 공정기반으로 컴퓨터의 두뇌에 해당하는 휘어지는 유연 고집적회로를 최초로 구현했다. 특히 반도체분야 최고 권위학회인 국제반도체소자학회(IEDM)에서 초청받아 발표하는 등 세계적인 주목을 받았다.

한국기계연구원 김재현 박사 연구팀은 2009년부터 롤 스탬프를 이용해 박막소자를 옮기는 기술을 연구하고 있다. 관련 롤 전사 장비 기술을 디스플레이 및 반도체 용도의 롤 장비 회사에 기술이전하기도 했다.

이번 연구는 2013년부터 진행된 한국기계연구원의 나노소재 응용 고성능 유연소자기술 기반구축사업의 일환으로 수행됐다. 이건재 교수는 교원창업을 통해 유연한 고집적회로 관련 기술 상용화를 계획 중이다.

□ 그림 설명

그림1. 연속 롤-패키징 공정의 개요 모식도

그림2. 제작된 유연 실리콘 낸드 플래시메모리

2016.09.01 조회수 19091 -

세계에서 가장 작은 나노전자소자 공동 개발

KAIST 최양규 교수팀 / 나노종합팹센터 공동 연구

새로운 구조의 3차원 3nm급 나노전자소자(FinFET) 공동개발

현재 반도체소자 기술의 한계를 극복하여 향후 세계 반도체 시장에서 유리한 입지 확보

KAIST (총장 로버트 러플린) 최양규 교수팀과 나노종합팹센터(소장 이희철)가 테라급 차세대 반도체소자에 적용 가능한 세계에서 가장 작은 새로운 구조의 3차원 3nm급 ‘나노전자소자(FinFET)’를 공동 개발하는데 성공했다

이번에 공동 개발한 나노전자소자는 게이트가 채널의 전면을 감싸고 있는 새로운 형태의 3차원 구조를 고안하여 3nm급 트랜지스터를 개발한 것이다.

이것은 기존의 실리콘 반도체 기술의 한계를 한단계 진전시킨 의미 있는 연구 결과이다.

칩의 집적도를 높이기 위한 5nm급 나노소자 구현은 기존의 실리콘 기술이 아닌 탄소나노튜브나 분자소자 등과 같은 신소재를 사용해야 할 것으로 예상되었으나, 본 연구 결과는 실리콘 기술만으로도 5nm급 이하 소자 구현이 가능하고 ‘무어의 법칙’이 향후 20년 이상 계속 유지될 수 있다는 가능성을 제시했다.

현재까지 발표된 세계에서 가장 작은 소자는 2003년 12월 일본 NEC가 국제전자소자회의(IEDM)에서 발표한 ‘표준형 2차원 평면 소자구조를 이용한 4nm 소자’로 알려져 있으나, 이는 누설 전류가 크고 동작 시 충분한 전류를 얻지 못하는 등 만족스러운 소자 특성을 얻지는 못했다.

그러나 공동 개발된 3차원 구조(게이트가 채널의 전면을 감싸고 있는 구조)는 NEC의 4nm 소자에 비해 소자의 크기가 작을 뿐만 아니라 ‘단채널 효과’가 크게 개선된 결과를 얻었다.

이번에 공동 개발된 나노소자는 프로세서나 테라급 DRAM, SRAM, 플래시 메모리 소자로 응용이 가능하며, 휴대인터넷, 동영상 회의, 입는 컴퓨터 등의 차세대 정보처리 기기의 필수부품으로 사용될 것으로 전망되며, 컴퓨터의 두뇌에 해당되는 마이크로프로세서에 이 나노소자를 적용할 경우 처리속도가 100GHz (현재보다 25배 빠름)를 넘을 수 있을 것으로 예상된다.

전체 반도체 시장의 연평균 성장률을 7%로 가정할 경우 그 시장 규모가 2015년에는 480조로 예상되는데, 이 중 공동 개발된 3nm급 3차원 소자가 약 35% 정도를 차지할 것으로 기대된다.

이번 공동 연구개발을 통하여 얻은 차세대 나노 집적회로의 원천기술 및 응용기술은 앞으로도 우리나라가 세계 반도체 시장에서 유리한 입지를 확보하는데 기여할 것으로 평가된다.

이번 연구 성과는 오는 6월 13일 미국 하와이에서 개막되는 권위적인 국제 학술회의인 “초고집적회로 국제학회(Symposium on VLSI Technology)”에서 발표될 예정이다.

앞으로 한국과학기술원과 나노종합팹센터는 공동 프로젝트를 통하여 단위소자뿐만 아니라 3nm FinFET 제작 기술을 응용한 아날로그 및 디지털 RF 회로 등에 접목하는 양산성에 대한 추가적인 연구를 계속 진행할 예정이다.

※ 1테라 NAND 플래시는 엄지 손톱만한 크기의 칩 속에 12,500년분의 신문기사와 50만곡의 MP3 파일, 1,250편의 DVD 영화를 저장할 수 있고, 나노소자 칩을 가로, 세로에 각각 10개씩 배열하여 휴대하면 한 사람이 일생동안 보고 들은 것을 모두 저장할 수 있는 용량

2006.03.17 조회수 22370

세계에서 가장 작은 나노전자소자 공동 개발

KAIST 최양규 교수팀 / 나노종합팹센터 공동 연구

새로운 구조의 3차원 3nm급 나노전자소자(FinFET) 공동개발

현재 반도체소자 기술의 한계를 극복하여 향후 세계 반도체 시장에서 유리한 입지 확보

KAIST (총장 로버트 러플린) 최양규 교수팀과 나노종합팹센터(소장 이희철)가 테라급 차세대 반도체소자에 적용 가능한 세계에서 가장 작은 새로운 구조의 3차원 3nm급 ‘나노전자소자(FinFET)’를 공동 개발하는데 성공했다

이번에 공동 개발한 나노전자소자는 게이트가 채널의 전면을 감싸고 있는 새로운 형태의 3차원 구조를 고안하여 3nm급 트랜지스터를 개발한 것이다.

이것은 기존의 실리콘 반도체 기술의 한계를 한단계 진전시킨 의미 있는 연구 결과이다.

칩의 집적도를 높이기 위한 5nm급 나노소자 구현은 기존의 실리콘 기술이 아닌 탄소나노튜브나 분자소자 등과 같은 신소재를 사용해야 할 것으로 예상되었으나, 본 연구 결과는 실리콘 기술만으로도 5nm급 이하 소자 구현이 가능하고 ‘무어의 법칙’이 향후 20년 이상 계속 유지될 수 있다는 가능성을 제시했다.

현재까지 발표된 세계에서 가장 작은 소자는 2003년 12월 일본 NEC가 국제전자소자회의(IEDM)에서 발표한 ‘표준형 2차원 평면 소자구조를 이용한 4nm 소자’로 알려져 있으나, 이는 누설 전류가 크고 동작 시 충분한 전류를 얻지 못하는 등 만족스러운 소자 특성을 얻지는 못했다.

그러나 공동 개발된 3차원 구조(게이트가 채널의 전면을 감싸고 있는 구조)는 NEC의 4nm 소자에 비해 소자의 크기가 작을 뿐만 아니라 ‘단채널 효과’가 크게 개선된 결과를 얻었다.

이번에 공동 개발된 나노소자는 프로세서나 테라급 DRAM, SRAM, 플래시 메모리 소자로 응용이 가능하며, 휴대인터넷, 동영상 회의, 입는 컴퓨터 등의 차세대 정보처리 기기의 필수부품으로 사용될 것으로 전망되며, 컴퓨터의 두뇌에 해당되는 마이크로프로세서에 이 나노소자를 적용할 경우 처리속도가 100GHz (현재보다 25배 빠름)를 넘을 수 있을 것으로 예상된다.

전체 반도체 시장의 연평균 성장률을 7%로 가정할 경우 그 시장 규모가 2015년에는 480조로 예상되는데, 이 중 공동 개발된 3nm급 3차원 소자가 약 35% 정도를 차지할 것으로 기대된다.

이번 공동 연구개발을 통하여 얻은 차세대 나노 집적회로의 원천기술 및 응용기술은 앞으로도 우리나라가 세계 반도체 시장에서 유리한 입지를 확보하는데 기여할 것으로 평가된다.

이번 연구 성과는 오는 6월 13일 미국 하와이에서 개막되는 권위적인 국제 학술회의인 “초고집적회로 국제학회(Symposium on VLSI Technology)”에서 발표될 예정이다.

앞으로 한국과학기술원과 나노종합팹센터는 공동 프로젝트를 통하여 단위소자뿐만 아니라 3nm FinFET 제작 기술을 응용한 아날로그 및 디지털 RF 회로 등에 접목하는 양산성에 대한 추가적인 연구를 계속 진행할 예정이다.

※ 1테라 NAND 플래시는 엄지 손톱만한 크기의 칩 속에 12,500년분의 신문기사와 50만곡의 MP3 파일, 1,250편의 DVD 영화를 저장할 수 있고, 나노소자 칩을 가로, 세로에 각각 10개씩 배열하여 휴대하면 한 사람이 일생동안 보고 들은 것을 모두 저장할 수 있는 용량

2006.03.17 조회수 22370