%EB%A9%94%EB%AA%A8%EB%A6%AC

-

췌장 등 생체조직 고해상도 홀로토모그래피 성공

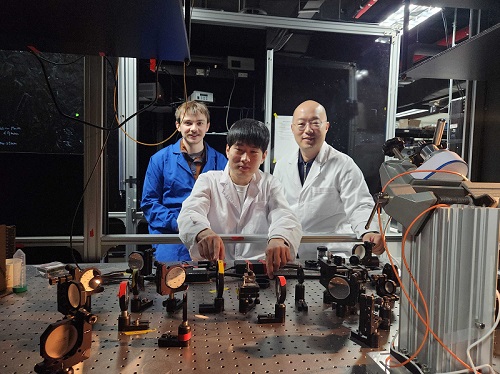

기존 광학 기술은 두꺼운 생체 조직을 관찰할 때, 조직 내부에서 발생하는 빛의 산란으로 인해 광학적 수차(aberration)가 생기고, 이로 인해 영상 품질이 저하되는 한계가 있었다. 우리 연구진이 디지털 수차 보정 기술을 개발하여 두꺼운 생체 조직의 3차원 영상을 정밀하게 관찰할 수 있는 기술을 개발했다.

우리 대학 물리학과 박용근 교수 연구팀이 별도의 염색 없이 두꺼운 생체 조직의 3차원 영상을 고해상도로 관찰할 수 있는 디지털 수차 보정 기술을 개발했다고 5일 밝혔다.

연구팀은 광학적 메모리 효과(optical memory effect)*를 활용해 두꺼운 생체 조직을 실시간으로 고해상도로 관찰하는 기술을 개발했다. 이 기술은 기존 적응형 광학(adaptive optics) 기술보다 더욱 강력한 보정 효과를 제공하여, 생체 조직 내부의 구조를 보다 선명하게 포착할 수 있다.

☞광학적 메모리 효과: 빛이 기울어질 때, 산란된 빛도 함께 기울어지는 현상으로, 생체 조직과 같은 복잡한 산란 매질에서도 관찰 가능함.

새롭게 개발된 기법을 적용한 결과, 연구진은 생체 조직 내부의 세포 구조를 더욱 세밀하게 관찰할 수 있었으며, 마이크로미터 크기의 시료에서 발생하는 동적 변화를 실시간으로 포착하는 데 성공했다.

이번 연구는 조직 병리학, 신약 개발, 생물학 연구 등 다양한 분야에서 활용될 수 있는 새로운 이미징 기술을 제시했으며, 기존 기술이 극복하지 못한 심층 조직 이미징의 한계를 뛰어넘는 성과로 평가괸다. 이를 통해 생명과학 및 의료 분야에서 큰 기여를 할 것으로 기대된다.

박용근 교수는 “이번 연구는 기존 이미징 기술의 한계를 극복하는 새로운 접근 방식으로, 홀로토모그래피 기반 비침습적 생체 이미징 및 진단 연구에 큰 영향을 미칠 것이다. 앞으로는 생체 조직의 더욱 정밀한 3차원 이미징을 통해 세포 수준에서의 다양한 생명현상을 이해하는 연구를 지속할 계획”이라고 말했다.

물리학과 오철민 석박사통합과정 학생이 제1 저자인 이번 연구 결과는 지난 2월 17일 국제 학술지 ‘네이처 커뮤니케이션즈(Nature communications)’에 온라인 게재됐으며, 해당 기술은 다양한 생명과학 분야에서의 적용 가능성을 인정받고 있다.

(논문명: Digital aberration correction for enhanced thick tissue imaging exploiting aberration matrix and tilt-tilt correlation from the optical memory effect) DOI: 10.1038/s41467-025-56865-z

이번 연구는 한국연구재단 리더연구사업 및 한국산업기술진흥원 글로벌산업기술협력센터사업의 지원을 받아 수행됐다.

2025.03.05 조회수 3749

췌장 등 생체조직 고해상도 홀로토모그래피 성공

기존 광학 기술은 두꺼운 생체 조직을 관찰할 때, 조직 내부에서 발생하는 빛의 산란으로 인해 광학적 수차(aberration)가 생기고, 이로 인해 영상 품질이 저하되는 한계가 있었다. 우리 연구진이 디지털 수차 보정 기술을 개발하여 두꺼운 생체 조직의 3차원 영상을 정밀하게 관찰할 수 있는 기술을 개발했다.

우리 대학 물리학과 박용근 교수 연구팀이 별도의 염색 없이 두꺼운 생체 조직의 3차원 영상을 고해상도로 관찰할 수 있는 디지털 수차 보정 기술을 개발했다고 5일 밝혔다.

연구팀은 광학적 메모리 효과(optical memory effect)*를 활용해 두꺼운 생체 조직을 실시간으로 고해상도로 관찰하는 기술을 개발했다. 이 기술은 기존 적응형 광학(adaptive optics) 기술보다 더욱 강력한 보정 효과를 제공하여, 생체 조직 내부의 구조를 보다 선명하게 포착할 수 있다.

☞광학적 메모리 효과: 빛이 기울어질 때, 산란된 빛도 함께 기울어지는 현상으로, 생체 조직과 같은 복잡한 산란 매질에서도 관찰 가능함.

새롭게 개발된 기법을 적용한 결과, 연구진은 생체 조직 내부의 세포 구조를 더욱 세밀하게 관찰할 수 있었으며, 마이크로미터 크기의 시료에서 발생하는 동적 변화를 실시간으로 포착하는 데 성공했다.

이번 연구는 조직 병리학, 신약 개발, 생물학 연구 등 다양한 분야에서 활용될 수 있는 새로운 이미징 기술을 제시했으며, 기존 기술이 극복하지 못한 심층 조직 이미징의 한계를 뛰어넘는 성과로 평가괸다. 이를 통해 생명과학 및 의료 분야에서 큰 기여를 할 것으로 기대된다.

박용근 교수는 “이번 연구는 기존 이미징 기술의 한계를 극복하는 새로운 접근 방식으로, 홀로토모그래피 기반 비침습적 생체 이미징 및 진단 연구에 큰 영향을 미칠 것이다. 앞으로는 생체 조직의 더욱 정밀한 3차원 이미징을 통해 세포 수준에서의 다양한 생명현상을 이해하는 연구를 지속할 계획”이라고 말했다.

물리학과 오철민 석박사통합과정 학생이 제1 저자인 이번 연구 결과는 지난 2월 17일 국제 학술지 ‘네이처 커뮤니케이션즈(Nature communications)’에 온라인 게재됐으며, 해당 기술은 다양한 생명과학 분야에서의 적용 가능성을 인정받고 있다.

(논문명: Digital aberration correction for enhanced thick tissue imaging exploiting aberration matrix and tilt-tilt correlation from the optical memory effect) DOI: 10.1038/s41467-025-56865-z

이번 연구는 한국연구재단 리더연구사업 및 한국산업기술진흥원 글로벌산업기술협력센터사업의 지원을 받아 수행됐다.

2025.03.05 조회수 3749 -

최대 11배 빨라진 PIM 반도체 네트워크 개발

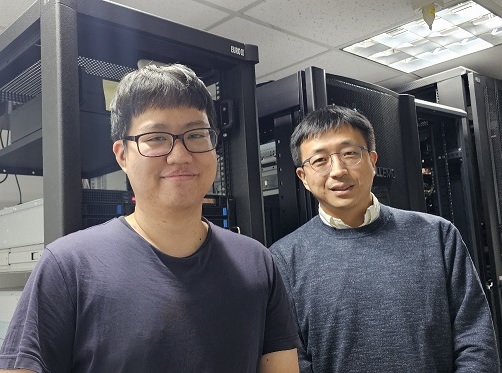

최근 인공지능, 빅데이터, 생명과학 등 연구에 사용되는 메모리 대역폭이 차지하는 비중이 높아, 메모리 내부에 연산장치를 배치하는 프로세싱-인-메모리(Processing-in-Memory, 이하 PIM) 반도체에 대한 연구개발이 활발히 진행되고 있다. 국제 공동 연구진이 기존의 PIM 반도체가 내부장치를 활용하면서도 통신을 할때 반드시 PIM 반도체 외부로 연결되는 CPU를 통해야한다는 문제점으로 발생한 병목현상을 해결했다.

우리 대학 전기및전자공학부 김동준 교수 연구팀이 미국 노스이스턴 대학(Northeastern Univ.), 보스턴 대학(Boston Univ.)와 스페인 무르시아 대학(Universidad de Murcia)의 저명 연구진과‘PIM 반도체 간 집합 통신에 특화된 인터커넥션 네트워크 아키텍처’를 통한 공동연구로 PIM 반도체의 통신 성능을 비약적으로 향상하는 기법을 개발했다고 19일 밝혔다.

김동준 교수 연구팀은 기존 PIM 반도체가 갖는 메모리 내부 연산 장치 간 통신 구조의 한계를 밝히고, 기존에 메모리 내부에 존재하는 데이터 이동을 위한 버스 구조를 최대한 활용하면서 각 연산장치를 직접적으로 상호 연결하는 *인터커넥션 네트워크 구조를 적용함으로써 PIM 반도체의 통신 성능을 극대화하는 기법을 제안했다.

※ 인터커넥션 네트워크(interconnection network): 다중 연산 장치를 포함하는 대규모 시스템 설계에 쓰이는 연산 장치 간 연결 구조를 말한다. 인터커넥션 네트워크는 다중 연산 장치를 포함하는 시스템 설계의 필수 요소 중 하나로써 시스템 규모가 커질수록 더욱 중요해지는 특징이 있다.

이를 통해 PIM 반도체를 위한 연산 과정에서 통신 처리를 위한 CPU의 개입을 최소화해 PIM 반도체 시스템의 전체적인 성능과 활용성을 높인 PIM 반도체에 특화된 인터커넥션 네트워크 구조를 개발했다.

메모리 공정은 복잡한 로직의 추가가 어렵다는 문제점이 있는데 김동준 교수팀이 개발한 네트워크 구조는 PIM에서 비용 효율적인 인터커넥트를 구현했다.

이 구조는 병렬 컴퓨팅과 기계학습 분야에서 널리 활용되는 집합 통신(Collective communication) 패턴에 특화돼 있으며, 각 연산장치의 통신량과 데이터 이동 경로를 미리 파악할 수 있다는 집합 통신의 결정성(determinism) 특징을 활용해 기존 네트워크에서 비용을 발생시키는 주요 구성 요소들을 최소화시켰다.

기존 PIM 반도체들이 통신하기 위해서는 CPU를 거쳐야만 하기 때문에 상당한 성능 손실이 있었다. 하지만, 연구팀은 PIM 특화 인터커넥션 네트워크를 적용하면 기존 시스템 대비 어플리케이션 성능을 최대 11배 향상했다고 밝혔다. 그 이유는 PIM 반도체의 내부 메모리 대역폭 활용률을 극대화하고 PIM 메모리 시스템의 규모가 커짐에 따라 통신 성능의 확장성이 함께 증가했기 때문이다.

최근 미국 전기전자공학회(IEEE) 컴퓨터 아키텍쳐 분야에서는 한국 최초로 2025 IEEE 펠로우(석학회원)로 선임되었고 이 연구를 주도한 김동준 교수는 “데이터 이동(data movement)을 줄이는 것은 PIM을 포함한 모든 시스템 반도체에서 핵심적인 요소이며, PIM은 컴퓨팅 시스템의 성능과 효율성을 향상할 수 있지만 PIM 연산장치 간 데이터 이동으로 인해 성능 확장성이 제약될 수 있어 응용 분야가 제한적이고, PIM 인터커넥트가 이에 대한 해법이 될 수 있다”고 연구의 의의를 설명했다.

전기및전자공학부 손효준 박사과정이 제1 저자로 참여한 이번 연구는 미국 네바다주 라스베이거스에서 열리는 컴퓨터 구조 분야 최우수 국제 학술대회인 ‘2025 IEEE International Symposium on High Performance Computer Architecture, HPCA 2025’에서 올 3월에 발표될 예정이다. (논문명: PIMnet: A Domain-Specific Network for Efficient Collective Communication in Scalable PIM)

한편 이번 연구는 한국연구재단, 삼성전자, 정보통신기획평가원 차세대지능형반도체기술개발사업의 지원을 받아 수행됐다.

2025.02.19 조회수 4040

최대 11배 빨라진 PIM 반도체 네트워크 개발

최근 인공지능, 빅데이터, 생명과학 등 연구에 사용되는 메모리 대역폭이 차지하는 비중이 높아, 메모리 내부에 연산장치를 배치하는 프로세싱-인-메모리(Processing-in-Memory, 이하 PIM) 반도체에 대한 연구개발이 활발히 진행되고 있다. 국제 공동 연구진이 기존의 PIM 반도체가 내부장치를 활용하면서도 통신을 할때 반드시 PIM 반도체 외부로 연결되는 CPU를 통해야한다는 문제점으로 발생한 병목현상을 해결했다.

우리 대학 전기및전자공학부 김동준 교수 연구팀이 미국 노스이스턴 대학(Northeastern Univ.), 보스턴 대학(Boston Univ.)와 스페인 무르시아 대학(Universidad de Murcia)의 저명 연구진과‘PIM 반도체 간 집합 통신에 특화된 인터커넥션 네트워크 아키텍처’를 통한 공동연구로 PIM 반도체의 통신 성능을 비약적으로 향상하는 기법을 개발했다고 19일 밝혔다.

김동준 교수 연구팀은 기존 PIM 반도체가 갖는 메모리 내부 연산 장치 간 통신 구조의 한계를 밝히고, 기존에 메모리 내부에 존재하는 데이터 이동을 위한 버스 구조를 최대한 활용하면서 각 연산장치를 직접적으로 상호 연결하는 *인터커넥션 네트워크 구조를 적용함으로써 PIM 반도체의 통신 성능을 극대화하는 기법을 제안했다.

※ 인터커넥션 네트워크(interconnection network): 다중 연산 장치를 포함하는 대규모 시스템 설계에 쓰이는 연산 장치 간 연결 구조를 말한다. 인터커넥션 네트워크는 다중 연산 장치를 포함하는 시스템 설계의 필수 요소 중 하나로써 시스템 규모가 커질수록 더욱 중요해지는 특징이 있다.

이를 통해 PIM 반도체를 위한 연산 과정에서 통신 처리를 위한 CPU의 개입을 최소화해 PIM 반도체 시스템의 전체적인 성능과 활용성을 높인 PIM 반도체에 특화된 인터커넥션 네트워크 구조를 개발했다.

메모리 공정은 복잡한 로직의 추가가 어렵다는 문제점이 있는데 김동준 교수팀이 개발한 네트워크 구조는 PIM에서 비용 효율적인 인터커넥트를 구현했다.

이 구조는 병렬 컴퓨팅과 기계학습 분야에서 널리 활용되는 집합 통신(Collective communication) 패턴에 특화돼 있으며, 각 연산장치의 통신량과 데이터 이동 경로를 미리 파악할 수 있다는 집합 통신의 결정성(determinism) 특징을 활용해 기존 네트워크에서 비용을 발생시키는 주요 구성 요소들을 최소화시켰다.

기존 PIM 반도체들이 통신하기 위해서는 CPU를 거쳐야만 하기 때문에 상당한 성능 손실이 있었다. 하지만, 연구팀은 PIM 특화 인터커넥션 네트워크를 적용하면 기존 시스템 대비 어플리케이션 성능을 최대 11배 향상했다고 밝혔다. 그 이유는 PIM 반도체의 내부 메모리 대역폭 활용률을 극대화하고 PIM 메모리 시스템의 규모가 커짐에 따라 통신 성능의 확장성이 함께 증가했기 때문이다.

최근 미국 전기전자공학회(IEEE) 컴퓨터 아키텍쳐 분야에서는 한국 최초로 2025 IEEE 펠로우(석학회원)로 선임되었고 이 연구를 주도한 김동준 교수는 “데이터 이동(data movement)을 줄이는 것은 PIM을 포함한 모든 시스템 반도체에서 핵심적인 요소이며, PIM은 컴퓨팅 시스템의 성능과 효율성을 향상할 수 있지만 PIM 연산장치 간 데이터 이동으로 인해 성능 확장성이 제약될 수 있어 응용 분야가 제한적이고, PIM 인터커넥트가 이에 대한 해법이 될 수 있다”고 연구의 의의를 설명했다.

전기및전자공학부 손효준 박사과정이 제1 저자로 참여한 이번 연구는 미국 네바다주 라스베이거스에서 열리는 컴퓨터 구조 분야 최우수 국제 학술대회인 ‘2025 IEEE International Symposium on High Performance Computer Architecture, HPCA 2025’에서 올 3월에 발표될 예정이다. (논문명: PIMnet: A Domain-Specific Network for Efficient Collective Communication in Scalable PIM)

한편 이번 연구는 한국연구재단, 삼성전자, 정보통신기획평가원 차세대지능형반도체기술개발사업의 지원을 받아 수행됐다.

2025.02.19 조회수 4040 -

강유전체 활용 차세대 반도체 메모리 혁신

강유전체는 메모리 소자에서 전하를 잘 저장하기 때문에 "전기를 기억하는 소재"와 같다는 특성으로 차세대 반도체 기술 개발에 있어 핵심 소재로 부각되고 있다. 우리 연구진이 이러한 강유전체 소재를 활용해 현재 메모리 반도체 산업의 양대 산맥인 디램(DRAM)과 낸드 플래시(NAND Flash) 메모리의 한계를 극복한 고성능, 고집적 차세대 메모리 소자를 개발하는데 성공했다.

우리 대학 전상훈 교수 연구팀이 하프니아 강유전체 소재*를 활용한 차세대 메모리 및 스토리지 메모리 기술을 개발했다고 6일 밝혔다.

*하프니아 강유전체 소재: 비휘발성 절연막으로, CMOS 공정 호환성, 동작 속도, 내구성 등의 우수한 물리적 특성을 바탕으로 차세대 반도체의 핵심 소재로 활발하게 연구되고 있는 물질

디램 메모리는 우리가 스마트폰, 컴퓨터, USB 등에서 사용하는 데이터를 저장하는 휘발성 메모리다. 휘발성 특성으로 인해, 외부 전력이 끊어지면 저장된 데이터가 손실되지만, 공정 단가가 낮고 집적도가 높아 메인 메모리로 활용돼 왔다. 하지만 디램 메모리 기술은 소자의 크기가 작아질수록 디램 소자가 정보를 저장하는 저장 커패시터의 용량도 작아지게 되고, 더 이상 메모리 동작을 수행하기 어렵다.

연구팀은 저장 커패시터는 정보를 저장하는 디램 기술의 한계를 극복하고자 이러한 저장 커패시터가 물리적으로 작은 면적에서도 높은 저장 용량을 달성할 수 있도록 개선하는 데에 집중했다. 이를 위해 하프니아 강유전체 기반 극박막의 고유전율 물질을 개발했다. 연구 결과 현재까지 보고된 디램 커패시터 중, 가장 낮은 2.4 Å (머리카락 굵기의 약 10만분의 1)의 SiO2(실리콘 산화물) 유효 두께와 같이 얇은 층에 저장하는 것을 달성했다.

또한 연구팀은 디램 메모리 기술을 잠재적으로 대체할 수 있는 후보군으로 주목받고 있는 강유전체 메모리 FRAM 메모리도 개발하였다. 현 DRAM 수준의 1V 이하의 낮은 전압에서도 비 휘발성 정보 저장과 삭제가 확실히 이루어지는 기술은 에너지 효율성을 크게 향상시켜 차세대 메모리에 필수적이다.

디램 메모리 기술에 이어 연구팀은 낸드 플래시 메모리의 한계를 극복할 하프니아 강유전체 기반의 차세대 메모리 기술을 개발했다. 낸드 플래시 메모리는 우리가 스마트폰, 컴퓨터, USB 등에서 사용하는 데이터를 저장하는 비휘발성 메모리이다. 현재, 낸드플래시 메모리의 저장 용량을 늘리기 위해 여러 층을 쌓아 올리는 방식으로 발전해 왔지만, 물리적인 한계로 인해 500층, 1000층 이상으로 쌓기가 어려운 상황이다.

이에 연구팀은 강유전체라는 새로운 소재를 낸드 플래시에 적용하는 방식을 연구한 결과, 소재 계면에 TiO2 층이라는 얇은 층을 추가함으로써 1000단 이상의 수직 적층 3차원이며 외부 환경의 간섭에도 데이터를 안정적으로 유지하도록 설계했다.

마지막으로 기존의 낸드 플래시 기술에서 산화물 채널 기반의 메모리 소자는 데이터를 완전히 지울 수 없는 한계가 있어 새로운 구조의 고성능 산화물 채널 기반 낸드 플래시 소자를 개발하는 데 성공했다. 이 소자는 더 많은 데이터를 저장할 수 있고 데이터를 10년 이상 안정적으로 보존할 수 있는 특징을 가진다.

전상훈 교수는 “이번 연구 결과들은 스케일링 이슈로 인해 답보상태에 있는 메모리 반도체 기술 개발에 돌파구가 되는 기술이 될 것으로 판단되며, 향후 다양한 인공지능 컴퓨팅 및 엣지 컴퓨팅 기술 상용화에 기여할 수 있을 것”이라고 설명했다.

벤카테스왈루 가담(Venkateswarlu Gaddam) 연구 교수, 김기욱 박사 과정, 조홍래 박사 과정, 황정현 박사 과정, 이상호 박사 과정, 최효준 석사 과정, 강현준 석사 과정이 공동 제1 저자로 참여했고 이러한 연구 성과를 국제적으로 인정받아 반도체 산업계 최고 수준의(Top-tier) 컨퍼런스에 2024년 5편의 논문을 발표했다. (2024 VLSI 2편, 2024 IEDM 3편)

- In-depth analysis of the Hafnia ferroelectrics as a key enabler for low voltage & QLC 3D VNAND beyond 1K layers: Experimental demonstration and modeling VLSI 24 DOI: 10.1109/VLSITechnologyandCir46783.2024

- Low-Damage Processed and High-Pressure Annealed High-k Hafnium Zirconium Oxide Capacitors near Morphotropic Phase Boundary with Record-Low EOT of 2.4 Å & high-k of 70 for DRAM … VLSI 24 DOI: 10.1109/VLSITechnologyandCir46783.2024

- Unveiling the Origin of Disturbance in FeFET and the Potential of Multifunctional TiO2 as a Breakthrough for Disturb-free 3D NAND Cell: Experimental and Modeling https://iedm24.mapyourshow.com/8_0/sessions/session-details.cfm?scheduleid=4

- Oxide Channel Ferroelectric NAND Device with Source- tied Covering Metal Structure: Wide Memory Window (14.3 V), Reliable Retention (> 10 years) and Disturbance Immunity (△Vth ≤ 0.1 V) for QLC Operation

https://iedm24.mapyourshow.com/8_0/sessions/session-details.cfm?scheduleid=47

- Design Methodology for Low-Voltage Operational (≤1 V) FRAM Cell Capacitors and Approaches for Overcoming Disturb Issues in 1T-nC Arrays: Experimental & Modeling:

https://iedm24.mapyourshow.com/8_0/sessions/session-details.cfm?scheduleid=54

참고로, IEEE VLSI와 IEEE IEDM 학회는 삼성전자, SK 하이닉스, 마이크론, 인텔 등 굴지의 반도체 업계와 세계적인 석학들이 최신 기술 개발을 공유하고 미래 기술의 지향점을 논의하는 학회로 반도체 올림픽이라고 불린다.

한편, 이 연구는 삼성전자, 한양대학교와 협업을 통해서 수행되었으며, 한국산업기술평가원 (KEIT) 민관공동투자 반도체 고급인력양성사업, 과학기술정보통신부 혁신연구센터(IRC) 지원 사업, 삼성전자(Samsung Electronics)의 지원을 받아 진행됐다.

2025.01.06 조회수 6020

강유전체 활용 차세대 반도체 메모리 혁신

강유전체는 메모리 소자에서 전하를 잘 저장하기 때문에 "전기를 기억하는 소재"와 같다는 특성으로 차세대 반도체 기술 개발에 있어 핵심 소재로 부각되고 있다. 우리 연구진이 이러한 강유전체 소재를 활용해 현재 메모리 반도체 산업의 양대 산맥인 디램(DRAM)과 낸드 플래시(NAND Flash) 메모리의 한계를 극복한 고성능, 고집적 차세대 메모리 소자를 개발하는데 성공했다.

우리 대학 전상훈 교수 연구팀이 하프니아 강유전체 소재*를 활용한 차세대 메모리 및 스토리지 메모리 기술을 개발했다고 6일 밝혔다.

*하프니아 강유전체 소재: 비휘발성 절연막으로, CMOS 공정 호환성, 동작 속도, 내구성 등의 우수한 물리적 특성을 바탕으로 차세대 반도체의 핵심 소재로 활발하게 연구되고 있는 물질

디램 메모리는 우리가 스마트폰, 컴퓨터, USB 등에서 사용하는 데이터를 저장하는 휘발성 메모리다. 휘발성 특성으로 인해, 외부 전력이 끊어지면 저장된 데이터가 손실되지만, 공정 단가가 낮고 집적도가 높아 메인 메모리로 활용돼 왔다. 하지만 디램 메모리 기술은 소자의 크기가 작아질수록 디램 소자가 정보를 저장하는 저장 커패시터의 용량도 작아지게 되고, 더 이상 메모리 동작을 수행하기 어렵다.

연구팀은 저장 커패시터는 정보를 저장하는 디램 기술의 한계를 극복하고자 이러한 저장 커패시터가 물리적으로 작은 면적에서도 높은 저장 용량을 달성할 수 있도록 개선하는 데에 집중했다. 이를 위해 하프니아 강유전체 기반 극박막의 고유전율 물질을 개발했다. 연구 결과 현재까지 보고된 디램 커패시터 중, 가장 낮은 2.4 Å (머리카락 굵기의 약 10만분의 1)의 SiO2(실리콘 산화물) 유효 두께와 같이 얇은 층에 저장하는 것을 달성했다.

또한 연구팀은 디램 메모리 기술을 잠재적으로 대체할 수 있는 후보군으로 주목받고 있는 강유전체 메모리 FRAM 메모리도 개발하였다. 현 DRAM 수준의 1V 이하의 낮은 전압에서도 비 휘발성 정보 저장과 삭제가 확실히 이루어지는 기술은 에너지 효율성을 크게 향상시켜 차세대 메모리에 필수적이다.

디램 메모리 기술에 이어 연구팀은 낸드 플래시 메모리의 한계를 극복할 하프니아 강유전체 기반의 차세대 메모리 기술을 개발했다. 낸드 플래시 메모리는 우리가 스마트폰, 컴퓨터, USB 등에서 사용하는 데이터를 저장하는 비휘발성 메모리이다. 현재, 낸드플래시 메모리의 저장 용량을 늘리기 위해 여러 층을 쌓아 올리는 방식으로 발전해 왔지만, 물리적인 한계로 인해 500층, 1000층 이상으로 쌓기가 어려운 상황이다.

이에 연구팀은 강유전체라는 새로운 소재를 낸드 플래시에 적용하는 방식을 연구한 결과, 소재 계면에 TiO2 층이라는 얇은 층을 추가함으로써 1000단 이상의 수직 적층 3차원이며 외부 환경의 간섭에도 데이터를 안정적으로 유지하도록 설계했다.

마지막으로 기존의 낸드 플래시 기술에서 산화물 채널 기반의 메모리 소자는 데이터를 완전히 지울 수 없는 한계가 있어 새로운 구조의 고성능 산화물 채널 기반 낸드 플래시 소자를 개발하는 데 성공했다. 이 소자는 더 많은 데이터를 저장할 수 있고 데이터를 10년 이상 안정적으로 보존할 수 있는 특징을 가진다.

전상훈 교수는 “이번 연구 결과들은 스케일링 이슈로 인해 답보상태에 있는 메모리 반도체 기술 개발에 돌파구가 되는 기술이 될 것으로 판단되며, 향후 다양한 인공지능 컴퓨팅 및 엣지 컴퓨팅 기술 상용화에 기여할 수 있을 것”이라고 설명했다.

벤카테스왈루 가담(Venkateswarlu Gaddam) 연구 교수, 김기욱 박사 과정, 조홍래 박사 과정, 황정현 박사 과정, 이상호 박사 과정, 최효준 석사 과정, 강현준 석사 과정이 공동 제1 저자로 참여했고 이러한 연구 성과를 국제적으로 인정받아 반도체 산업계 최고 수준의(Top-tier) 컨퍼런스에 2024년 5편의 논문을 발표했다. (2024 VLSI 2편, 2024 IEDM 3편)

- In-depth analysis of the Hafnia ferroelectrics as a key enabler for low voltage & QLC 3D VNAND beyond 1K layers: Experimental demonstration and modeling VLSI 24 DOI: 10.1109/VLSITechnologyandCir46783.2024

- Low-Damage Processed and High-Pressure Annealed High-k Hafnium Zirconium Oxide Capacitors near Morphotropic Phase Boundary with Record-Low EOT of 2.4 Å & high-k of 70 for DRAM … VLSI 24 DOI: 10.1109/VLSITechnologyandCir46783.2024

- Unveiling the Origin of Disturbance in FeFET and the Potential of Multifunctional TiO2 as a Breakthrough for Disturb-free 3D NAND Cell: Experimental and Modeling https://iedm24.mapyourshow.com/8_0/sessions/session-details.cfm?scheduleid=4

- Oxide Channel Ferroelectric NAND Device with Source- tied Covering Metal Structure: Wide Memory Window (14.3 V), Reliable Retention (> 10 years) and Disturbance Immunity (△Vth ≤ 0.1 V) for QLC Operation

https://iedm24.mapyourshow.com/8_0/sessions/session-details.cfm?scheduleid=47

- Design Methodology for Low-Voltage Operational (≤1 V) FRAM Cell Capacitors and Approaches for Overcoming Disturb Issues in 1T-nC Arrays: Experimental & Modeling:

https://iedm24.mapyourshow.com/8_0/sessions/session-details.cfm?scheduleid=54

참고로, IEEE VLSI와 IEEE IEDM 학회는 삼성전자, SK 하이닉스, 마이크론, 인텔 등 굴지의 반도체 업계와 세계적인 석학들이 최신 기술 개발을 공유하고 미래 기술의 지향점을 논의하는 학회로 반도체 올림픽이라고 불린다.

한편, 이 연구는 삼성전자, 한양대학교와 협업을 통해서 수행되었으며, 한국산업기술평가원 (KEIT) 민관공동투자 반도체 고급인력양성사업, 과학기술정보통신부 혁신연구센터(IRC) 지원 사업, 삼성전자(Samsung Electronics)의 지원을 받아 진행됐다.

2025.01.06 조회수 6020 -

차세대 뉴로모픽 컴퓨팅 신뢰성 문제를 풀다

최근 인간의 뇌를 모방해 하드웨어 기반으로 인공지능 연산을 구현하는 뉴로모픽 컴퓨팅 기술이 최근 주목받고 있다. 뉴로모픽 컴퓨팅의 단위 소자로 활용되는 멤리스터(전도성 변화 소자)는 저전력, 고집적, 고효율 등의 장점이 있지만 멤리스터로 대용량 뉴로모픽 컴퓨팅 시스템을 구현하는데 불규칙한 소자 특성으로 인한 신뢰성 문제가 발견되었다. 우리 연구진이 뉴로모픽 컴퓨팅의 상용화를 앞당길 신뢰성 향상 기술을 개발하여 화제다.

우리 대학 전기및전자공학부 최신현 교수 연구팀이 한양대학교 연구진과의 공동 연구를 통해 차세대 메모리 소자의 신뢰성과 성능을 높일 수 있는 이종원자가 이온* 도핑 방법을 개발했다고 21일 밝혔다.

* 이종원자가 이온(Aliovalent ion): 원래 존재하던 원자와 다른 원자가(공유 결합의 척도, valance)를 갖는 이온을 말함

공동연구팀은 기존 차세대 메모리 소자의 가장 큰 문제인 불규칙한 소자 특성 변화 문제를 개선하기 위해, 이종원자가 이온을 도핑하는 방식으로 소자의 균일성과 성능을 향상할 수 있다는 사실을 실험과 원자 수준의 시뮬레이션을 통해 원리를 규명했다.

공동 연구팀은 이러한 불규칙한 소자 신뢰성 문제를 해결하기 위해 이종원자가 할라이드(halide) 이온을 산화물 층 내에 적절히 주입하는 방법이 소자의 신뢰성과 성능을 향상할 수 있음을 보고했다. 연구팀은 이러한 방법으로 소자 동작의 균일성, 동작 속도, 그리고 성능이 증대됨을 실험적으로 확인했다.

연구팀은 또한, 원자 단위 시뮬레이션 분석을 통해 결정질과 비결정질 환경에서 모두 실험적으로 확인한 결과와 일치하는 소자 성능 개선 효과가 나타남을 보고했다. 그 과정에서 도핑된 이종원자가 이온이 근처 산소 빈자리(oxygen vacancy)를 끌어당겨 안정적인 소자 동작을 가능하게 하고, 이온 근처 공간을 넓혀 빠른 소자 동작을 가능하게 하는 원리를 밝혀냈다.

최신현 교수는 "이번에 개발한 이종원자가 이온 도핑 방법은 뉴로모픽 소자의 신뢰성과 성능을 획기적으로 높이는 방법으로서, 차세대 멤리스터 기반 뉴로모픽 컴퓨팅의 상용화에 기여할 수 있고, 밝혀낸 성능 향상 원리를 다양한 반도체 소자들에 응용할 수 있을 것이다ˮ 고 밝혔다.

전기및전자공학부 배종민 석사과정, 한양대학교 권초아 박사후연구원이 공동 제1 저자로 참여한 이번 연구는 국제 학술지 `사이언스 어드밴시스(Science Advances)' 6월호에 출판됐다. (논문명 : Tunable ion energy barrier modulation through aliovalent halide doping for reliable and dynamic memristive neuromorphic systems)

한편 이번 연구는 한국연구재단 신소자원천기술개발사업, 신재료PIM소자사업, 우수신진연구사업, 나노종합기술원 반도체공정기반 나노메디컬 디바이스개발 사업, 그리고 국가슈퍼컴퓨팅센터 혁신지원프로그램의 지원을 받아 수행됐다.

2024.06.21 조회수 8418

차세대 뉴로모픽 컴퓨팅 신뢰성 문제를 풀다

최근 인간의 뇌를 모방해 하드웨어 기반으로 인공지능 연산을 구현하는 뉴로모픽 컴퓨팅 기술이 최근 주목받고 있다. 뉴로모픽 컴퓨팅의 단위 소자로 활용되는 멤리스터(전도성 변화 소자)는 저전력, 고집적, 고효율 등의 장점이 있지만 멤리스터로 대용량 뉴로모픽 컴퓨팅 시스템을 구현하는데 불규칙한 소자 특성으로 인한 신뢰성 문제가 발견되었다. 우리 연구진이 뉴로모픽 컴퓨팅의 상용화를 앞당길 신뢰성 향상 기술을 개발하여 화제다.

우리 대학 전기및전자공학부 최신현 교수 연구팀이 한양대학교 연구진과의 공동 연구를 통해 차세대 메모리 소자의 신뢰성과 성능을 높일 수 있는 이종원자가 이온* 도핑 방법을 개발했다고 21일 밝혔다.

* 이종원자가 이온(Aliovalent ion): 원래 존재하던 원자와 다른 원자가(공유 결합의 척도, valance)를 갖는 이온을 말함

공동연구팀은 기존 차세대 메모리 소자의 가장 큰 문제인 불규칙한 소자 특성 변화 문제를 개선하기 위해, 이종원자가 이온을 도핑하는 방식으로 소자의 균일성과 성능을 향상할 수 있다는 사실을 실험과 원자 수준의 시뮬레이션을 통해 원리를 규명했다.

공동 연구팀은 이러한 불규칙한 소자 신뢰성 문제를 해결하기 위해 이종원자가 할라이드(halide) 이온을 산화물 층 내에 적절히 주입하는 방법이 소자의 신뢰성과 성능을 향상할 수 있음을 보고했다. 연구팀은 이러한 방법으로 소자 동작의 균일성, 동작 속도, 그리고 성능이 증대됨을 실험적으로 확인했다.

연구팀은 또한, 원자 단위 시뮬레이션 분석을 통해 결정질과 비결정질 환경에서 모두 실험적으로 확인한 결과와 일치하는 소자 성능 개선 효과가 나타남을 보고했다. 그 과정에서 도핑된 이종원자가 이온이 근처 산소 빈자리(oxygen vacancy)를 끌어당겨 안정적인 소자 동작을 가능하게 하고, 이온 근처 공간을 넓혀 빠른 소자 동작을 가능하게 하는 원리를 밝혀냈다.

최신현 교수는 "이번에 개발한 이종원자가 이온 도핑 방법은 뉴로모픽 소자의 신뢰성과 성능을 획기적으로 높이는 방법으로서, 차세대 멤리스터 기반 뉴로모픽 컴퓨팅의 상용화에 기여할 수 있고, 밝혀낸 성능 향상 원리를 다양한 반도체 소자들에 응용할 수 있을 것이다ˮ 고 밝혔다.

전기및전자공학부 배종민 석사과정, 한양대학교 권초아 박사후연구원이 공동 제1 저자로 참여한 이번 연구는 국제 학술지 `사이언스 어드밴시스(Science Advances)' 6월호에 출판됐다. (논문명 : Tunable ion energy barrier modulation through aliovalent halide doping for reliable and dynamic memristive neuromorphic systems)

한편 이번 연구는 한국연구재단 신소자원천기술개발사업, 신재료PIM소자사업, 우수신진연구사업, 나노종합기술원 반도체공정기반 나노메디컬 디바이스개발 사업, 그리고 국가슈퍼컴퓨팅센터 혁신지원프로그램의 지원을 받아 수행됐다.

2024.06.21 조회수 8418 -

뉴로모픽 반도체 신개념 메모리 소자 개발

우리 연구진이 공정 비용이 낮고 초저전력 동작이 가능하여 기존의 메모리를 대체하거나 차세대 인공지능 하드웨어를 위한 뉴로모픽 컴퓨팅(Neuromorphic Computing) 구현에 사용될 메모리 소자를 개발하여 화제다.

전기및전자공학부 최신현 교수 연구팀이 디램 (DRAM) 및 낸드(NAND) 플래시 메모리를 대체할 수 있는 *초저전력 차세대 상변화 메모리 소자를 개발했다고 4일 밝혔다.

☞ 상변화 메모리(Phase Change Memory): 열을 사용하여 물질의 상태를 비정질과 결정질을 변경하여, 이를 통해 저항 상태를 변경함으로써 정보를 저장하거나 처리하는 메모리 소자.

기존 상변화 메모리는 값비싼 초미세 반도체 노광공정을 통해 제작하며 소모 전력이 높은 문제점이 있었다. 최 교수 연구팀은 상변화 물질을 전기적으로 극소 형성하는 방식을 통해 제작한 초저전력 상변화 메모리 소자로 값비싼 노광공정 없이도 매우 작은 나노미터(nm) 스케일의 상변화 필라멘트를 자체적으로 형성하였다. 이는 공정 비용이 매우 낮을 뿐 아니라 초저전력 동작이 가능하다는 획기적인 장점이 있다.

현재 널리 사용되고 있는 메모리인 디램(DRAM)은 속도가 매우 빠르지만, 전원이 꺼지면 정보가 사라지는 휘발성 특징을 갖고 있으며, 저장장치로 사용되는 낸드 플래시 메모리는 읽기/쓰기 속도는 상대적으로 느린 대신 전원이 꺼져도 정보를 보존하는 비휘발성 특징을 갖고 있다.

이에 반해, 상변화 메모리는 디램과 낸드 플래시 메모리의 장점을 모두 가진 차세대 메모리로, 빠른 속도와 비휘발성 특성을 동시에 지닌다. 이러한 이유로, 상변화 메모리는 기존의 메모리를 대체할 수 있는 차세대 메모리로 각광받으며, 메모리 기술 또는 인간의 두뇌를 모방하는 뉴로모픽 컴퓨팅 기술로 활발히 연구되고 있다.

그러나 기존 상변화 메모리는 소비 전력이 매우 높아서 실용적인 대용량 메모리 제품 및 뉴로모픽 컴퓨팅 시스템을 구현하기에는 어려움이 있다. 기존 연구는 메모리 동작을 위한 발열 효과를 높이기 위해 초미세 반도체 노광공정을 이용해 소자의 물리적 크기를 줄여 소비 전력을 낮추는 연구가 진행됐으나, 소비 전력 개선 정도가 작고 공정비용과 공정 난이도가 증가해 실용성 측면의 한계점이 존재했다.

최신현 교수 연구팀은 이러한 상변화 메모리의 소비 전력 문제를 해결하기 위해, 상변화 물질을 전기적으로 극소 형성하는 방식으로 기존의 값비싼 초미세 노광공정을 이용한 상변화 메모리 소자보다 소비 전력이 15배 이상 작은 초저전력 상변화 메모리 소자 구현에 성공했다.

최신현 교수는 "이번에 개발한 초저전력 상변화 메모리 소자는 기존의 연구 방향과는 완전히 다른 방식으로 기존에 풀지 못하였던 큰 숙제인 제조비용과 에너지 효율을 대폭 개선한 소자를 개발했다는 의의가 있다. 또한 물질 선택이 자유로워 고집적 3차원 수직 메모리 및 뉴로모픽 컴퓨팅 시스템 등 다양한 응용을 가능케 하는 등 미래 전자공학의 기반이 될 것으로 기대한다ˮ며 이번 연구가 앞으로 뻗어나갈 새로운 분야에 대한 강한 자신감을 피력했다. 또한 "이 연구를 지원한 한국연구재단 및 나노종합기술원에 감사드린다ˮ라고 말했다.

전기및전자공학부 박시온 석박사통합과정, 홍석만 박사과정이 제1 저자로 참여한 이번 연구는 저명한 국제 학술지 `네이처(Nature)' 4월호에 4월 4일 자 출판됐다. (논문명 : Phase-Change Memory via a Phase-Changeable Self-Confined Nano-Filament)

한편 이번 연구는 한국연구재단 차세대 지능형반도체기술개발사업, PIM인공지능반도체핵심기술개발(소자)사업, 우수신진연구, 그리고 나노종합기술원 반도체공정기반 나노메디컬 디바이스개발 사업의 지원을 받아 수행됐다.

2024.04.04 조회수 9792

뉴로모픽 반도체 신개념 메모리 소자 개발

우리 연구진이 공정 비용이 낮고 초저전력 동작이 가능하여 기존의 메모리를 대체하거나 차세대 인공지능 하드웨어를 위한 뉴로모픽 컴퓨팅(Neuromorphic Computing) 구현에 사용될 메모리 소자를 개발하여 화제다.

전기및전자공학부 최신현 교수 연구팀이 디램 (DRAM) 및 낸드(NAND) 플래시 메모리를 대체할 수 있는 *초저전력 차세대 상변화 메모리 소자를 개발했다고 4일 밝혔다.

☞ 상변화 메모리(Phase Change Memory): 열을 사용하여 물질의 상태를 비정질과 결정질을 변경하여, 이를 통해 저항 상태를 변경함으로써 정보를 저장하거나 처리하는 메모리 소자.

기존 상변화 메모리는 값비싼 초미세 반도체 노광공정을 통해 제작하며 소모 전력이 높은 문제점이 있었다. 최 교수 연구팀은 상변화 물질을 전기적으로 극소 형성하는 방식을 통해 제작한 초저전력 상변화 메모리 소자로 값비싼 노광공정 없이도 매우 작은 나노미터(nm) 스케일의 상변화 필라멘트를 자체적으로 형성하였다. 이는 공정 비용이 매우 낮을 뿐 아니라 초저전력 동작이 가능하다는 획기적인 장점이 있다.

현재 널리 사용되고 있는 메모리인 디램(DRAM)은 속도가 매우 빠르지만, 전원이 꺼지면 정보가 사라지는 휘발성 특징을 갖고 있으며, 저장장치로 사용되는 낸드 플래시 메모리는 읽기/쓰기 속도는 상대적으로 느린 대신 전원이 꺼져도 정보를 보존하는 비휘발성 특징을 갖고 있다.

이에 반해, 상변화 메모리는 디램과 낸드 플래시 메모리의 장점을 모두 가진 차세대 메모리로, 빠른 속도와 비휘발성 특성을 동시에 지닌다. 이러한 이유로, 상변화 메모리는 기존의 메모리를 대체할 수 있는 차세대 메모리로 각광받으며, 메모리 기술 또는 인간의 두뇌를 모방하는 뉴로모픽 컴퓨팅 기술로 활발히 연구되고 있다.

그러나 기존 상변화 메모리는 소비 전력이 매우 높아서 실용적인 대용량 메모리 제품 및 뉴로모픽 컴퓨팅 시스템을 구현하기에는 어려움이 있다. 기존 연구는 메모리 동작을 위한 발열 효과를 높이기 위해 초미세 반도체 노광공정을 이용해 소자의 물리적 크기를 줄여 소비 전력을 낮추는 연구가 진행됐으나, 소비 전력 개선 정도가 작고 공정비용과 공정 난이도가 증가해 실용성 측면의 한계점이 존재했다.

최신현 교수 연구팀은 이러한 상변화 메모리의 소비 전력 문제를 해결하기 위해, 상변화 물질을 전기적으로 극소 형성하는 방식으로 기존의 값비싼 초미세 노광공정을 이용한 상변화 메모리 소자보다 소비 전력이 15배 이상 작은 초저전력 상변화 메모리 소자 구현에 성공했다.

최신현 교수는 "이번에 개발한 초저전력 상변화 메모리 소자는 기존의 연구 방향과는 완전히 다른 방식으로 기존에 풀지 못하였던 큰 숙제인 제조비용과 에너지 효율을 대폭 개선한 소자를 개발했다는 의의가 있다. 또한 물질 선택이 자유로워 고집적 3차원 수직 메모리 및 뉴로모픽 컴퓨팅 시스템 등 다양한 응용을 가능케 하는 등 미래 전자공학의 기반이 될 것으로 기대한다ˮ며 이번 연구가 앞으로 뻗어나갈 새로운 분야에 대한 강한 자신감을 피력했다. 또한 "이 연구를 지원한 한국연구재단 및 나노종합기술원에 감사드린다ˮ라고 말했다.

전기및전자공학부 박시온 석박사통합과정, 홍석만 박사과정이 제1 저자로 참여한 이번 연구는 저명한 국제 학술지 `네이처(Nature)' 4월호에 4월 4일 자 출판됐다. (논문명 : Phase-Change Memory via a Phase-Changeable Self-Confined Nano-Filament)

한편 이번 연구는 한국연구재단 차세대 지능형반도체기술개발사업, PIM인공지능반도체핵심기술개발(소자)사업, 우수신진연구, 그리고 나노종합기술원 반도체공정기반 나노메디컬 디바이스개발 사업의 지원을 받아 수행됐다.

2024.04.04 조회수 9792 -

111배 빠른 검색엔진용 CXL 3.0 기반 AI반도체 세계 최초 개발

최근 각광받고 있는 이미지 검색, 데이터베이스, 추천 시스템, 광고 등의 서비스들은 마이크로소프트, 메타, 알리바바 등의 글로벌 IT 기업들에서 활발히 제공되고 있다. 하지만 실제 서비스에서 사용되는 데이터 셋은 크기가 매우 커, 많은 양의 메모리를 요구하여 기존 시스템에서는 추가할 수 있는 메모리 용량에 제한이 있어 이러한 요구사항을 만족할 수 없었다.

우리 대학 전기및전자공학부 정명수 교수 연구팀(컴퓨터 아키텍처 및 메모리 시스템 연구실)에서 대용량으로 메모리 확장이 가능한 컴퓨트 익스프레스 링크 3.0 기술(Compute eXpress Link, 이하 CXL)을 활용해 검색 엔진을 위한 AI 반도체를 세계 최초로 개발했다고 25일 밝혔다.

최근 검색 서비스에서 사용되는 알고리즘은 근사 근접 이웃 탐색(Approximate Nearest Neighbor Search, ANNS)으로 어떤 데이터든지 특징 벡터로 표현할 수 있다. 특징 벡터란 데이터가 가지는 특징들 각각을 숫자로 표현해 나열한 것으로, 이들 사이의 거리를 통해 우리는 데이터 간의 유사도를 구할 수 있다. 하지만 벡터 데이터 용량이 매우 커서 이를 압축해 메모리에 적재하는 압축 방식과 메모리보다 큰 용량과 느린 속도를 가지는 저장 장치를 사용하는 스토리지 방식(마이크로소프트에서 사용 중)이 사용되어 왔다. 하지만 이들 각각은 낮은 정확도와 성능을 가지는 문제가 있었다.

이에 정명수 교수 연구팀은 메모리 확장의 제한이라는 근본적인 문제를 해결하기 위해 CXL이라는 기술에 주목했다. CXL은 CPU-장치 간 연결을 위한 프로토콜로, 가속기 및 메모리 확장기의 고속 연결을 제공한다. 또한 CXL 스위치를 통해 여러 대의 메모리 확장기를 하나의 포트에 연결할 수 있는 확장성을 제공한다. 하지만 CXL을 통한 메모리 확장은 로컬 메모리와 비교해 메모리 접근 시간이 증가하는 단점을 가지고 있다.

데이터를 책으로 비유하자면 기존 시스템은 집에 해당하는 CPU 크기의 제한으로 서재(메모리 용량)를 무한정 늘릴 수 없어, 보관할 수 있는 책 개수에 제한이 있는 것이다. 이에 압축 방식은 책의 내용을 압축하여 더 많은 책을 보관하는 방법이고, 스토리지 방식은 필요한 책들을 거리가 먼 도서관에서 구해오는 것과 비슷하다. CXL을 통한 메모리 확장은 집 옆에 창고를 지어 책을 보관하는 것으로 이해될 수 있다.

연구진이 개발한 AI 반도체(CXL-ANNS)는 CXL 스위치와 CXL 메모리 확장기를 사용해 근사 근접 이웃 탐색에서 필요한 모든 데이터를 메모리에 적재할 수 있어 정확도를 높이고 성능 감소를 없앴다. 또한 근사 근접 이웃 탐색의 특징을 활용해 데이터 근처 처리 기법과 지역성을 활용한 데이터 배치 기법으로 CXL-ANNS의 성능을 한 단계 향상했다. 이는 마치 창고 스스로가 필요한 책들의 내용을 요약하고 정리해 전달하고, 자주 보는 책들은 서재에 배치해 집과 창고를 오가는 시간을 줄이는 것과 유사하다.

연구진은 CXL-ANNS의 프로토타입을 자체 제작해 실효성을 확인하고, CXL-ANNS 성능을 기존 연구들과 비교했다. 마이크로소프트, 메타, 얀덱스 등의 글로벌 IT 기업에서 공개한 검색 데이터 셋을 사용한 근사 근접 이웃 탐색의 성능 비교에서 CXL-ANNS는 기존 연구들 대비 평균 111배 성능 향상이 있었다. 특히, 마이크로소프트의 상용화된 서비스에서 사용되는 방식과 비교하였을 때 92배의 성능 향상을 보여줬다.

정명수 교수는 "이번에 개발한 CXL-ANNS는 기존 검색 엔진의 문제였던 메모리 용량 제한 문제를 해결하고, CXL 기반의 메모리 확장이 실제 적용될 때 발생하는 메모리 접근 시간 지연 문제를 해결했다ˮ며, “제안하는 CXL 기반 메모리 확장과 데이터 근처 처리 가속의 패러다임은 검색 엔진뿐만 아니라 빅 데이터가 필요한 고성능 컴퓨팅, 유전자 탐색, 영상 처리 등의 다양한 분야에도 적용할 수 있다ˮ라고 말했다.

이번 연구는 미국 보스턴에서 오는 7월에 열릴 시스템 분야 최우수 학술대회인 유즈닉스 연례 회의 `USENIX Annual Technical Conference, 2023'에 ‘CXL-ANNS’이라는 이름으로 발표된 예정이다. (논문명: CXL-ANNS: Software-Hardware Collaborative Memory Disaggregation and Computation for Billion-Scale Approximate Nearest Neighbor Search)

한편 해당 연구는 파네시아(http://panmnesia.com)의 지원을 받아 진행됐다.

2023.05.25 조회수 9131

111배 빠른 검색엔진용 CXL 3.0 기반 AI반도체 세계 최초 개발

최근 각광받고 있는 이미지 검색, 데이터베이스, 추천 시스템, 광고 등의 서비스들은 마이크로소프트, 메타, 알리바바 등의 글로벌 IT 기업들에서 활발히 제공되고 있다. 하지만 실제 서비스에서 사용되는 데이터 셋은 크기가 매우 커, 많은 양의 메모리를 요구하여 기존 시스템에서는 추가할 수 있는 메모리 용량에 제한이 있어 이러한 요구사항을 만족할 수 없었다.

우리 대학 전기및전자공학부 정명수 교수 연구팀(컴퓨터 아키텍처 및 메모리 시스템 연구실)에서 대용량으로 메모리 확장이 가능한 컴퓨트 익스프레스 링크 3.0 기술(Compute eXpress Link, 이하 CXL)을 활용해 검색 엔진을 위한 AI 반도체를 세계 최초로 개발했다고 25일 밝혔다.

최근 검색 서비스에서 사용되는 알고리즘은 근사 근접 이웃 탐색(Approximate Nearest Neighbor Search, ANNS)으로 어떤 데이터든지 특징 벡터로 표현할 수 있다. 특징 벡터란 데이터가 가지는 특징들 각각을 숫자로 표현해 나열한 것으로, 이들 사이의 거리를 통해 우리는 데이터 간의 유사도를 구할 수 있다. 하지만 벡터 데이터 용량이 매우 커서 이를 압축해 메모리에 적재하는 압축 방식과 메모리보다 큰 용량과 느린 속도를 가지는 저장 장치를 사용하는 스토리지 방식(마이크로소프트에서 사용 중)이 사용되어 왔다. 하지만 이들 각각은 낮은 정확도와 성능을 가지는 문제가 있었다.

이에 정명수 교수 연구팀은 메모리 확장의 제한이라는 근본적인 문제를 해결하기 위해 CXL이라는 기술에 주목했다. CXL은 CPU-장치 간 연결을 위한 프로토콜로, 가속기 및 메모리 확장기의 고속 연결을 제공한다. 또한 CXL 스위치를 통해 여러 대의 메모리 확장기를 하나의 포트에 연결할 수 있는 확장성을 제공한다. 하지만 CXL을 통한 메모리 확장은 로컬 메모리와 비교해 메모리 접근 시간이 증가하는 단점을 가지고 있다.

데이터를 책으로 비유하자면 기존 시스템은 집에 해당하는 CPU 크기의 제한으로 서재(메모리 용량)를 무한정 늘릴 수 없어, 보관할 수 있는 책 개수에 제한이 있는 것이다. 이에 압축 방식은 책의 내용을 압축하여 더 많은 책을 보관하는 방법이고, 스토리지 방식은 필요한 책들을 거리가 먼 도서관에서 구해오는 것과 비슷하다. CXL을 통한 메모리 확장은 집 옆에 창고를 지어 책을 보관하는 것으로 이해될 수 있다.

연구진이 개발한 AI 반도체(CXL-ANNS)는 CXL 스위치와 CXL 메모리 확장기를 사용해 근사 근접 이웃 탐색에서 필요한 모든 데이터를 메모리에 적재할 수 있어 정확도를 높이고 성능 감소를 없앴다. 또한 근사 근접 이웃 탐색의 특징을 활용해 데이터 근처 처리 기법과 지역성을 활용한 데이터 배치 기법으로 CXL-ANNS의 성능을 한 단계 향상했다. 이는 마치 창고 스스로가 필요한 책들의 내용을 요약하고 정리해 전달하고, 자주 보는 책들은 서재에 배치해 집과 창고를 오가는 시간을 줄이는 것과 유사하다.

연구진은 CXL-ANNS의 프로토타입을 자체 제작해 실효성을 확인하고, CXL-ANNS 성능을 기존 연구들과 비교했다. 마이크로소프트, 메타, 얀덱스 등의 글로벌 IT 기업에서 공개한 검색 데이터 셋을 사용한 근사 근접 이웃 탐색의 성능 비교에서 CXL-ANNS는 기존 연구들 대비 평균 111배 성능 향상이 있었다. 특히, 마이크로소프트의 상용화된 서비스에서 사용되는 방식과 비교하였을 때 92배의 성능 향상을 보여줬다.

정명수 교수는 "이번에 개발한 CXL-ANNS는 기존 검색 엔진의 문제였던 메모리 용량 제한 문제를 해결하고, CXL 기반의 메모리 확장이 실제 적용될 때 발생하는 메모리 접근 시간 지연 문제를 해결했다ˮ며, “제안하는 CXL 기반 메모리 확장과 데이터 근처 처리 가속의 패러다임은 검색 엔진뿐만 아니라 빅 데이터가 필요한 고성능 컴퓨팅, 유전자 탐색, 영상 처리 등의 다양한 분야에도 적용할 수 있다ˮ라고 말했다.

이번 연구는 미국 보스턴에서 오는 7월에 열릴 시스템 분야 최우수 학술대회인 유즈닉스 연례 회의 `USENIX Annual Technical Conference, 2023'에 ‘CXL-ANNS’이라는 이름으로 발표된 예정이다. (논문명: CXL-ANNS: Software-Hardware Collaborative Memory Disaggregation and Computation for Billion-Scale Approximate Nearest Neighbor Search)

한편 해당 연구는 파네시아(http://panmnesia.com)의 지원을 받아 진행됐다.

2023.05.25 조회수 9131 -

방사선에도 문제없는 초저에너지 메모리 최초 개발

지상에서 잘 동작하던 반도체 메모리가 우주나 비행기 안에서 갑자기 오동작을 일으키는 일이 있는데, 이는 고고도에 존재하는 방사선 때문이다. 이 뿐만 아니라, 최근 자율 주행 운송 수단과 같이 사람의 안전이 중요한 장치에 사용되는 반도체 메모리도 대기 방사선에 의해 오동작할 확률이 있다는 연구 결과들이 보고되면서 방사선에 대해 높은 안정성을 갖는 메모리 소자의 중요성이 점차 증가하고 있다.

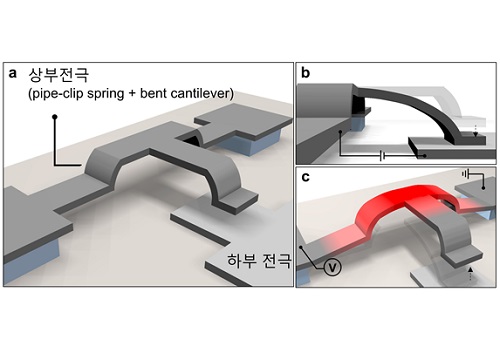

우리 대학 전기및전자공학부 윤준보 교수 연구팀이 나노종합기술원(원장 이조원) 강민호 박사와의 협업을 통해 우주 부품 수준의 내방사선 특성을 가지면서도 일반적인 비휘발성 플래시 메모리보다 30,000배 이상 프로그래밍 에너지가 낮은 나노 전자 기계식 비휘발성 메모리 소자를 세계 최초로 개발했다고 28일 밝혔다.

전기및전자공학부 이용복 박사과정이 제1 저자로 수행한 이번 연구는 저명 국제 학술지 `네이처 커뮤니케이션즈 (Nature Communications)' 2023년 1월호에 출판됐다. (논문명: Sub-10 fJ/bit radiation-hard nanoelectromechanical non-volatile memory). (Impact Factor : 17.690). (https://www.nature.com/articles/s41467-023-36076-0)

반도체 메모리 소자들은 동작 원리상 근본적으로 방사선에 취약해, 이를 보완하기 위해서는 복잡한 회로나 추가적인 데이터 프로세싱을 수반하는데 그 과정에서 많은 에너지가 소모된다. 즉, 일반적인 반도체 메모리 소자들은 내방사선과 낮은 동작 에너지를 동시에 만족하는 것이 매우 어렵다는 것을 의미한다.

윤준보 교수 연구팀은 방사선에 원천적으로 강인한 특성을 가진 나노 전자 기계 기술(Nano Electro Mechanical System, NEMS)을 활용해 고에너지 방사선에도 강인할 뿐만 아니라 매우 낮은 프로그래밍 에너지를 가지고, 전원이 공급되지 않아도 저장된 정보를 유지할 수 있는 비휘발성 메모리 소자를 세계 최초로 개발했다.

연구팀은 반도체 메모리를 사용하는 대신, 나노 크기의 매우 작은 기계 구조에 전기 신호를 가함으로써 나노 기계 구조체가 실제로 움직여서 하부 전극에 붙고 떨어지는 방식을 사용하였다. 또한, 매우 낮은 프로그래밍 에너지를 달성하기 위해 파이프-클립 스프링 구조와 구부러진 외팔보 구조로 구성된 상부 전극을 도입했으며, 특히 파이프-클립 모양의 나노 기계 구조에 전류를 가해 열을 내는 구동 방식을 통해 프로그램된 구조체가 초기 상태로 복구할 수 있도록 하여 반복적인 프로그램 동작에도 낮은 프로그래밍 에너지를 유지할 수 있도록 하였다.

연구진은 나노종합기술원의 반도체 장비·시설 인프라를 활용해 8인치 웨이퍼 수준의 대면적 기판에 신뢰적으로 소자를 제작했고, 제작한 나노 전자 기계식 비휘발성 메모리의 프로그래밍 에너지는 차세대 메모리들과 비교했을 때도 매우 낮은 수준이었다. 또한, 기계적인 움직임을 기반으로 하는 동작 방식 덕분에 고에너지 방사선 조사 후에도 누설 전류 증가, 동작 전압 변화, 비트 오작동 등의 성능 저하 없이 우수한 내방사선 특성을 보였다.

연구개발에 주도적으로 참여한 이용복 박사과정은 “이번 연구 결과는 연구팀이 보유한 나노 전자 기계 설계 기술과 나노종합기술원의 첨단 공정 기술이 만나 내방사선 특성과 낮은 동작 에너지 소모를 동시에 만족하는 비휘발성 메모리를 세계 최초로 구현했다는 점에서 중요한 의미를 가지고, 해당 기술은 우주 환경에서의 인공지능, 초안정성 자율주행 시스템 등 내방사선과 높은 에너지 효율성이 필요한 다양한 미래 응용 분야에서 핵심 기술이 될 것” 이라고 말했다. 또한, “세계 차세대 반도체 시장에서 우리나라가 메모리 원천 기술을 선도할 수 있도록 기여하고 싶다”며 앞으로의 계획을 밝혔다.

해당 기술과 관련해 미국, 중국, 대만, 한국 등에 6건의 특허가 출원돼 있다.

한편, 이번 연구는 한국연구재단의 차세대지능형반도체기술개발사업과 삼성전자의 지원을 받아 수행됐다.

2023.02.28 조회수 10278

방사선에도 문제없는 초저에너지 메모리 최초 개발

지상에서 잘 동작하던 반도체 메모리가 우주나 비행기 안에서 갑자기 오동작을 일으키는 일이 있는데, 이는 고고도에 존재하는 방사선 때문이다. 이 뿐만 아니라, 최근 자율 주행 운송 수단과 같이 사람의 안전이 중요한 장치에 사용되는 반도체 메모리도 대기 방사선에 의해 오동작할 확률이 있다는 연구 결과들이 보고되면서 방사선에 대해 높은 안정성을 갖는 메모리 소자의 중요성이 점차 증가하고 있다.

우리 대학 전기및전자공학부 윤준보 교수 연구팀이 나노종합기술원(원장 이조원) 강민호 박사와의 협업을 통해 우주 부품 수준의 내방사선 특성을 가지면서도 일반적인 비휘발성 플래시 메모리보다 30,000배 이상 프로그래밍 에너지가 낮은 나노 전자 기계식 비휘발성 메모리 소자를 세계 최초로 개발했다고 28일 밝혔다.

전기및전자공학부 이용복 박사과정이 제1 저자로 수행한 이번 연구는 저명 국제 학술지 `네이처 커뮤니케이션즈 (Nature Communications)' 2023년 1월호에 출판됐다. (논문명: Sub-10 fJ/bit radiation-hard nanoelectromechanical non-volatile memory). (Impact Factor : 17.690). (https://www.nature.com/articles/s41467-023-36076-0)

반도체 메모리 소자들은 동작 원리상 근본적으로 방사선에 취약해, 이를 보완하기 위해서는 복잡한 회로나 추가적인 데이터 프로세싱을 수반하는데 그 과정에서 많은 에너지가 소모된다. 즉, 일반적인 반도체 메모리 소자들은 내방사선과 낮은 동작 에너지를 동시에 만족하는 것이 매우 어렵다는 것을 의미한다.

윤준보 교수 연구팀은 방사선에 원천적으로 강인한 특성을 가진 나노 전자 기계 기술(Nano Electro Mechanical System, NEMS)을 활용해 고에너지 방사선에도 강인할 뿐만 아니라 매우 낮은 프로그래밍 에너지를 가지고, 전원이 공급되지 않아도 저장된 정보를 유지할 수 있는 비휘발성 메모리 소자를 세계 최초로 개발했다.

연구팀은 반도체 메모리를 사용하는 대신, 나노 크기의 매우 작은 기계 구조에 전기 신호를 가함으로써 나노 기계 구조체가 실제로 움직여서 하부 전극에 붙고 떨어지는 방식을 사용하였다. 또한, 매우 낮은 프로그래밍 에너지를 달성하기 위해 파이프-클립 스프링 구조와 구부러진 외팔보 구조로 구성된 상부 전극을 도입했으며, 특히 파이프-클립 모양의 나노 기계 구조에 전류를 가해 열을 내는 구동 방식을 통해 프로그램된 구조체가 초기 상태로 복구할 수 있도록 하여 반복적인 프로그램 동작에도 낮은 프로그래밍 에너지를 유지할 수 있도록 하였다.

연구진은 나노종합기술원의 반도체 장비·시설 인프라를 활용해 8인치 웨이퍼 수준의 대면적 기판에 신뢰적으로 소자를 제작했고, 제작한 나노 전자 기계식 비휘발성 메모리의 프로그래밍 에너지는 차세대 메모리들과 비교했을 때도 매우 낮은 수준이었다. 또한, 기계적인 움직임을 기반으로 하는 동작 방식 덕분에 고에너지 방사선 조사 후에도 누설 전류 증가, 동작 전압 변화, 비트 오작동 등의 성능 저하 없이 우수한 내방사선 특성을 보였다.

연구개발에 주도적으로 참여한 이용복 박사과정은 “이번 연구 결과는 연구팀이 보유한 나노 전자 기계 설계 기술과 나노종합기술원의 첨단 공정 기술이 만나 내방사선 특성과 낮은 동작 에너지 소모를 동시에 만족하는 비휘발성 메모리를 세계 최초로 구현했다는 점에서 중요한 의미를 가지고, 해당 기술은 우주 환경에서의 인공지능, 초안정성 자율주행 시스템 등 내방사선과 높은 에너지 효율성이 필요한 다양한 미래 응용 분야에서 핵심 기술이 될 것” 이라고 말했다. 또한, “세계 차세대 반도체 시장에서 우리나라가 메모리 원천 기술을 선도할 수 있도록 기여하고 싶다”며 앞으로의 계획을 밝혔다.

해당 기술과 관련해 미국, 중국, 대만, 한국 등에 6건의 특허가 출원돼 있다.

한편, 이번 연구는 한국연구재단의 차세대지능형반도체기술개발사업과 삼성전자의 지원을 받아 수행됐다.

2023.02.28 조회수 10278 -

획기적 음의 정전용량 플래시 메모리 최초 개발

우리 대학 전기및전자공학부 전상훈 교수 연구팀이 `음의 정전용량 효과(Negative Capacitance Effect, 이하 NC 효과)*'를 활용해 기존 플래시 메모리의 물리적 성능 한계를 뛰어넘는 음의 정전용량 플래시 메모리 (NC-Flash Memory)를 세계 최초로 개발했다고 18일 밝혔다.

*음의 정전용량 효과: 음의 정전용량 현상은 인가되는 전압이 증가하면 전하량이 감소함을 의미한다. 음의 정전용량 특성을 가지는 유전체 사용시, 트랜지스터에 인가되는 전압을 내부적으로 증폭하여 상대적으로 낮은 동작전압을 사용할 수 있어, 파워소모를 줄일 수 있다.

전기및전자공학부 김태호 박사과정과 김기욱 박사과정이 공동 제1 저자로 수행한 이번 연구는 저명 국제 학술지 `어드밴스드 펑셔널 머터리얼즈(Advanced Functional Materials)' 2022년 12월호에 출판됐다. (논문명 : The Opportunity of Negative Capacitance Behavior in Flash Memory for High-Density and Energy-Efficient In-Memory Computing Applications) 이 국제학술지는 독일 와일리 출판사(Wiley-VCH)에서 발행하는 피어리뷰 과학 저널이다. (Impact Factor : 19.924)

현대 전자 소자에서 축전기(Capacitor)는 매우 중요한 구성 요소의 하나로, 전자 소자가 소형화되고 수직 방향으로 적층 되면서 축전기에 저장되는 전하량(Charge, Q)이 감소하는 문제가 생기므로 높은 정전용량(Capacitance, C)을 가진 유전체 물질이 필수적으로 요구되고 있다. 여기에 일반적인 축전기와 다르게 정전용량이 음의 값을 갖는(Negative Capacitance) 축전기를 활용한다면 다층의 축전기의 전체 정전용량을 오히려 더 증가시킬 수 있고, 차세대 소자에 적합한 높은 정전용량 소자 개발 난제를 해결할 수 있을 것이라는 가설이 제안되었다.

최근 메모리 공급업체들은 데이터의 폭발적 증가와 더 높은 용량의 솔리드 스테이트 드라이브(SSD) 및 더 빠른 액세스 시간에 대한 요구로 인해 기술 경쟁을 치열하게 하고 있다. 스토리지의 핵심 기술인 3D 낸드 플래시는 지속적으로 더 높은 층을 적층할 수 있는 기술을 요구하고 있고, 2028년에는 1,000단 이상의 메모리 적층이 필요할 것으로 예상되고 있다.

한편, 강유전체* 물질에서 보이는 `음의 정전용량 효과(NC 효과)'은 전자 소자에 인가된 외부 전압을 내부적으로 증폭해 전력 소모를 줄이는 특성이 있어, 전자 소자의 물리적 성능 한계를 극복할 수 있다는 가능성이 제시됐다. 최근 페로브스카이트 강유전체에서 NC 효과를 실험적으로 관찰했으나, 페로브스카이트 강유전체의 소형화 한계 및 CMOS 공정과의 부적합성으로 인해 NC 효과를 활용한 전자 소자의 구현에 대해 상당한 회의론을 불러일으켰다.

*강유전체: 전기적으로는 절연체이지만 자연상태에서 외부 전기장이 없어도 전기 편극을 지닐 수 있는 특이한 물리적 성질을 가진 물질

전상훈 교수 연구팀은 기존 플래시 메모리의 물리적 성능 한계를 극복하고 동작전압을 낮추기 위해, 반도체 공정에 사용되는 하프늄옥사이드(HfO2) 강유전체 박막의 NC 효과를 안정화해 저전압 구동이 가능한 강유전체 소재의 NC-플래시 메모리를 세계 최초로 개발했다. 개발된 NC-플래시 메모리는 기존 플래시 메모리 대비 전력 소모가 10,000배 이상 낮은 저전력 고성능 특성을 달성했다.

연구팀은 그뿐만 아니라 기존 컴퓨팅 구조인 폰노이만 아키텍처를 대체하여 새롭게 지향하는 인메모리 컴퓨팅을 NC-플래시 메모리를 기반으로 구현해 세계 최고 수준의 에너지 효율 또한 달성했다.

이번 연구 결과는 빠른 스토리지를 필요로 하는 최신 컴퓨팅과 네트워킹의 요구를 충족하는 차세대 낸드 플래시 메모리 개발에 있어 핵심 역할을 할 것이다.

한편, 이번 연구는 연세대학교와 협업을 통해서 이루어졌고, 한국 연구재단 지능형 반도체 기술개발사업의 지원을 받아 수행됐다.

2023.01.18 조회수 9852

획기적 음의 정전용량 플래시 메모리 최초 개발

우리 대학 전기및전자공학부 전상훈 교수 연구팀이 `음의 정전용량 효과(Negative Capacitance Effect, 이하 NC 효과)*'를 활용해 기존 플래시 메모리의 물리적 성능 한계를 뛰어넘는 음의 정전용량 플래시 메모리 (NC-Flash Memory)를 세계 최초로 개발했다고 18일 밝혔다.

*음의 정전용량 효과: 음의 정전용량 현상은 인가되는 전압이 증가하면 전하량이 감소함을 의미한다. 음의 정전용량 특성을 가지는 유전체 사용시, 트랜지스터에 인가되는 전압을 내부적으로 증폭하여 상대적으로 낮은 동작전압을 사용할 수 있어, 파워소모를 줄일 수 있다.

전기및전자공학부 김태호 박사과정과 김기욱 박사과정이 공동 제1 저자로 수행한 이번 연구는 저명 국제 학술지 `어드밴스드 펑셔널 머터리얼즈(Advanced Functional Materials)' 2022년 12월호에 출판됐다. (논문명 : The Opportunity of Negative Capacitance Behavior in Flash Memory for High-Density and Energy-Efficient In-Memory Computing Applications) 이 국제학술지는 독일 와일리 출판사(Wiley-VCH)에서 발행하는 피어리뷰 과학 저널이다. (Impact Factor : 19.924)

현대 전자 소자에서 축전기(Capacitor)는 매우 중요한 구성 요소의 하나로, 전자 소자가 소형화되고 수직 방향으로 적층 되면서 축전기에 저장되는 전하량(Charge, Q)이 감소하는 문제가 생기므로 높은 정전용량(Capacitance, C)을 가진 유전체 물질이 필수적으로 요구되고 있다. 여기에 일반적인 축전기와 다르게 정전용량이 음의 값을 갖는(Negative Capacitance) 축전기를 활용한다면 다층의 축전기의 전체 정전용량을 오히려 더 증가시킬 수 있고, 차세대 소자에 적합한 높은 정전용량 소자 개발 난제를 해결할 수 있을 것이라는 가설이 제안되었다.

최근 메모리 공급업체들은 데이터의 폭발적 증가와 더 높은 용량의 솔리드 스테이트 드라이브(SSD) 및 더 빠른 액세스 시간에 대한 요구로 인해 기술 경쟁을 치열하게 하고 있다. 스토리지의 핵심 기술인 3D 낸드 플래시는 지속적으로 더 높은 층을 적층할 수 있는 기술을 요구하고 있고, 2028년에는 1,000단 이상의 메모리 적층이 필요할 것으로 예상되고 있다.

한편, 강유전체* 물질에서 보이는 `음의 정전용량 효과(NC 효과)'은 전자 소자에 인가된 외부 전압을 내부적으로 증폭해 전력 소모를 줄이는 특성이 있어, 전자 소자의 물리적 성능 한계를 극복할 수 있다는 가능성이 제시됐다. 최근 페로브스카이트 강유전체에서 NC 효과를 실험적으로 관찰했으나, 페로브스카이트 강유전체의 소형화 한계 및 CMOS 공정과의 부적합성으로 인해 NC 효과를 활용한 전자 소자의 구현에 대해 상당한 회의론을 불러일으켰다.

*강유전체: 전기적으로는 절연체이지만 자연상태에서 외부 전기장이 없어도 전기 편극을 지닐 수 있는 특이한 물리적 성질을 가진 물질

전상훈 교수 연구팀은 기존 플래시 메모리의 물리적 성능 한계를 극복하고 동작전압을 낮추기 위해, 반도체 공정에 사용되는 하프늄옥사이드(HfO2) 강유전체 박막의 NC 효과를 안정화해 저전압 구동이 가능한 강유전체 소재의 NC-플래시 메모리를 세계 최초로 개발했다. 개발된 NC-플래시 메모리는 기존 플래시 메모리 대비 전력 소모가 10,000배 이상 낮은 저전력 고성능 특성을 달성했다.

연구팀은 그뿐만 아니라 기존 컴퓨팅 구조인 폰노이만 아키텍처를 대체하여 새롭게 지향하는 인메모리 컴퓨팅을 NC-플래시 메모리를 기반으로 구현해 세계 최고 수준의 에너지 효율 또한 달성했다.

이번 연구 결과는 빠른 스토리지를 필요로 하는 최신 컴퓨팅과 네트워킹의 요구를 충족하는 차세대 낸드 플래시 메모리 개발에 있어 핵심 역할을 할 것이다.

한편, 이번 연구는 연세대학교와 협업을 통해서 이루어졌고, 한국 연구재단 지능형 반도체 기술개발사업의 지원을 받아 수행됐다.

2023.01.18 조회수 9852 -

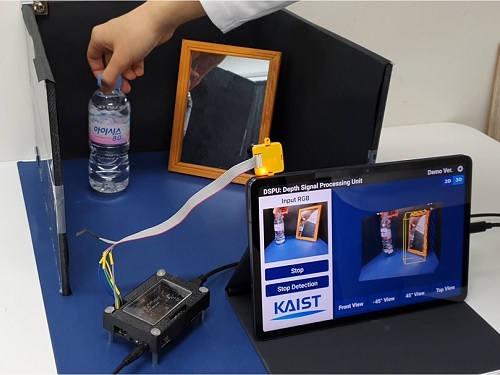

사진에서 3차원 정보를 추론하는 인공지능 반도체 IP(지식재산권) 세계 최초 개발

우리 대학 전기및전자공학부 유회준 교수가 이끄는 PIM 반도체 설계 연구센터(AI-PIM)가 유수 학계에서 인정한 5종의 최첨단 인공지능 반도체 IP(지식재산권)를 개발했다고 29일 밝혔다.

대표적으로 심층신경망 추론 기술 및 센서 퓨전* 기술을 통해 사진으로부터 3차원 공간정보 추출하고 물체를 인식해 처리하는 인공지능(AI) 칩은 KAIST에서 세계 최초로 개발해 SRAM PIM** 시스템에 필요한 기술을 IP(지식재산권)화 한 것이다.

* 센서 퓨전 : 카메라, 거리센서 등의 각종 센서로부터 얻은 데이터를 결합하여보다 정확한 데이터를 얻는 방식

** SRAM PIM : 기존 메모리 SRAM과 DRAM 중 SRAM에 연산기를 결합한 PIM반도체

이 IP는 올해 2월 20일부터 28일까지 개최된 국제고체회로설계학회(ISSCC)에서 현장 시연을 통해 많은 주목을 받았으며, 이를 누구라도 편리하게 활용할 수 있도록 한 것이다. (웹사이트 : www.ai-pim.org)

KAIST PIM 반도체 설계연구센터는 해당 IP를 포함해 ADC*, PLL** 등 총 5가지의 PIM IP를 확보했으며, 지난 28일 웹사이트를 오픈해 연구자들이 공유할 수 있는 환경을 제공하고 있다.

* ADC(Analog to Digital Converter) : 아날로그 데이터를 디지털 데이터로 변환시키는 회로

** PLL(Phase-Locked Loop) : 내부 신호의 위상과 외부 신호의 위상을 동기화할 수 있도록 설계된 회로

기존 물체 인식 인공지능 반도체는 사진과 같은 2차원 정보를 인식하는 `사진인식기술'에 불과하다. 하지만 현실 세계의 물체들은 3차원 구조물이기 때문에 3차원 공간정보를 활용해야만 정확한 `물체인식'이 가능하다.

3차원 공간정보는 사진과 같은 2차원 정보에 거리정보를 포함시켜 실제 3차원 공간을 표현한 것으로, 3차원 공간정보에 물체를 식별해 해당 물체의 위치 및 각도를 추적하는 3차원 물체인식 기술이다. 이는 자율주행, 자동화 기술, 개인용 증강현실 (AR)과 가상현실(VR) 등과 같은 3D 어플리케이션에서 사용하는 핵심기술이다.

기존 ToF 센서*를 활용해 센서 뷰 내에 있는 모든 물체에 대한 정밀한 3차원 정보를 추출하는 것은 전력 소모가 매우 크기 때문에 배터리 기반 모바일 장치(스마트폰, 태블릿 등)에서는 사용하기 어렵다.

* ToF 센서 : 3차원 공간정보를 추출하는 Time-of-Flight 센서로, 레이저를 방출하고 반사된 레이저가 검출되는 시간을 측정하여 거리를 계산, 대표적인 센서로 3D 라이다 (LiDAR) 센서가 있음

또한, ToF 센서는 특정 측정 환경에서 3차원 정보가 손실되는 문제와 데이터 전처리 과정에 많은 시간이 소요된다는 문제점이 있다.

3차원 물체인식 기술은 데이터가 복잡해 기존 인공지능 2차원 사진인식 가속 프로세서로 처리하기 어렵다. 이는 3차원 포인트 클라우드 데이터를 어떻게 선택하고 그룹화하느냐에 따라 메모리 접근량이 달라진다.

따라서 3차원 포인트 클라우드 기반 인공지능 추론은 연산 능력이 제한적이고 메모리가 작은 모바일 장치에서는 소프트웨어만으로 구현할 수 없었다.

이에 연구팀은 카메라와 저전력 거리센서 (64픽셀)를 사용하여 3차원 공간정보를 생성했고, 모바일에서도 3차원 어플리케이션 구현이 가능한 반도체 (DSPU: Depth Signal Processing Unit)를 개발함으로써 인공지능 반도체의 활용범위를 넓혔다.

모바일 기기에서 저전력 센서를 활용한 3차원 정보 처리 시스템을 구동하면서, 실시간 심층신경망 추론과 센서 퓨전 기술을 가속하기 위해서는 다양한 핵심기술이 필요하다. 인공지능 핵심기술이 적용된 DSPU는 단순 ToF센서에 의존했던 3차원 물체인식 가속기 반도체 대비 63.4% 낮춘 전력 소모와 53.6% 낮춘 지연시간을 달성했다.

PIM반도체 설계연구센터(AI-PIM)의 소장인 유회준 교수는 “이번 연구는 저가의 거리센서와 카메라를 융합해 3차원 데이터 처리를 가능하게 한 인공지능 반도체를 IP화했다는 점에서 의미가 크며, 모바일 기기에서 인공지능 활용 영역을 크게 넓혀 다양한 분야에 응용 및 기술이전을 기대하고 있다”고 연구의 의의를 설명했다.

한편, 이번 연구는 과학기술정보통신부와 정보통신기획평가원의 PIM인공지능반도체핵심기술개발사업을 통해 개발되었으며, 이와 관련해 PIM 반도체 관련 기업과 연구기관에 개발된 IP들의 기술이전 및 활용을 돕고 있다.

2022.12.29 조회수 9761

사진에서 3차원 정보를 추론하는 인공지능 반도체 IP(지식재산권) 세계 최초 개발

우리 대학 전기및전자공학부 유회준 교수가 이끄는 PIM 반도체 설계 연구센터(AI-PIM)가 유수 학계에서 인정한 5종의 최첨단 인공지능 반도체 IP(지식재산권)를 개발했다고 29일 밝혔다.

대표적으로 심층신경망 추론 기술 및 센서 퓨전* 기술을 통해 사진으로부터 3차원 공간정보 추출하고 물체를 인식해 처리하는 인공지능(AI) 칩은 KAIST에서 세계 최초로 개발해 SRAM PIM** 시스템에 필요한 기술을 IP(지식재산권)화 한 것이다.

* 센서 퓨전 : 카메라, 거리센서 등의 각종 센서로부터 얻은 데이터를 결합하여보다 정확한 데이터를 얻는 방식

** SRAM PIM : 기존 메모리 SRAM과 DRAM 중 SRAM에 연산기를 결합한 PIM반도체

이 IP는 올해 2월 20일부터 28일까지 개최된 국제고체회로설계학회(ISSCC)에서 현장 시연을 통해 많은 주목을 받았으며, 이를 누구라도 편리하게 활용할 수 있도록 한 것이다. (웹사이트 : www.ai-pim.org)

KAIST PIM 반도체 설계연구센터는 해당 IP를 포함해 ADC*, PLL** 등 총 5가지의 PIM IP를 확보했으며, 지난 28일 웹사이트를 오픈해 연구자들이 공유할 수 있는 환경을 제공하고 있다.

* ADC(Analog to Digital Converter) : 아날로그 데이터를 디지털 데이터로 변환시키는 회로

** PLL(Phase-Locked Loop) : 내부 신호의 위상과 외부 신호의 위상을 동기화할 수 있도록 설계된 회로

기존 물체 인식 인공지능 반도체는 사진과 같은 2차원 정보를 인식하는 `사진인식기술'에 불과하다. 하지만 현실 세계의 물체들은 3차원 구조물이기 때문에 3차원 공간정보를 활용해야만 정확한 `물체인식'이 가능하다.

3차원 공간정보는 사진과 같은 2차원 정보에 거리정보를 포함시켜 실제 3차원 공간을 표현한 것으로, 3차원 공간정보에 물체를 식별해 해당 물체의 위치 및 각도를 추적하는 3차원 물체인식 기술이다. 이는 자율주행, 자동화 기술, 개인용 증강현실 (AR)과 가상현실(VR) 등과 같은 3D 어플리케이션에서 사용하는 핵심기술이다.

기존 ToF 센서*를 활용해 센서 뷰 내에 있는 모든 물체에 대한 정밀한 3차원 정보를 추출하는 것은 전력 소모가 매우 크기 때문에 배터리 기반 모바일 장치(스마트폰, 태블릿 등)에서는 사용하기 어렵다.

* ToF 센서 : 3차원 공간정보를 추출하는 Time-of-Flight 센서로, 레이저를 방출하고 반사된 레이저가 검출되는 시간을 측정하여 거리를 계산, 대표적인 센서로 3D 라이다 (LiDAR) 센서가 있음

또한, ToF 센서는 특정 측정 환경에서 3차원 정보가 손실되는 문제와 데이터 전처리 과정에 많은 시간이 소요된다는 문제점이 있다.

3차원 물체인식 기술은 데이터가 복잡해 기존 인공지능 2차원 사진인식 가속 프로세서로 처리하기 어렵다. 이는 3차원 포인트 클라우드 데이터를 어떻게 선택하고 그룹화하느냐에 따라 메모리 접근량이 달라진다.

따라서 3차원 포인트 클라우드 기반 인공지능 추론은 연산 능력이 제한적이고 메모리가 작은 모바일 장치에서는 소프트웨어만으로 구현할 수 없었다.

이에 연구팀은 카메라와 저전력 거리센서 (64픽셀)를 사용하여 3차원 공간정보를 생성했고, 모바일에서도 3차원 어플리케이션 구현이 가능한 반도체 (DSPU: Depth Signal Processing Unit)를 개발함으로써 인공지능 반도체의 활용범위를 넓혔다.

모바일 기기에서 저전력 센서를 활용한 3차원 정보 처리 시스템을 구동하면서, 실시간 심층신경망 추론과 센서 퓨전 기술을 가속하기 위해서는 다양한 핵심기술이 필요하다. 인공지능 핵심기술이 적용된 DSPU는 단순 ToF센서에 의존했던 3차원 물체인식 가속기 반도체 대비 63.4% 낮춘 전력 소모와 53.6% 낮춘 지연시간을 달성했다.

PIM반도체 설계연구센터(AI-PIM)의 소장인 유회준 교수는 “이번 연구는 저가의 거리센서와 카메라를 융합해 3차원 데이터 처리를 가능하게 한 인공지능 반도체를 IP화했다는 점에서 의미가 크며, 모바일 기기에서 인공지능 활용 영역을 크게 넓혀 다양한 분야에 응용 및 기술이전을 기대하고 있다”고 연구의 의의를 설명했다.

한편, 이번 연구는 과학기술정보통신부와 정보통신기획평가원의 PIM인공지능반도체핵심기술개발사업을 통해 개발되었으며, 이와 관련해 PIM 반도체 관련 기업과 연구기관에 개발된 IP들의 기술이전 및 활용을 돕고 있다.

2022.12.29 조회수 9761 -

스핀 소자 기반 물리적 복제방지 보안기술 개발

우리 대학 신소재공학과 박병국 교수팀이 물리학과 김갑진 교수 연구팀 및 현대자동차와 공동연구를 통해 자성메모리(Magnetic random-access memory, MRAM)를 기반으로 사람의 지문과 같이 매번 다른 패턴을 갖는 하드웨어 보안인증 원천 기술을 개발하는 데 성공했다고 30일 밝혔다.

박병국 교수 연구팀은 반강자성체-하부강자성체-비자성체-상부강자성체 다층박막 구조에서 무자기장(field-free) 스핀-궤도 토크(spin-orbit torque, SOT)로 동작하는 MRAM 소자의 스위칭 극성을 무작위적으로 분포시켜 물리적 복제 불가능성(physical unclonable function, 이하 PUF)을 지닌 보안소자를 개발하는 것이 가능함을 입증했다. 이 기술은 고온 및 고자기장 등의 환경에서도 높은 동작 신뢰도 및 무작위성을 유지하면서 작동 가능해 사물인터넷(IoT)을 비롯한 다양한 보안시스템에 응용될 수 있을 것으로 기대된다.

PUF를 이용한 하드웨어 기반 보안 소자는 동일한 공정 과정을 통해 제작해도 공정 편차에서 발생하는 제어되거나 예측할 수 없는 반도체소재/소자 간의 차이를 이용해 보안용 인증키를 형성하는 기술이다. 이는 기존 소프트웨어 기반 보안시스템과 다르게 외부 공격에 대해 높은 저항성을 지니는 장점이 있기에 최근 증가하고 있는 사물인터넷 기기 해킹 등의 보안 위협을 해결할 기술로 주목받고 있다.

하지만 기존에 주로 연구됐던 상보적 금속 산화물 반도체(complementary metal oxide semiconductor, CMOS) 소자 기반 물리적 복제방지기술은 외부 환경 변화에 민감하며 반복 동작 시 신뢰도가 낮아지는 문제점이 있다. 이에 반해 자성메모리(magnetic random-access memory, MRAM)를 포함한 자화를 이용해 정보를 저장하는 스핀트로닉스 기반 소자는 높은 내구성 및 안정성을 지니고 있고 환경 변화에 비교적 민감하지 않다. 따라서 이러한 특성을 이용해 물리적 복제방지기술을 개발한다면 현행 반도체 공정 기술과 호환이 가능하며 보안인증 등 다양한 활용 범위를 가지는 비휘발성 메모리 기반 보안 기술 개발을 기대할 수 있다.

신소재공학과 이수길 박사와 강재민 박사과정이 공동 제1 저자로 참여한 이번 연구는 국제 학술지 `어드벤스드 머티리얼스(Advanced Materials)'에 11월 10일 字 온라인 게재됐다. (논문명 : Spintronic physical unclonable functions based on field-free spin-orbit torque switching)

연구팀은 교환결합이 형성된 다층박막을 제작해 고온에서 교류 자기장 인가를 통해 교환결합의 방향의 좌우로 50:50의 비율을 갖는 무작위한 분포 생성했다. [그림1(a)] 이때 생성된 교환결합의 방향이 상부 강자성체의 무자기장 스위칭 부호를 결정하는 성질을 이용해 무작위한 분포 방향을 전기적으로 0과1의 이진법분포로 바꿔 출력했으며 이를 보안키로 활용하는 물리적 복제 방지 기술을 개발했다. [그림1(b) 및 1(c)]

연구팀이 개발한 스핀 기반 물리적 복제방지 기술은 50,000번 이상의 반복 동작 시에도 에러가 발생하지 않는 높은 내구성을 보이며 반도체소자가 기본적으로 요구하는 -100℃부터 125℃까지 넓은 온도 범위에서도 안정적으로 작동한다. 또한 무작위성의 원천으로 교환결합의 방향을 이용했기 때문에 자성체 기반 소자임에도 불구하고 외부 자기장을 이용해 저장된 무작위분포를 바꾸지 못하는 것을 확인했다.

공동 제1 저자인 이수길 박사와 강재민 연구원은 "이번 연구는 차세대 MRAM의 주요 기술인 스핀-궤도 토크 기반으로 보안소자 기술을 개발할 수 있다는 것을 제시한 것에 의미가 있으며 향후 유력한 차세대 메모리인 MRAM에 보안 소자 기술을 접목하는 연구가 활발히 이뤄질 것으로 예상 된다ˮ고 밝혔다.

한편 이번 연구는 현대자동차 및 과학기술정보통신부 PIM인공지능반도체핵심기술개발 사업과 중견연구자지원 사업 연구과제의 지원을 받아 수행됐다.

2022.12.02 조회수 8964

스핀 소자 기반 물리적 복제방지 보안기술 개발

우리 대학 신소재공학과 박병국 교수팀이 물리학과 김갑진 교수 연구팀 및 현대자동차와 공동연구를 통해 자성메모리(Magnetic random-access memory, MRAM)를 기반으로 사람의 지문과 같이 매번 다른 패턴을 갖는 하드웨어 보안인증 원천 기술을 개발하는 데 성공했다고 30일 밝혔다.

박병국 교수 연구팀은 반강자성체-하부강자성체-비자성체-상부강자성체 다층박막 구조에서 무자기장(field-free) 스핀-궤도 토크(spin-orbit torque, SOT)로 동작하는 MRAM 소자의 스위칭 극성을 무작위적으로 분포시켜 물리적 복제 불가능성(physical unclonable function, 이하 PUF)을 지닌 보안소자를 개발하는 것이 가능함을 입증했다. 이 기술은 고온 및 고자기장 등의 환경에서도 높은 동작 신뢰도 및 무작위성을 유지하면서 작동 가능해 사물인터넷(IoT)을 비롯한 다양한 보안시스템에 응용될 수 있을 것으로 기대된다.

PUF를 이용한 하드웨어 기반 보안 소자는 동일한 공정 과정을 통해 제작해도 공정 편차에서 발생하는 제어되거나 예측할 수 없는 반도체소재/소자 간의 차이를 이용해 보안용 인증키를 형성하는 기술이다. 이는 기존 소프트웨어 기반 보안시스템과 다르게 외부 공격에 대해 높은 저항성을 지니는 장점이 있기에 최근 증가하고 있는 사물인터넷 기기 해킹 등의 보안 위협을 해결할 기술로 주목받고 있다.

하지만 기존에 주로 연구됐던 상보적 금속 산화물 반도체(complementary metal oxide semiconductor, CMOS) 소자 기반 물리적 복제방지기술은 외부 환경 변화에 민감하며 반복 동작 시 신뢰도가 낮아지는 문제점이 있다. 이에 반해 자성메모리(magnetic random-access memory, MRAM)를 포함한 자화를 이용해 정보를 저장하는 스핀트로닉스 기반 소자는 높은 내구성 및 안정성을 지니고 있고 환경 변화에 비교적 민감하지 않다. 따라서 이러한 특성을 이용해 물리적 복제방지기술을 개발한다면 현행 반도체 공정 기술과 호환이 가능하며 보안인증 등 다양한 활용 범위를 가지는 비휘발성 메모리 기반 보안 기술 개발을 기대할 수 있다.

신소재공학과 이수길 박사와 강재민 박사과정이 공동 제1 저자로 참여한 이번 연구는 국제 학술지 `어드벤스드 머티리얼스(Advanced Materials)'에 11월 10일 字 온라인 게재됐다. (논문명 : Spintronic physical unclonable functions based on field-free spin-orbit torque switching)

연구팀은 교환결합이 형성된 다층박막을 제작해 고온에서 교류 자기장 인가를 통해 교환결합의 방향의 좌우로 50:50의 비율을 갖는 무작위한 분포 생성했다. [그림1(a)] 이때 생성된 교환결합의 방향이 상부 강자성체의 무자기장 스위칭 부호를 결정하는 성질을 이용해 무작위한 분포 방향을 전기적으로 0과1의 이진법분포로 바꿔 출력했으며 이를 보안키로 활용하는 물리적 복제 방지 기술을 개발했다. [그림1(b) 및 1(c)]

연구팀이 개발한 스핀 기반 물리적 복제방지 기술은 50,000번 이상의 반복 동작 시에도 에러가 발생하지 않는 높은 내구성을 보이며 반도체소자가 기본적으로 요구하는 -100℃부터 125℃까지 넓은 온도 범위에서도 안정적으로 작동한다. 또한 무작위성의 원천으로 교환결합의 방향을 이용했기 때문에 자성체 기반 소자임에도 불구하고 외부 자기장을 이용해 저장된 무작위분포를 바꾸지 못하는 것을 확인했다.

공동 제1 저자인 이수길 박사와 강재민 연구원은 "이번 연구는 차세대 MRAM의 주요 기술인 스핀-궤도 토크 기반으로 보안소자 기술을 개발할 수 있다는 것을 제시한 것에 의미가 있으며 향후 유력한 차세대 메모리인 MRAM에 보안 소자 기술을 접목하는 연구가 활발히 이뤄질 것으로 예상 된다ˮ고 밝혔다.

한편 이번 연구는 현대자동차 및 과학기술정보통신부 PIM인공지능반도체핵심기술개발 사업과 중견연구자지원 사업 연구과제의 지원을 받아 수행됐다.

2022.12.02 조회수 8964 -

인공지능 및 빅데이터 시대를 이끌어갈 차세대 CXL2.0 메모리 확장 플랫폼 세계 최초 개발

우리 대학 전기및전자공학부 정명수 교수 연구팀(컴퓨터 아키텍처 및 메모리 시스템 연구실)이 대용량 메모리 장치부터 프로세스를 포함한 컴퓨트 익스프레스 링크(CXL) 2.0 기반의 차세대 메모리 확장 플랫폼 ‘다이렉트CXL(이하 DirectCXL)’을 세계 최초로 프로토타입 제작, 운영체제가 실장된 단대단(End-to-End) 시연에 성공했다고 1일 밝혔다.

오늘날 빅데이터 분석, 그래프 분석, 인메모리 데이터베이스 등 대규모 데이터에 기반한 응용처리가 증가함에 따라, 데이터 센터에서는 이를 더 빠르고 효율적으로 처리하기 위해 시스템의 메모리 확장에 많은 투자를 하고 있다.

그러나 우리가 흔히 알고 있는 메모리 확장 방식인 더블 데이터 대역폭(DDR) 인터페이스를 통한 메모리 확장은 추가할 수 있는 메모리 개수의 제한이 있어, 대규모 데이터 기반의 응용을 처리하기에 충분치 않다. 따라서 데이터 센터에서는 CPU와 메모리로 이루어진 메모리 노드들을 따로 구성하고, 응용을 수행하는 호스트의 메모리가 부족하면 네트워크로 연결된 메모리 노드를 자신의 메모리 공간으로 사용하는 원격 데이터 전송 기술(이하 RDMA) 기반의 메모리 확장을 사용한다.

여러 메모리 노드를 사용하는 RDMA 기반의 메모리 확장을 통해 데이터센터는 시스템의 메모리 크기를 늘릴 수 있었지만, 여전히 해결해야 할 문제들이 남아있었다. 우선 RDMA 기반 메모리 확장 시스템에서는 노드 간 데이터 이동 시 불필요한 데이터 복사, 소프트웨어의 개입 그리고 프로토콜 전환으로 인한 지연을 발생시켜 성능 저하가 발생했다. 또한 시스템의 메모리 확장 시 메모리만을 추가할 수 있는 것이 아닌, 메모리와 메모리를 제어할 CPU가 하나의 메모리 노드를 이루어 시스템에 추가되어야 했기 때문에, 추가적인 비용 소모가 발생했다.

최근 컴퓨트 익스프레스 링크(Compute Express Link, 이하 CXL) 프로토콜의 등장으로 많은 메모리 고객사와 제조사가 이러한 문제를 해결할 가능성을 확인하고 있다. CXL은 PCI 익스프레스(PCIe) 인터페이스 기반의 CPU-장치(Device) 간 연결을 위한 프로토콜로, 이를 기반으로 한 장치 연결은 기존보다 높은 성능과 확장성을 지원하는 것이 특징이다.

국내외 유수 기업들이 모여 CXL 인터페이스 표준 규약을 제안하는 CXL 컨소시엄은 지난 2019년 CXL 1.0/1.1을 처음 제안했고, 이후 CXL 2.0을 발표하며 CXL 1.0/1.1에서 하나의 포트당 하나의 지역 메모리 장치만을 연결할 수 있었던 확장성 문제를 스위치 네트워크를 통해 개선, 하나의 포트를 여러 포트로 확장할 수 있도록 했다. 따라서 CXL 1.0/1.1과 달리 CXL 2.0에서는 확장된 포트에 다수의 원격 CXL 메모리 장치를 연결하는 것이 가능해 더 높은 확장성을 지원할 수 있게 됐다.

그러나 CXL 2.0의 높은 확장성에도 불구하고, 아직 CXL 연구의 방향성을 제시해줄 수 있는 시제품 개발 및 연구들이 진행되지 않아, 메모리 업계와 학계에서는 여전히 CXL1.0/1.1을 기반으로 지역 메모리 확장 장치, 시제품 개발 및 연구를 진행하고 있는 실정이다. 따라서 새로운 CXL 2.0을 통한 메모리 확장 연구의 방향성 초석을 제시할 필요성이 커졌다.

정명수 교수 연구팀이 전 세계 최초로 프로토타입한 CXL 2.0 기반 메모리 확장 플랫폼 ‘DirectCXL’은 높은 수준의 메모리 확장성을 제공하며, 빠른 속도로 대규모 데이터 처리를 가능케 한다. 이를 위해 연구팀은 메모리를 확장해 줄 장치인 ‘CXL 메모리 장치’와 호스트 ‘CXL 프로세서 (CPU)’, 여러 호스트를 다수의 CXL 메모리 장치에 연결해주는 ‘CXL 네트워크 스위치’ 그리고 메모리 확장 플랫폼 전반을 제어할 리눅스 운영체제 기반의‘CXL 소프트웨어 모듈’을 개발해 플랫폼을 구성했다.

구성된 ‘DirectCXL’ 플랫폼을 사용한 시스템에서는 확장된 메모리 공간에 직접 접근해 데이터를 CPU의 캐시로 가져와 불필요한 메모리 복사와 소프트웨어의 개입이 없으며, PCIe 인터페이스만을 사용해 프로토콜 전환을 없애 지연시간을 최대한 줄였다. 또한 추가적인 CPU가 필요 없는 CXL 메모리 장치를 CXL 스위치에 연결하는 것만으로 메모리 확장이 가능해 효율적인 시스템의 구성이 가능했다. 국내외 소수 대기업에서 메모리 장치 일부 단품에 대한 구성을 보여준 준 사례는 있지만, CXL 2.0 기반, CPU부터 CXL 스위치, 메모리 장치가 장착된 시스템에서 운영체제를 동작시키고 데이터 센터와 응용을 실행하고 시연한 것은 정명수 교수 연구팀이 처음이다.

연구팀은 자체 제작한 메모리 확장 플랫폼 ‘DirectCXL’의 성능을 검증하기 위해 CXL 동작이 가능한 다수의 자체 개발 호스트 컴퓨터가 CXL 네트워크 스위치를 통해 연결된 다수 CXL 메모리 장치들을 제어하는 환경을 구성했다. 이후 구성된 플랫폼을 통해 CXL 메모리 장치의 성능을 기존 RDMA 기반 메모리 확장 솔루션과 비교했다. 연구팀이 제안한 ‘DirectCXL’은 확장된 메모리에 대한 접근 시간 검증에서 기존 RDMA 기반의 메모리 확장 솔루션 대비 8.3배의 성능 향상을 보였으며, 많은 메모리 접근을 요구하는 그래프 응용처리 및 인 메모리 데이터베이스 응용처리에서도 각각 2.3배, 2배의 성능 향상을 이뤄냈다.

정명수 교수는 "이번에 개발된 ‘DirectCXL’은 기존 RDMA기반 메모리 확장 솔루션보다 훨씬 적은 비용으로도 뛰어난 성능과 높은 확장성을 제공하는 만큼 데이터센터나 고성능 컴퓨팅 시스템에서의 수요가 클 것으로 기대한다ˮ며, "세계 최초로 개발된 CXL 2.0 기반의 단대단 프로토타입 플랫폼을 활용해 CXL이 적용된 새로운 운영체제(OS)는 물론 시스템 소프트웨어, 솔루션 시제품 고도화를 통해 향후 CXL을 활용한 시스템 구축에 초석을 제공할 것이다ˮ라고 말했다.

한편 이번 연구는 미국 칼스배드에서 지난 7월에 11에 열린 시스템 분야 최우수 학술대회인 유즈닉스 연례 회의 `USENIX Annual Technical Conference, 2022'에 ‘DirectCXL’이라는 논문명(Direct Access, High-performance Memory Disaggregation with DirectCXL)으로 발표되었다. 또한 미국 산호세에서 열리는 8월 2/3일에 플래시 메모리 정상회담(Flash Memory Summit)에서 CXL 컨소시움이 이끄는 CXL포럼에 발표될 예정이다.

‘DirectCXL’의 자세한 내용은 연구실 웹사이트(http://camelab.org)에서 확인할 수 있다. DirectCXL은 데이터센터와 클라우드 시스템에서 다양한 응용에 쉽게 적용 가능하며, 하나의 실시예로 메타(페이스북) 추천시스템 기계학습 데이터 가속에 대한 시연 영상을 연구실 유튜브(https://youtu.be/jm8k-JM0qbM) 에서 확인할 수 있다. 해당 영상은 각 개인의 대규모 특성 자료들(텐서)을 CXL 메모리 풀에 올려두고 빅데이터를 활용한 인공지능이 친구나 광고 등 개인 특성에 맞는 자료들을 추천하게 하는 시스템으로 기존 데이터 센터의 원격메모리에 비해 3.2배 이상의 사용자 수준 성능 향상을 보여주고 있다.

2022.08.01 조회수 11280

인공지능 및 빅데이터 시대를 이끌어갈 차세대 CXL2.0 메모리 확장 플랫폼 세계 최초 개발

우리 대학 전기및전자공학부 정명수 교수 연구팀(컴퓨터 아키텍처 및 메모리 시스템 연구실)이 대용량 메모리 장치부터 프로세스를 포함한 컴퓨트 익스프레스 링크(CXL) 2.0 기반의 차세대 메모리 확장 플랫폼 ‘다이렉트CXL(이하 DirectCXL)’을 세계 최초로 프로토타입 제작, 운영체제가 실장된 단대단(End-to-End) 시연에 성공했다고 1일 밝혔다.

오늘날 빅데이터 분석, 그래프 분석, 인메모리 데이터베이스 등 대규모 데이터에 기반한 응용처리가 증가함에 따라, 데이터 센터에서는 이를 더 빠르고 효율적으로 처리하기 위해 시스템의 메모리 확장에 많은 투자를 하고 있다.

그러나 우리가 흔히 알고 있는 메모리 확장 방식인 더블 데이터 대역폭(DDR) 인터페이스를 통한 메모리 확장은 추가할 수 있는 메모리 개수의 제한이 있어, 대규모 데이터 기반의 응용을 처리하기에 충분치 않다. 따라서 데이터 센터에서는 CPU와 메모리로 이루어진 메모리 노드들을 따로 구성하고, 응용을 수행하는 호스트의 메모리가 부족하면 네트워크로 연결된 메모리 노드를 자신의 메모리 공간으로 사용하는 원격 데이터 전송 기술(이하 RDMA) 기반의 메모리 확장을 사용한다.

여러 메모리 노드를 사용하는 RDMA 기반의 메모리 확장을 통해 데이터센터는 시스템의 메모리 크기를 늘릴 수 있었지만, 여전히 해결해야 할 문제들이 남아있었다. 우선 RDMA 기반 메모리 확장 시스템에서는 노드 간 데이터 이동 시 불필요한 데이터 복사, 소프트웨어의 개입 그리고 프로토콜 전환으로 인한 지연을 발생시켜 성능 저하가 발생했다. 또한 시스템의 메모리 확장 시 메모리만을 추가할 수 있는 것이 아닌, 메모리와 메모리를 제어할 CPU가 하나의 메모리 노드를 이루어 시스템에 추가되어야 했기 때문에, 추가적인 비용 소모가 발생했다.

최근 컴퓨트 익스프레스 링크(Compute Express Link, 이하 CXL) 프로토콜의 등장으로 많은 메모리 고객사와 제조사가 이러한 문제를 해결할 가능성을 확인하고 있다. CXL은 PCI 익스프레스(PCIe) 인터페이스 기반의 CPU-장치(Device) 간 연결을 위한 프로토콜로, 이를 기반으로 한 장치 연결은 기존보다 높은 성능과 확장성을 지원하는 것이 특징이다.

국내외 유수 기업들이 모여 CXL 인터페이스 표준 규약을 제안하는 CXL 컨소시엄은 지난 2019년 CXL 1.0/1.1을 처음 제안했고, 이후 CXL 2.0을 발표하며 CXL 1.0/1.1에서 하나의 포트당 하나의 지역 메모리 장치만을 연결할 수 있었던 확장성 문제를 스위치 네트워크를 통해 개선, 하나의 포트를 여러 포트로 확장할 수 있도록 했다. 따라서 CXL 1.0/1.1과 달리 CXL 2.0에서는 확장된 포트에 다수의 원격 CXL 메모리 장치를 연결하는 것이 가능해 더 높은 확장성을 지원할 수 있게 됐다.

그러나 CXL 2.0의 높은 확장성에도 불구하고, 아직 CXL 연구의 방향성을 제시해줄 수 있는 시제품 개발 및 연구들이 진행되지 않아, 메모리 업계와 학계에서는 여전히 CXL1.0/1.1을 기반으로 지역 메모리 확장 장치, 시제품 개발 및 연구를 진행하고 있는 실정이다. 따라서 새로운 CXL 2.0을 통한 메모리 확장 연구의 방향성 초석을 제시할 필요성이 커졌다.

정명수 교수 연구팀이 전 세계 최초로 프로토타입한 CXL 2.0 기반 메모리 확장 플랫폼 ‘DirectCXL’은 높은 수준의 메모리 확장성을 제공하며, 빠른 속도로 대규모 데이터 처리를 가능케 한다. 이를 위해 연구팀은 메모리를 확장해 줄 장치인 ‘CXL 메모리 장치’와 호스트 ‘CXL 프로세서 (CPU)’, 여러 호스트를 다수의 CXL 메모리 장치에 연결해주는 ‘CXL 네트워크 스위치’ 그리고 메모리 확장 플랫폼 전반을 제어할 리눅스 운영체제 기반의‘CXL 소프트웨어 모듈’을 개발해 플랫폼을 구성했다.

구성된 ‘DirectCXL’ 플랫폼을 사용한 시스템에서는 확장된 메모리 공간에 직접 접근해 데이터를 CPU의 캐시로 가져와 불필요한 메모리 복사와 소프트웨어의 개입이 없으며, PCIe 인터페이스만을 사용해 프로토콜 전환을 없애 지연시간을 최대한 줄였다. 또한 추가적인 CPU가 필요 없는 CXL 메모리 장치를 CXL 스위치에 연결하는 것만으로 메모리 확장이 가능해 효율적인 시스템의 구성이 가능했다. 국내외 소수 대기업에서 메모리 장치 일부 단품에 대한 구성을 보여준 준 사례는 있지만, CXL 2.0 기반, CPU부터 CXL 스위치, 메모리 장치가 장착된 시스템에서 운영체제를 동작시키고 데이터 센터와 응용을 실행하고 시연한 것은 정명수 교수 연구팀이 처음이다.

연구팀은 자체 제작한 메모리 확장 플랫폼 ‘DirectCXL’의 성능을 검증하기 위해 CXL 동작이 가능한 다수의 자체 개발 호스트 컴퓨터가 CXL 네트워크 스위치를 통해 연결된 다수 CXL 메모리 장치들을 제어하는 환경을 구성했다. 이후 구성된 플랫폼을 통해 CXL 메모리 장치의 성능을 기존 RDMA 기반 메모리 확장 솔루션과 비교했다. 연구팀이 제안한 ‘DirectCXL’은 확장된 메모리에 대한 접근 시간 검증에서 기존 RDMA 기반의 메모리 확장 솔루션 대비 8.3배의 성능 향상을 보였으며, 많은 메모리 접근을 요구하는 그래프 응용처리 및 인 메모리 데이터베이스 응용처리에서도 각각 2.3배, 2배의 성능 향상을 이뤄냈다.

정명수 교수는 "이번에 개발된 ‘DirectCXL’은 기존 RDMA기반 메모리 확장 솔루션보다 훨씬 적은 비용으로도 뛰어난 성능과 높은 확장성을 제공하는 만큼 데이터센터나 고성능 컴퓨팅 시스템에서의 수요가 클 것으로 기대한다ˮ며, "세계 최초로 개발된 CXL 2.0 기반의 단대단 프로토타입 플랫폼을 활용해 CXL이 적용된 새로운 운영체제(OS)는 물론 시스템 소프트웨어, 솔루션 시제품 고도화를 통해 향후 CXL을 활용한 시스템 구축에 초석을 제공할 것이다ˮ라고 말했다.

한편 이번 연구는 미국 칼스배드에서 지난 7월에 11에 열린 시스템 분야 최우수 학술대회인 유즈닉스 연례 회의 `USENIX Annual Technical Conference, 2022'에 ‘DirectCXL’이라는 논문명(Direct Access, High-performance Memory Disaggregation with DirectCXL)으로 발표되었다. 또한 미국 산호세에서 열리는 8월 2/3일에 플래시 메모리 정상회담(Flash Memory Summit)에서 CXL 컨소시움이 이끄는 CXL포럼에 발표될 예정이다.

‘DirectCXL’의 자세한 내용은 연구실 웹사이트(http://camelab.org)에서 확인할 수 있다. DirectCXL은 데이터센터와 클라우드 시스템에서 다양한 응용에 쉽게 적용 가능하며, 하나의 실시예로 메타(페이스북) 추천시스템 기계학습 데이터 가속에 대한 시연 영상을 연구실 유튜브(https://youtu.be/jm8k-JM0qbM) 에서 확인할 수 있다. 해당 영상은 각 개인의 대규모 특성 자료들(텐서)을 CXL 메모리 풀에 올려두고 빅데이터를 활용한 인공지능이 친구나 광고 등 개인 특성에 맞는 자료들을 추천하게 하는 시스템으로 기존 데이터 센터의 원격메모리에 비해 3.2배 이상의 사용자 수준 성능 향상을 보여주고 있다.

2022.08.01 조회수 11280 -

인간 뇌처럼 뉴런-시냅스 동시 구동 모사한 메모리 최초 구현

우리 대학 신소재공학과 이건재 교수팀이 100 nm(나노미터) 두께의 단일 소자에서 뉴런과 시냅스를 동시에 모사하는 뉴로모픽(neuromorphic) 메모리를 개발했다고 23일 밝혔다. 뉴런은 신경계를 이루는 기본적인 단위세포를, 시냅스는 뉴런 간의 접합 부위를 말한다.

이 교수팀은 인간의 뇌처럼 뉴런과 시냅스가 유기적으로 동작하는 방식의 단일 메모리 소자를 최초로 구현했으며, 이를 통해 반도체 소자로 인간 뇌를 완전히 구현한다는 뉴로모픽 컴퓨팅 본연의 목표 달성에 근접할 수 있을 것으로 기대된다.

1,000억 개의 뉴런과 100조 개의 시냅스의 복잡한 네트워크로 구성된 인간 뇌는 그 기능과 구조가 고정된 것이 아니라 외부 환경에 따라서 유연하게 변하는 특징을 가지고 있다. 따라서 뉴로모픽 소자는 뉴런과 시냅스의 특성을 모사해 기존의 컴퓨터로는 구현할 수 없는 인간 뇌의 고도 인지 기능을 실현하는 데에 가장 큰 목적을 두고 있다.

지금까지 뉴로모픽 컴퓨팅 구현을 위해서 CMOS 집적회로와 비휘발성 메모리 등을 이용한 연구들이 진행됐으나, 기존 기술들은 뉴런과 시냅스의 기능을 분리해 모사한다는 한계점을 가지고 있었다.

인간 뇌에서 뉴런과 시냅스는 서로 유기적으로 연결돼 있으며, 서로 간의 상호작용을 통해 인지 기능이 발현된다. 이러한 뉴런과 시냅스의 기능을 인간 뇌처럼 단일 구조체에서 통합해 구현하는 것은 어려운 도전 과제였다.

이 교수 연구팀은 휘발성의 소자(threshold switch)로 뉴런을, 비휘발성의 상변화 메모리 소자로 시냅스를 모사해 단기·장기 기억이 공존하는 단일 뉴로모픽 소자를 개발했으며, 이를 통해 집적도 개선 및 비용 절감 효과도 얻을 수 있을 것으로 기대된다. 특히 기존 CMOS 뉴런 소자에서는 단순 신호 발산 기능만이 구현됐으나, 연구팀의 뉴런-시냅스 통합소자는 신호 발산 유형이 환경에 따라서 유연하게 적응하는 가소성(plasticity)을 구현하는 데 성공했다.

이건재 교수는 이번 연구 성과에 대해 "인간은 뉴런과 시냅스의 상호작용을 통해 기억, 학습, 인지 기능을 발현하므로 둘 모두를 통합 모사하는 것이 인공지능에 있어서 필수적인 요소ˮ라며 "개발한 단일 뉴런-시냅스 소자는 기존의 단순 이미지 학습 효과를 넘어서, 피드백 효과를 기반으로 한 번 배운 내용을 더 빨리 학습하는 재학습(retraining) 효과 구현도 성공해 인공지능뿐만 아니라 뇌를 역설계하는 연구에도 큰 도움이 될 것이다”고 언급했다.

한편 이번 연구는 삼성전자 전략산학과제와 지능형반도체 사업의 지원을 받아 수행됐으며, 국제 학술지 `네이쳐 커뮤니케이션즈(Nature Communications)'에 5월 19일 字 게재됐다.

2022.06.23 조회수 10883

인간 뇌처럼 뉴런-시냅스 동시 구동 모사한 메모리 최초 구현

우리 대학 신소재공학과 이건재 교수팀이 100 nm(나노미터) 두께의 단일 소자에서 뉴런과 시냅스를 동시에 모사하는 뉴로모픽(neuromorphic) 메모리를 개발했다고 23일 밝혔다. 뉴런은 신경계를 이루는 기본적인 단위세포를, 시냅스는 뉴런 간의 접합 부위를 말한다.

이 교수팀은 인간의 뇌처럼 뉴런과 시냅스가 유기적으로 동작하는 방식의 단일 메모리 소자를 최초로 구현했으며, 이를 통해 반도체 소자로 인간 뇌를 완전히 구현한다는 뉴로모픽 컴퓨팅 본연의 목표 달성에 근접할 수 있을 것으로 기대된다.

1,000억 개의 뉴런과 100조 개의 시냅스의 복잡한 네트워크로 구성된 인간 뇌는 그 기능과 구조가 고정된 것이 아니라 외부 환경에 따라서 유연하게 변하는 특징을 가지고 있다. 따라서 뉴로모픽 소자는 뉴런과 시냅스의 특성을 모사해 기존의 컴퓨터로는 구현할 수 없는 인간 뇌의 고도 인지 기능을 실현하는 데에 가장 큰 목적을 두고 있다.

지금까지 뉴로모픽 컴퓨팅 구현을 위해서 CMOS 집적회로와 비휘발성 메모리 등을 이용한 연구들이 진행됐으나, 기존 기술들은 뉴런과 시냅스의 기능을 분리해 모사한다는 한계점을 가지고 있었다.

인간 뇌에서 뉴런과 시냅스는 서로 유기적으로 연결돼 있으며, 서로 간의 상호작용을 통해 인지 기능이 발현된다. 이러한 뉴런과 시냅스의 기능을 인간 뇌처럼 단일 구조체에서 통합해 구현하는 것은 어려운 도전 과제였다.

이 교수 연구팀은 휘발성의 소자(threshold switch)로 뉴런을, 비휘발성의 상변화 메모리 소자로 시냅스를 모사해 단기·장기 기억이 공존하는 단일 뉴로모픽 소자를 개발했으며, 이를 통해 집적도 개선 및 비용 절감 효과도 얻을 수 있을 것으로 기대된다. 특히 기존 CMOS 뉴런 소자에서는 단순 신호 발산 기능만이 구현됐으나, 연구팀의 뉴런-시냅스 통합소자는 신호 발산 유형이 환경에 따라서 유연하게 적응하는 가소성(plasticity)을 구현하는 데 성공했다.

이건재 교수는 이번 연구 성과에 대해 "인간은 뉴런과 시냅스의 상호작용을 통해 기억, 학습, 인지 기능을 발현하므로 둘 모두를 통합 모사하는 것이 인공지능에 있어서 필수적인 요소ˮ라며 "개발한 단일 뉴런-시냅스 소자는 기존의 단순 이미지 학습 효과를 넘어서, 피드백 효과를 기반으로 한 번 배운 내용을 더 빨리 학습하는 재학습(retraining) 효과 구현도 성공해 인공지능뿐만 아니라 뇌를 역설계하는 연구에도 큰 도움이 될 것이다”고 언급했다.

한편 이번 연구는 삼성전자 전략산학과제와 지능형반도체 사업의 지원을 받아 수행됐으며, 국제 학술지 `네이쳐 커뮤니케이션즈(Nature Communications)'에 5월 19일 字 게재됐다.

2022.06.23 조회수 10883