%EC%A0%9C1%EC%9B%90%EB%A6%AC

-

그래핀 기반 2차원 반도체 소자 시뮬레이션의 양자 도약 달성

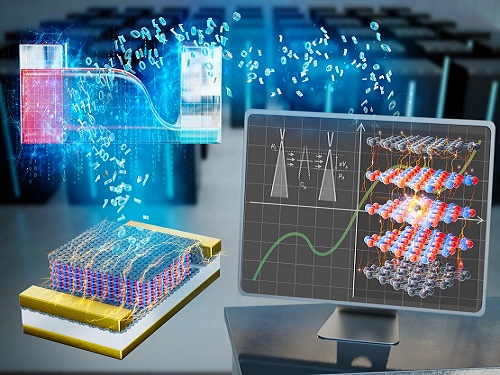

반도체 연구 개발에서 소자의 미세화에 따라 원자 수준에서 전류의 흐름을 이해하고 제어하는 것이 핵심적 요소가 되고 있는 상황에서, 우리 연구진이 기존에는 불가능했던 원자만큼 얇은 2차원 반도체 소자의 엄밀한 양자 역학적 컴퓨터 시뮬레이션을 성공적으로 구현하고 이를 기반으로 원자 결함에 의해 발생하는 특이한 소자 특성을 세계 최초로 보고했다.

우리 대학 전기및전자공학부 김용훈 교수 연구팀이 자체적으로 개발한 양자 수송 이론을 통해 세계 최초로 그래핀 전극 간 전자의 터널링 현상(전자가 포텐셜 장벽을 투과하는 현상)으로 작동하는 *2차원 터널링 트랜지스터의 **제1 원리 시뮬레이션을 수행하는 데 성공했다고 4일 밝혔다.

* 2차원 터널링 트랜지스터: 그래핀을 전극으로 하여 전극 간 전자의 터널링(tunneling) 현상을 통해 소자가 작동하는 반도체 소자이다. 소자의 동작 특성을 결정하는 그래핀 전극간 전자의 터널링 현상은 소스-드레인(source-drain) 전극 및 게이트(gate) 전압에 의해 결정된다.

**제1 원리 시뮬레이션: 제1원리 계산은 물질 내 전자들의 거동을 해석할 때 실험적 데이터나 경험적 모델을 도입하지 않고 지배방정식인 슈뢰딩거 방정식을 원자 정보를 포함시켜 직접 푸는 양자역학적 물질 시뮬레이션 방법으로 대표적인 방법론은 밀도 범함수론(density functional theory, DFT)이 있음

전기및전자공학부 김태형 박사과정과 이주호 박사가 공동 제1 저자로 참여한 이번 연구는 소재 계산 분야의 권위 있는 학술지 `네이쳐 파트너 저널 컴퓨테이셔널 머터리얼즈(Npj Computational Materials)' (IF 13.20) 3월 25일 字 온라인판에 게재됐다. (논문명: Gate-versus defect-induced voltage drop and negative differential resistance in vertical graphene heterostructures)

제1 원리 시뮬레이션이란 슈퍼컴퓨터에서 원자 수준의 양자역학 계산을 수행해 실험적 데이터나 경험적 모델의 도움 없이 물질의 특성을 도출하는 방법으로 제1 원리 계산을 통한 평형 상태의 소재 연구는 1998년 월터 콘(Walter Khon) 교수가 노벨상을 받은 `밀도 범함수론(density functional theory: DFT)'을 기반으로 다방면으로 수행돼왔다.

반면 전압 인가에 따른 비평형 상태에서 작동하는 나노 소자의 제1 원리 계산은 DFT 이론을 적용하기 어렵고 그 대안으로 제시된 이론들에도 한계가 있어 현재 그래핀 기반 2차원 반도체 소자의 엄밀한 양자역학적 시뮬레이션은 불가능한 상황이었다.

연구팀은 먼저 이러한 어려움을 극복하기 위해 자체적으로 수립한 새로운 양자 수송 계산 체계인 다공간 DFT 이론을 발전시켜 그래핀 기반 2차원 터널링 트랜지스터의 제1 원리 시뮬레이션을 가능하게 했다.

다음으로 이를 그래핀 전극-육각형 질화붕소 채널-그래핀 전극 소자 구조에 적용해 질화붕소 층에 존재하는 원자 결함이 다양한 비선형 소자 특성들을 도출시킬 수 있음을 보여 원자 결함의 종류와 위치에 대한 정보가 신뢰성 있는 2차원 소자의 구현에 매우 중요함 요소을 입증했다.

한편 이러한 비선형 소자 특성은 연구진이 기존에 세계 최초로 제안했던 양자 혼성화(quantum hybridization) 소자 원리(device principle)에 따라 발현됨을 보여 2차원 소자의 양자적 특성을 활용하는 한 방향을 제시했다.

김 교수는 "나날이 치열해지는 반도체 연구/개발 분야에서 세계적으로 경쟁력 있는 나노 소자 전산 설계 원천기술을 확보했다ˮ고 연구의 의미를 소개하며 "양자 효과가 극대화될 수밖에 없는 차세대 반도체 연구/개발에서 양자역학적 제1 원리 컴퓨터 시뮬레이션의 역할이 더욱 중요해질 것”이라고 강조했다.

한편 이번 연구는 삼성전자 미래기술 육성센터의 지원을 받아 수행됐다.

2022.04.04 조회수 14541

그래핀 기반 2차원 반도체 소자 시뮬레이션의 양자 도약 달성

반도체 연구 개발에서 소자의 미세화에 따라 원자 수준에서 전류의 흐름을 이해하고 제어하는 것이 핵심적 요소가 되고 있는 상황에서, 우리 연구진이 기존에는 불가능했던 원자만큼 얇은 2차원 반도체 소자의 엄밀한 양자 역학적 컴퓨터 시뮬레이션을 성공적으로 구현하고 이를 기반으로 원자 결함에 의해 발생하는 특이한 소자 특성을 세계 최초로 보고했다.

우리 대학 전기및전자공학부 김용훈 교수 연구팀이 자체적으로 개발한 양자 수송 이론을 통해 세계 최초로 그래핀 전극 간 전자의 터널링 현상(전자가 포텐셜 장벽을 투과하는 현상)으로 작동하는 *2차원 터널링 트랜지스터의 **제1 원리 시뮬레이션을 수행하는 데 성공했다고 4일 밝혔다.

* 2차원 터널링 트랜지스터: 그래핀을 전극으로 하여 전극 간 전자의 터널링(tunneling) 현상을 통해 소자가 작동하는 반도체 소자이다. 소자의 동작 특성을 결정하는 그래핀 전극간 전자의 터널링 현상은 소스-드레인(source-drain) 전극 및 게이트(gate) 전압에 의해 결정된다.

**제1 원리 시뮬레이션: 제1원리 계산은 물질 내 전자들의 거동을 해석할 때 실험적 데이터나 경험적 모델을 도입하지 않고 지배방정식인 슈뢰딩거 방정식을 원자 정보를 포함시켜 직접 푸는 양자역학적 물질 시뮬레이션 방법으로 대표적인 방법론은 밀도 범함수론(density functional theory, DFT)이 있음

전기및전자공학부 김태형 박사과정과 이주호 박사가 공동 제1 저자로 참여한 이번 연구는 소재 계산 분야의 권위 있는 학술지 `네이쳐 파트너 저널 컴퓨테이셔널 머터리얼즈(Npj Computational Materials)' (IF 13.20) 3월 25일 字 온라인판에 게재됐다. (논문명: Gate-versus defect-induced voltage drop and negative differential resistance in vertical graphene heterostructures)

제1 원리 시뮬레이션이란 슈퍼컴퓨터에서 원자 수준의 양자역학 계산을 수행해 실험적 데이터나 경험적 모델의 도움 없이 물질의 특성을 도출하는 방법으로 제1 원리 계산을 통한 평형 상태의 소재 연구는 1998년 월터 콘(Walter Khon) 교수가 노벨상을 받은 `밀도 범함수론(density functional theory: DFT)'을 기반으로 다방면으로 수행돼왔다.

반면 전압 인가에 따른 비평형 상태에서 작동하는 나노 소자의 제1 원리 계산은 DFT 이론을 적용하기 어렵고 그 대안으로 제시된 이론들에도 한계가 있어 현재 그래핀 기반 2차원 반도체 소자의 엄밀한 양자역학적 시뮬레이션은 불가능한 상황이었다.

연구팀은 먼저 이러한 어려움을 극복하기 위해 자체적으로 수립한 새로운 양자 수송 계산 체계인 다공간 DFT 이론을 발전시켜 그래핀 기반 2차원 터널링 트랜지스터의 제1 원리 시뮬레이션을 가능하게 했다.

다음으로 이를 그래핀 전극-육각형 질화붕소 채널-그래핀 전극 소자 구조에 적용해 질화붕소 층에 존재하는 원자 결함이 다양한 비선형 소자 특성들을 도출시킬 수 있음을 보여 원자 결함의 종류와 위치에 대한 정보가 신뢰성 있는 2차원 소자의 구현에 매우 중요함 요소을 입증했다.

한편 이러한 비선형 소자 특성은 연구진이 기존에 세계 최초로 제안했던 양자 혼성화(quantum hybridization) 소자 원리(device principle)에 따라 발현됨을 보여 2차원 소자의 양자적 특성을 활용하는 한 방향을 제시했다.

김 교수는 "나날이 치열해지는 반도체 연구/개발 분야에서 세계적으로 경쟁력 있는 나노 소자 전산 설계 원천기술을 확보했다ˮ고 연구의 의미를 소개하며 "양자 효과가 극대화될 수밖에 없는 차세대 반도체 연구/개발에서 양자역학적 제1 원리 컴퓨터 시뮬레이션의 역할이 더욱 중요해질 것”이라고 강조했다.

한편 이번 연구는 삼성전자 미래기술 육성센터의 지원을 받아 수행됐다.

2022.04.04 조회수 14541 -

70년 만에 준-페르미 준위 분리 현상 제1 원리적으로 규명

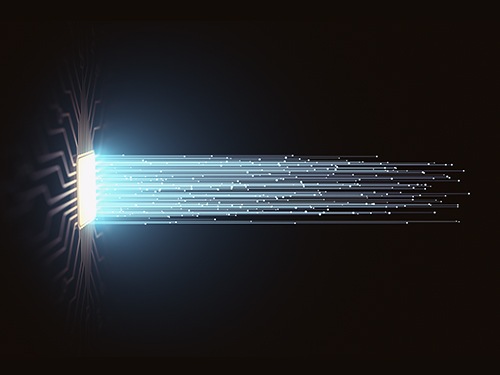

국내 연구진이 70년 난제로 꼽히던 준-페르미 준위 분리 현상의 원자 수준 규명에 성공했다.

우리 대학 전기및전자공학부 김용훈 교수 연구팀이 반도체 소자 동작의 기원인 준-페르미 준위(quasi-Fermi level) 분리 현상을 제1 원리적으로 기술하는 데 최초로 성공했다고 27일 밝혔다.

제1 원리적인 방법이란 실험적 데이터나 경험적 모델을 사용하지 않고 슈뢰딩거 방정식을 직접 푸는 양자역학적 물질 시뮬레이션 방법이다.

김용훈 교수 연구팀의 연구 결과는 특히 비평형 상태의 나노 소자 내에서 발생하는 복잡한 전압 강하의 기원을 새로운 이론 체계와 슈퍼컴퓨터를 통해 규명함으로써, 다양한 첨단 반도체 소자의 분석 및 차세대 나노 소자 개발을 위한 이론적 틀을 제공할 것으로 기대되고 있다.

이주호 박사과정 학생이 제1 저자로 참여한 이번 연구 성과는 국제학술지 미국‘국립과학원회보(Proceedings of the National Academy of Sciences)’ 4월 23일 字 온라인판에 게재됐다. (논문명: Quasi-Fermi level splitting in nanoscale junctions from ab initio)

반도체 관련 교과서에도 소개되고 있는 준-페르미 준위 개념은 반도체 소자 내 전압인가 상황을 기술하는 표준적인 이론 도구로서 그동안 트랜지스터, 태양전지, 발광다이오드(LED) 등 다양한 반도체 소자들의 구동 원리를 이해하거나 성능을 결정하는데 경험적으로 사용돼왔다.

하지만 준-페르미 준위 분포 현상은 1956년 노벨 물리학상 수상자 윌리엄 쇼클리(William B. Shockley)가 제시한 지 70년이 지난 현재에도 전압 인가 상황의 반도체 소자 채널 내에서 측정을 하거나 계산을 해야 하는 어려움 때문에 원자 수준에서는 이해되지 못한 상황이 계속돼왔다.

연구팀은 차세대 반도체 소자의 후보군으로 주목을 받는 단일분자 소자에서, 나노미터 길이에서 발생하는 복잡한 전압 강하 현상을 최초로 규명해냈다. 특히 전도성이 강한 특정 나노 전자소자에 대해 비 선형적 전압 강하 현상이 일어나는 원인이 준-페르미 준위 분리 현상임을 밝혔다.

이러한 연구 성과는 김 교수 연구팀이 다년간에 걸쳐 새로운 반도체 소자 제1 원리 계산 이론을 확립하고 이를 소프트웨어적으로 구현했기에 가능했다. 이는 외산 소프트웨어에만 의존하던 반도체 설계 분야에서 세계적으로 경쟁력 있는 차세대 나노소자 전산 설계 원천기술을 확보했다는 점에서 큰 의미를 부여할 수 있다.

한편 이번 연구는 과학기술정보통신부 중견연구자지원사업, 나노소재원천기술개발사업, 기초연구실지원사업, 글로벌프론티어사업의 지원을 받아 수행됐다.

2020.04.27 조회수 18218

70년 만에 준-페르미 준위 분리 현상 제1 원리적으로 규명

국내 연구진이 70년 난제로 꼽히던 준-페르미 준위 분리 현상의 원자 수준 규명에 성공했다.

우리 대학 전기및전자공학부 김용훈 교수 연구팀이 반도체 소자 동작의 기원인 준-페르미 준위(quasi-Fermi level) 분리 현상을 제1 원리적으로 기술하는 데 최초로 성공했다고 27일 밝혔다.

제1 원리적인 방법이란 실험적 데이터나 경험적 모델을 사용하지 않고 슈뢰딩거 방정식을 직접 푸는 양자역학적 물질 시뮬레이션 방법이다.

김용훈 교수 연구팀의 연구 결과는 특히 비평형 상태의 나노 소자 내에서 발생하는 복잡한 전압 강하의 기원을 새로운 이론 체계와 슈퍼컴퓨터를 통해 규명함으로써, 다양한 첨단 반도체 소자의 분석 및 차세대 나노 소자 개발을 위한 이론적 틀을 제공할 것으로 기대되고 있다.

이주호 박사과정 학생이 제1 저자로 참여한 이번 연구 성과는 국제학술지 미국‘국립과학원회보(Proceedings of the National Academy of Sciences)’ 4월 23일 字 온라인판에 게재됐다. (논문명: Quasi-Fermi level splitting in nanoscale junctions from ab initio)

반도체 관련 교과서에도 소개되고 있는 준-페르미 준위 개념은 반도체 소자 내 전압인가 상황을 기술하는 표준적인 이론 도구로서 그동안 트랜지스터, 태양전지, 발광다이오드(LED) 등 다양한 반도체 소자들의 구동 원리를 이해하거나 성능을 결정하는데 경험적으로 사용돼왔다.

하지만 준-페르미 준위 분포 현상은 1956년 노벨 물리학상 수상자 윌리엄 쇼클리(William B. Shockley)가 제시한 지 70년이 지난 현재에도 전압 인가 상황의 반도체 소자 채널 내에서 측정을 하거나 계산을 해야 하는 어려움 때문에 원자 수준에서는 이해되지 못한 상황이 계속돼왔다.

연구팀은 차세대 반도체 소자의 후보군으로 주목을 받는 단일분자 소자에서, 나노미터 길이에서 발생하는 복잡한 전압 강하 현상을 최초로 규명해냈다. 특히 전도성이 강한 특정 나노 전자소자에 대해 비 선형적 전압 강하 현상이 일어나는 원인이 준-페르미 준위 분리 현상임을 밝혔다.

이러한 연구 성과는 김 교수 연구팀이 다년간에 걸쳐 새로운 반도체 소자 제1 원리 계산 이론을 확립하고 이를 소프트웨어적으로 구현했기에 가능했다. 이는 외산 소프트웨어에만 의존하던 반도체 설계 분야에서 세계적으로 경쟁력 있는 차세대 나노소자 전산 설계 원천기술을 확보했다는 점에서 큰 의미를 부여할 수 있다.

한편 이번 연구는 과학기술정보통신부 중견연구자지원사업, 나노소재원천기술개발사업, 기초연구실지원사업, 글로벌프론티어사업의 지원을 받아 수행됐다.

2020.04.27 조회수 18218