-

KAIST, 인공지능 반도체 생태계를 선도하다

인공지능 반도체(이하 AI 반도체)가 국가적인 전략기술로 두드러지면서 KAIST의 관련 성과도 주목받고 있다. 과학기술정보통신부는 지난해 2030년 세계 AI 반도체 시장 20% 점유를 목표로 인공지능 반도체 지원사업에 본격적으로 착수한 바 있다. 올해에는 산학연 논의를 거쳐 5년간 1조 200억 원을 투입하는 `인공지능 반도체 산업 성장 지원대책'으로 지원을 확대했다. 이에 따라 AI 반도체 전문가 양성을 위해 주요 대학들의 행보도 분주해졌다.

KAIST는 반도체와 인공지능 양대 핵심 분야에서 최상급의 교육, 연구 역량을 쌓아 왔다. 반도체 분야에서는 지난 17년 동안 메사추세츠 공과대학(이하 MIT), 스탠퍼드(Stanford)와 같은 세계적인 학교를 제치고 국제반도체회로학회(이하 ISSCC, International Solid State Circuit Conference)에서 대학 중 1위를 지켜 왔다는 점이 돋보인다. ISSCC는 1954년 설립된 반도체 집적회로 설계 분야 세계 최고 권위 학회다. 참가자 중 60% 이상이 삼성, 퀄컴, TSMC, 인텔을 비롯한 산업계 소속일만큼 산업적인 실용성을 중시해서 `반도체 설계 올림픽'이라는 별명도 있다.

KAIST는 ISSCC에서 채택 논문 수 기준 매년 전 세계 대학교 중 1~2위를 유지했다. 최근 17년간 평균 채택 논문 수를 살펴보면 압도적인 선두다. 해당 기간 채택된 KAIST의 논문은 평균 8.4편으로, 경쟁자인 MIT(4.6편)와 캘리포니아대학교 로스앤젤레스(UCLA)(3.6편)에 비해 두 배 가까운 성과다. 국내에서는 반도체 설계 분야 부동의 1위인 삼성에 이어 종합 2위 자리를 유지하고 있다. 그럴 뿐만 아니라 ISSCC와 쌍벽을 이루는 집적회로 분야 학술대회인 초고밀도집적회로학회에서도 KAIST는 2022년 전 세계 대학 중 1위를 기록했다.

KAIST의 연구진들이 반도체 산업 핵심 분야 전반에서 신기술을 발표해 연구의 질적인 수준도 높다. 전기및전자공학부 정명수 교수 연구팀은 고성능 저전력을 추구하는 현재 업계의 수요에 대응해 전력 공급 없이도 동작을 유지하는 컴퓨터를 개발했다. 소재 분야에서는 신소재공학과의 박병국 교수 연구팀이 기존의 메모리에 비해 동작 속도가 10배 이상 빠른 `스핀궤도토크 자성메모리' 소자를 개발해서 기존 `폰노이만 구조'의 한계를 극복하는 방안을 제시하기도 했다.

이처럼 현재 반도체 산업의 주요 과제에 솔루션을 제공하는 한편으로 미래의 새로운 반도체 분야를 선점하는 데 필요한 신기술 개발도 활발하다. 암호 및 비선형 연산 분야에서 차세대 컴퓨팅으로 주목받는 양자컴퓨팅 분야에서는 전기및전자공학부 김상현 교수 연구팀이 3차원 집적 기술을 세계 최초로 선보였다. 신경계의 원리를 활용해 인공지능 분야에서 발군의 성능을 보일 것으로 기대되는 뉴로모픽 컴퓨팅에서는 전기및전자공학부 최신현 교수 연구팀이 신경세포를 모사하는 차세대 멤리스터를 개발 중이다.

인공지능 분야에서도 비약적으로 성장했다. 인공지능 분야의 양대 세계 최고 권위 학회인 국제머신러닝학회(ICML)과 인공신경망학회(NeurIPS) 논문 수 기준으로 KAIST는 2020년 세계 6위, 아시아에서는 1위를 기록했다. KAIST의 순위는 2012년부터 꾸준히 우상향 그래프를 그려 8년만에 37위에서 6위로, 무려 31계단이나 도약했다. 2021년에는 인공지능 분야 톱 학회 11개에 발표된 한국 논문 중 약 40%에 달하는 129편이 KAIST에서 나왔다. KAIST의 이러한 활약에 힘입어 2021년 한국은 글로벌 인공지능 톱 학회 등재 논문 수 기준으로 미국, 중국, 영국, 캐나다, 독일에 이어 6위에 올랐다.

내용 면에서도 KAIST의 인공지능 연구는 최전선에 있다. 전기및전자공학부 유회준 교수 연구팀은 모바일기기에서 인공지능 실시간 학습을 구현해 에지 네트워크의 단점을 보완했다. 인공지능을 구현하려면 데이터 축적관 막대한 양의 연산이 필요한데, 이를 위해 고성능 서버가 방대한 연산을 담당하고 사용자 단말은 데이터 수집과 간단한 연산만 하는 `에지 네트워크'가 사용된다. 유 교수의 연구는 사용자 단말에 학습 능력을 부여함으로써 인공지능의 처리 속도와 성능을 크게 높일 수 있다.

지난 6월에는 전산학부 김민수 교수 연구팀이 초대규모 인공지능 모델 처리에 꼭 필요한 솔루션을 제시했다. 연구팀이 개발한 초대규모 기계학습 시스템은 현재 업계에서 주로 사용되는 구글의 텐서플로우(Tensorflow)나 IBM의 시스템DS 대비 최대 8.8배나 빠른 속도를 달성할 수 있을 것으로 기대된다.

KAIST는 반도체와 인공지능이 결합된 AI 반도체 분야에서도 주목할만한 성과를 내고 있다. 2020년 전기및전자공학부 유민수 교수 연구팀은 세계 최초로 추천시스템에 최적화된 AI 반도체를 개발하는 데 성공했다. 인공지능 추천시스템은 방대한 콘텐츠와 사용자 정보를 다룬다는 특성상 범용 인공지능 시스템으로 운영하면 병목현상으로 성능에 한계가 있다. 유민수 교수팀은 `프로세싱-인-메모리(이하 PIM, Processing-In-Memory)' 기술을 기반으로 기존 시스템 대비 최대 21배 빠른 속도를 낼 수 있는 반도체를 개발했다. PIM은 처리할 데이터를 임시로 저장하기만 하던 `램'에서 연산까지 수행해 효율을 높이는 기술이다. PIM 기술이 본격적으로 상용화되면 메모리 분야에서 강세인 한국 기업의 AI 반도체 시장 경쟁력이 비약적으로 높아질 것으로 기대된다.

KAIST는 그간의 성과에 안주하지 않고 인공지능 및 반도체, 그리고 AI 반도체 분야 초격차를 유지하고자 다각적인 노력을 기울이고 있다. 1990년 국내 최초로 인공지능연구센터를 설립한 데 이어 2019년에는 김재철AI대학원을 개설해 전문인력을 양성 중이다. 2020년에는 인공지능과 반도체 연구를 융합해 ITRC 인공지능반도체시스템 연구센터가 출범했으며, 2021년에는 인공지능을 다양한 분야에 접목하는 `AI+X' 연구를 활성화하고자 김재철AI대학원과 별도로 AI 연구원을 설립했다.

KAIST는 이러한 노력으로 축적된 내적 역량을 바탕으로 네이버 등 기업과 공동연구센터를 설립하는 한편, 화성시와 같은 지자체와 협력해 동시다발적인 전문인력 양성에 나섰다. 지난 2021년에는 삼성전자와 함께 반도체시스템공학과 설립 협약을 체결하고 새로운 반도체 전문인력 교육과정을 준비하고 있다. 새로 설립되는 반도체시스템공학과는 2023년부터 매년 100명 내외의 신입생을 선발하고, 이들이 전문역량을 꽃피울 수 있도록 학생 전원에게 특별장학금을 지급할 예정이다. 또한 산업계와의 긴밀한 협력을 통해 삼성전자 견학과 인턴십, 공동 워크숍을 지원해 현장에 밀착한 교육을 제공할 예정이다.

KAIST는 국내 반도체 분야 박사 인력의 25%, 박사 출신 중견 및 벤처기업 CEO의 20%를 배출하며 한국 반도체 산업 생태계가 성장하는 데 중대한 공헌을 했다. 본격적으로 열린 AI 반도체 경쟁 체제를 앞두고 KAIST가 다시 산업 생태계의 구심점 역할을 할지 귀추가 주목된다.

KAIST, 인공지능 반도체 생태계를 선도하다

인공지능 반도체(이하 AI 반도체)가 국가적인 전략기술로 두드러지면서 KAIST의 관련 성과도 주목받고 있다. 과학기술정보통신부는 지난해 2030년 세계 AI 반도체 시장 20% 점유를 목표로 인공지능 반도체 지원사업에 본격적으로 착수한 바 있다. 올해에는 산학연 논의를 거쳐 5년간 1조 200억 원을 투입하는 `인공지능 반도체 산업 성장 지원대책'으로 지원을 확대했다. 이에 따라 AI 반도체 전문가 양성을 위해 주요 대학들의 행보도 분주해졌다.

KAIST는 반도체와 인공지능 양대 핵심 분야에서 최상급의 교육, 연구 역량을 쌓아 왔다. 반도체 분야에서는 지난 17년 동안 메사추세츠 공과대학(이하 MIT), 스탠퍼드(Stanford)와 같은 세계적인 학교를 제치고 국제반도체회로학회(이하 ISSCC, International Solid State Circuit Conference)에서 대학 중 1위를 지켜 왔다는 점이 돋보인다. ISSCC는 1954년 설립된 반도체 집적회로 설계 분야 세계 최고 권위 학회다. 참가자 중 60% 이상이 삼성, 퀄컴, TSMC, 인텔을 비롯한 산업계 소속일만큼 산업적인 실용성을 중시해서 `반도체 설계 올림픽'이라는 별명도 있다.

KAIST는 ISSCC에서 채택 논문 수 기준 매년 전 세계 대학교 중 1~2위를 유지했다. 최근 17년간 평균 채택 논문 수를 살펴보면 압도적인 선두다. 해당 기간 채택된 KAIST의 논문은 평균 8.4편으로, 경쟁자인 MIT(4.6편)와 캘리포니아대학교 로스앤젤레스(UCLA)(3.6편)에 비해 두 배 가까운 성과다. 국내에서는 반도체 설계 분야 부동의 1위인 삼성에 이어 종합 2위 자리를 유지하고 있다. 그럴 뿐만 아니라 ISSCC와 쌍벽을 이루는 집적회로 분야 학술대회인 초고밀도집적회로학회에서도 KAIST는 2022년 전 세계 대학 중 1위를 기록했다.

KAIST의 연구진들이 반도체 산업 핵심 분야 전반에서 신기술을 발표해 연구의 질적인 수준도 높다. 전기및전자공학부 정명수 교수 연구팀은 고성능 저전력을 추구하는 현재 업계의 수요에 대응해 전력 공급 없이도 동작을 유지하는 컴퓨터를 개발했다. 소재 분야에서는 신소재공학과의 박병국 교수 연구팀이 기존의 메모리에 비해 동작 속도가 10배 이상 빠른 `스핀궤도토크 자성메모리' 소자를 개발해서 기존 `폰노이만 구조'의 한계를 극복하는 방안을 제시하기도 했다.

이처럼 현재 반도체 산업의 주요 과제에 솔루션을 제공하는 한편으로 미래의 새로운 반도체 분야를 선점하는 데 필요한 신기술 개발도 활발하다. 암호 및 비선형 연산 분야에서 차세대 컴퓨팅으로 주목받는 양자컴퓨팅 분야에서는 전기및전자공학부 김상현 교수 연구팀이 3차원 집적 기술을 세계 최초로 선보였다. 신경계의 원리를 활용해 인공지능 분야에서 발군의 성능을 보일 것으로 기대되는 뉴로모픽 컴퓨팅에서는 전기및전자공학부 최신현 교수 연구팀이 신경세포를 모사하는 차세대 멤리스터를 개발 중이다.

인공지능 분야에서도 비약적으로 성장했다. 인공지능 분야의 양대 세계 최고 권위 학회인 국제머신러닝학회(ICML)과 인공신경망학회(NeurIPS) 논문 수 기준으로 KAIST는 2020년 세계 6위, 아시아에서는 1위를 기록했다. KAIST의 순위는 2012년부터 꾸준히 우상향 그래프를 그려 8년만에 37위에서 6위로, 무려 31계단이나 도약했다. 2021년에는 인공지능 분야 톱 학회 11개에 발표된 한국 논문 중 약 40%에 달하는 129편이 KAIST에서 나왔다. KAIST의 이러한 활약에 힘입어 2021년 한국은 글로벌 인공지능 톱 학회 등재 논문 수 기준으로 미국, 중국, 영국, 캐나다, 독일에 이어 6위에 올랐다.

내용 면에서도 KAIST의 인공지능 연구는 최전선에 있다. 전기및전자공학부 유회준 교수 연구팀은 모바일기기에서 인공지능 실시간 학습을 구현해 에지 네트워크의 단점을 보완했다. 인공지능을 구현하려면 데이터 축적관 막대한 양의 연산이 필요한데, 이를 위해 고성능 서버가 방대한 연산을 담당하고 사용자 단말은 데이터 수집과 간단한 연산만 하는 `에지 네트워크'가 사용된다. 유 교수의 연구는 사용자 단말에 학습 능력을 부여함으로써 인공지능의 처리 속도와 성능을 크게 높일 수 있다.

지난 6월에는 전산학부 김민수 교수 연구팀이 초대규모 인공지능 모델 처리에 꼭 필요한 솔루션을 제시했다. 연구팀이 개발한 초대규모 기계학습 시스템은 현재 업계에서 주로 사용되는 구글의 텐서플로우(Tensorflow)나 IBM의 시스템DS 대비 최대 8.8배나 빠른 속도를 달성할 수 있을 것으로 기대된다.

KAIST는 반도체와 인공지능이 결합된 AI 반도체 분야에서도 주목할만한 성과를 내고 있다. 2020년 전기및전자공학부 유민수 교수 연구팀은 세계 최초로 추천시스템에 최적화된 AI 반도체를 개발하는 데 성공했다. 인공지능 추천시스템은 방대한 콘텐츠와 사용자 정보를 다룬다는 특성상 범용 인공지능 시스템으로 운영하면 병목현상으로 성능에 한계가 있다. 유민수 교수팀은 `프로세싱-인-메모리(이하 PIM, Processing-In-Memory)' 기술을 기반으로 기존 시스템 대비 최대 21배 빠른 속도를 낼 수 있는 반도체를 개발했다. PIM은 처리할 데이터를 임시로 저장하기만 하던 `램'에서 연산까지 수행해 효율을 높이는 기술이다. PIM 기술이 본격적으로 상용화되면 메모리 분야에서 강세인 한국 기업의 AI 반도체 시장 경쟁력이 비약적으로 높아질 것으로 기대된다.

KAIST는 그간의 성과에 안주하지 않고 인공지능 및 반도체, 그리고 AI 반도체 분야 초격차를 유지하고자 다각적인 노력을 기울이고 있다. 1990년 국내 최초로 인공지능연구센터를 설립한 데 이어 2019년에는 김재철AI대학원을 개설해 전문인력을 양성 중이다. 2020년에는 인공지능과 반도체 연구를 융합해 ITRC 인공지능반도체시스템 연구센터가 출범했으며, 2021년에는 인공지능을 다양한 분야에 접목하는 `AI+X' 연구를 활성화하고자 김재철AI대학원과 별도로 AI 연구원을 설립했다.

KAIST는 이러한 노력으로 축적된 내적 역량을 바탕으로 네이버 등 기업과 공동연구센터를 설립하는 한편, 화성시와 같은 지자체와 협력해 동시다발적인 전문인력 양성에 나섰다. 지난 2021년에는 삼성전자와 함께 반도체시스템공학과 설립 협약을 체결하고 새로운 반도체 전문인력 교육과정을 준비하고 있다. 새로 설립되는 반도체시스템공학과는 2023년부터 매년 100명 내외의 신입생을 선발하고, 이들이 전문역량을 꽃피울 수 있도록 학생 전원에게 특별장학금을 지급할 예정이다. 또한 산업계와의 긴밀한 협력을 통해 삼성전자 견학과 인턴십, 공동 워크숍을 지원해 현장에 밀착한 교육을 제공할 예정이다.

KAIST는 국내 반도체 분야 박사 인력의 25%, 박사 출신 중견 및 벤처기업 CEO의 20%를 배출하며 한국 반도체 산업 생태계가 성장하는 데 중대한 공헌을 했다. 본격적으로 열린 AI 반도체 경쟁 체제를 앞두고 KAIST가 다시 산업 생태계의 구심점 역할을 할지 귀추가 주목된다.

2022.08.04

조회수 18972

-

무한대 화소 수준의 초고해상도 AR/VR 디스플레이 기술 개발

우리 대학 전기및전자공학부 김상현 교수 연구팀이 *모놀리식 3차원 집적의 장점을 활용한 1,600PPI*에 상응하는 마이크로LED 디스플레이를 구현하는 데 성공했다고 29일 밝혔다. 1,600 PPI는 초고해상도 증강현실(AR)/가상현실(VR) 디스플레이에 적용 가능한 해상도로써 2020년 출시된 오큘러스(Oculus) 社(現 메타(Meta))의 메타 퀘스트 2(Meta quest 2, 442 PPI)의 3.6배에 해당하는 디스플레이 해상도다.

☞ 모놀리식 3차원 집적: 하부 소자 공정 후, 상부의 박막층을 형성하고 상부 소자 공정을 순차적으로 진행함으로써 상하부 소자 간의 정렬도를 극대화할 수 있는 기술로 궁극적 3차원 집적 기술로 불린다.

☞ PPI: Pixel per Inch. 디스플레이에서 1인치에 포함되는 픽셀의 갯수

전기및전자공학부 박주혁 박사과정과 금대명 박사가 제1 저자로 주도하고 백우진 박사과정과 대만의 제스퍼 디스플레이(Jasper Display)의 존슨 쉬(Johnson Shieh) 박사와 협업으로 진행한 이번 연구는 반도체 올림픽이라 불리는 하와이 호놀롤루에서 열린 `VLSI 기술 & 회로 심포지엄 (2022 IEEE Symposium on VLSI Technology & Circuits)'에서 지난 6월 16일에 발표됐다. (논문명 : Monolithic 3D sequential integration realizing 1600-PPI red micro-LED display on Si CMOS driver IC)

VLSI 기술 심포지엄은 국제전자소자학회(International Electron Device Meetings, IEDM)와 더불어 대학 논문의 채택 비율이 25%가 되지 않는 저명한 반도체 소자 분야 최고 권위 학회다.

최근 디스플레이 분야는 각종 TV, 모니터 및 모바일 기기뿐만 아니라 스마트 워치, 스마트 글라스 등의 웨어러블 디바이스까지 그 응용처가 크게 확장됐다. 이처럼 디스플레이의 활용이 점차 다양화되고 고도화됨에 따라 요구되는 픽셀의 크기가 점점 작아지고 있는데, 특히 증강현실(AR)/가상현실(VR) 스마트 글라스 등과 같이 사람의 눈과 매우 가까운 거리를 유지하는 디스플레이의 경우 *픽셀화가 없는 완벽한 이미지의 구현을 위해서는 4K 이상의 고해상도가 요구된다.

☞ 픽셀화(Pixelation): 컴퓨터 그래픽에서 비트맵을 구성하는 작은 단색 정사각형 디스플레이 요소인 개별 픽셀이 보이는 현상.

앞서 언급한 초고해상도 디스플레이를 구현하기 위한 차세대 디스플레이 소자로서 무기물 기반의 인듐갈륨나이트라이드/갈륨나이트라이드(InGaN/GaN), 혹은 알루미늄 갈륨 인듐 인화물/갈륨 인듐 인화물(AlGaInP/GaInP)로 대표되는 3-5(III-V)족 화합물 반도체를 활용한 마이크로 LED 소자가 핵심 소재 및 부품으로써 주목받고 있다. 마이크로 LED는 현재 TV, 모바일 기기에 많이 사용되고 있는 OLED, LCD 디스플레이에 비해 높은 휘도와 명암비, 긴 픽셀 수명 등의 장점이 있어 차세대 디스플레이 소자로서 장점이 뚜렷하다.

☞ III-V 화합물 반도체: 주기율표 III족 원소와 V족 원소가 화합물을 이루고 있는 반도체로 전하 수송 특성 및 광 특성이 매우 우수한 소재.

하지만 무기물 기반 마이크로 LED를 활용해 디스플레이를 제작하기 위해서는 적색, 청색, 녹색의 각 색상의 픽셀을 각각의 기판에서 분리해 디스플레이 패널로 옮기는 패키징 작업이 필수적이다.

기존에 사용돼온 픽앤플레이스(Pick-and-place) 방법은 각각의 픽셀을 일일이 기계적으로 옮겨서 디스플레이 패널에 결합하는 방법으로 픽셀의 크기가 수십 마이크로미터 미만 수준으로 작아지게 되면 기계적인 정렬 정밀도가 저하되고 전사 수율이 감소해 초고해상도 디스플레이에는 적용이 어려울 것이라는 평가를 받고 있다.

연구팀은 이러한 문제의 해결을 위해 디스플레이 구동용 규소 상보적 금속산화물 반도체(이하 Si CMOS) 회로 기판 위에 적색 발광용 LED를 모놀리식 3차원 집적하는 방식을 적용했다. 위 방식은 Si CMOS 회로 위에 마이크로 LED 필름층을 먼저 웨이퍼 본딩을 통해 전사한 뒤, 포토리소그래피 공정으로 픽셀을 구현하는 방법으로, 기계적 픽셀 전사 공정이 제외된다. 이후 연구팀은 Si CMOS 회로상에서 상단에서 하단 방향으로(Top-down) 연속적인 반도체 공정 과정을 통해 고해상도 디스플레이 데모에 성공했다.

이 과정에서 연구팀은 조명용으로 활용돼왔던 무기물 기반 LED 반도체가 아닌 디스플레이용 LED 반도체층을 설계해 발광을 위한 활성층의 두께를 기존의 1/3로 감소시켜, 픽셀 형성에 필요한 식각 공정의 난도를 크게 낮추어 이번 연구성과를 얻어냈다.

또한, 연구팀은 하부 디스플레이 구동 회로의 성능 저하 방지를 위해 350oC 이하에서 상부 III-V 소자를 집적하는 웨이퍼 본딩 등의 초저온 공정을 활용해 상부 소자 집적 후에도 하부 드라이버 IC(Driver IC)의 성능을 그대로 유지할 수 있었다.

이번 연구 결과는 적색 마이크로 LED를 3차원 적층 방식으로 집적해 세계적인 수준의 해상도인 1,600 PPI 구현에 성공한 연구로서 연구에서 활용된 모놀리식 3차원 집적에 관한 연구 결과는 차세대 초고해상도 디스플레이 구현을 위한 좋은 가이드가 될 것으로 예상된다.

김상현 교수는 "향후 유사 공정을 확대 적용해 적색, 녹색, 청색이 모두 포함된 풀 컬러 디스플레이 제작도 가능할 것으로 생각한다ˮ라고 말했다.

한편 이번 연구는 삼성 미래기술육성센터의 지원을 받아 수행했다.

무한대 화소 수준의 초고해상도 AR/VR 디스플레이 기술 개발

우리 대학 전기및전자공학부 김상현 교수 연구팀이 *모놀리식 3차원 집적의 장점을 활용한 1,600PPI*에 상응하는 마이크로LED 디스플레이를 구현하는 데 성공했다고 29일 밝혔다. 1,600 PPI는 초고해상도 증강현실(AR)/가상현실(VR) 디스플레이에 적용 가능한 해상도로써 2020년 출시된 오큘러스(Oculus) 社(現 메타(Meta))의 메타 퀘스트 2(Meta quest 2, 442 PPI)의 3.6배에 해당하는 디스플레이 해상도다.

☞ 모놀리식 3차원 집적: 하부 소자 공정 후, 상부의 박막층을 형성하고 상부 소자 공정을 순차적으로 진행함으로써 상하부 소자 간의 정렬도를 극대화할 수 있는 기술로 궁극적 3차원 집적 기술로 불린다.

☞ PPI: Pixel per Inch. 디스플레이에서 1인치에 포함되는 픽셀의 갯수

전기및전자공학부 박주혁 박사과정과 금대명 박사가 제1 저자로 주도하고 백우진 박사과정과 대만의 제스퍼 디스플레이(Jasper Display)의 존슨 쉬(Johnson Shieh) 박사와 협업으로 진행한 이번 연구는 반도체 올림픽이라 불리는 하와이 호놀롤루에서 열린 `VLSI 기술 & 회로 심포지엄 (2022 IEEE Symposium on VLSI Technology & Circuits)'에서 지난 6월 16일에 발표됐다. (논문명 : Monolithic 3D sequential integration realizing 1600-PPI red micro-LED display on Si CMOS driver IC)

VLSI 기술 심포지엄은 국제전자소자학회(International Electron Device Meetings, IEDM)와 더불어 대학 논문의 채택 비율이 25%가 되지 않는 저명한 반도체 소자 분야 최고 권위 학회다.

최근 디스플레이 분야는 각종 TV, 모니터 및 모바일 기기뿐만 아니라 스마트 워치, 스마트 글라스 등의 웨어러블 디바이스까지 그 응용처가 크게 확장됐다. 이처럼 디스플레이의 활용이 점차 다양화되고 고도화됨에 따라 요구되는 픽셀의 크기가 점점 작아지고 있는데, 특히 증강현실(AR)/가상현실(VR) 스마트 글라스 등과 같이 사람의 눈과 매우 가까운 거리를 유지하는 디스플레이의 경우 *픽셀화가 없는 완벽한 이미지의 구현을 위해서는 4K 이상의 고해상도가 요구된다.

☞ 픽셀화(Pixelation): 컴퓨터 그래픽에서 비트맵을 구성하는 작은 단색 정사각형 디스플레이 요소인 개별 픽셀이 보이는 현상.

앞서 언급한 초고해상도 디스플레이를 구현하기 위한 차세대 디스플레이 소자로서 무기물 기반의 인듐갈륨나이트라이드/갈륨나이트라이드(InGaN/GaN), 혹은 알루미늄 갈륨 인듐 인화물/갈륨 인듐 인화물(AlGaInP/GaInP)로 대표되는 3-5(III-V)족 화합물 반도체를 활용한 마이크로 LED 소자가 핵심 소재 및 부품으로써 주목받고 있다. 마이크로 LED는 현재 TV, 모바일 기기에 많이 사용되고 있는 OLED, LCD 디스플레이에 비해 높은 휘도와 명암비, 긴 픽셀 수명 등의 장점이 있어 차세대 디스플레이 소자로서 장점이 뚜렷하다.

☞ III-V 화합물 반도체: 주기율표 III족 원소와 V족 원소가 화합물을 이루고 있는 반도체로 전하 수송 특성 및 광 특성이 매우 우수한 소재.

하지만 무기물 기반 마이크로 LED를 활용해 디스플레이를 제작하기 위해서는 적색, 청색, 녹색의 각 색상의 픽셀을 각각의 기판에서 분리해 디스플레이 패널로 옮기는 패키징 작업이 필수적이다.

기존에 사용돼온 픽앤플레이스(Pick-and-place) 방법은 각각의 픽셀을 일일이 기계적으로 옮겨서 디스플레이 패널에 결합하는 방법으로 픽셀의 크기가 수십 마이크로미터 미만 수준으로 작아지게 되면 기계적인 정렬 정밀도가 저하되고 전사 수율이 감소해 초고해상도 디스플레이에는 적용이 어려울 것이라는 평가를 받고 있다.

연구팀은 이러한 문제의 해결을 위해 디스플레이 구동용 규소 상보적 금속산화물 반도체(이하 Si CMOS) 회로 기판 위에 적색 발광용 LED를 모놀리식 3차원 집적하는 방식을 적용했다. 위 방식은 Si CMOS 회로 위에 마이크로 LED 필름층을 먼저 웨이퍼 본딩을 통해 전사한 뒤, 포토리소그래피 공정으로 픽셀을 구현하는 방법으로, 기계적 픽셀 전사 공정이 제외된다. 이후 연구팀은 Si CMOS 회로상에서 상단에서 하단 방향으로(Top-down) 연속적인 반도체 공정 과정을 통해 고해상도 디스플레이 데모에 성공했다.

이 과정에서 연구팀은 조명용으로 활용돼왔던 무기물 기반 LED 반도체가 아닌 디스플레이용 LED 반도체층을 설계해 발광을 위한 활성층의 두께를 기존의 1/3로 감소시켜, 픽셀 형성에 필요한 식각 공정의 난도를 크게 낮추어 이번 연구성과를 얻어냈다.

또한, 연구팀은 하부 디스플레이 구동 회로의 성능 저하 방지를 위해 350oC 이하에서 상부 III-V 소자를 집적하는 웨이퍼 본딩 등의 초저온 공정을 활용해 상부 소자 집적 후에도 하부 드라이버 IC(Driver IC)의 성능을 그대로 유지할 수 있었다.

이번 연구 결과는 적색 마이크로 LED를 3차원 적층 방식으로 집적해 세계적인 수준의 해상도인 1,600 PPI 구현에 성공한 연구로서 연구에서 활용된 모놀리식 3차원 집적에 관한 연구 결과는 차세대 초고해상도 디스플레이 구현을 위한 좋은 가이드가 될 것으로 예상된다.

김상현 교수는 "향후 유사 공정을 확대 적용해 적색, 녹색, 청색이 모두 포함된 풀 컬러 디스플레이 제작도 가능할 것으로 생각한다ˮ라고 말했다.

한편 이번 연구는 삼성 미래기술육성센터의 지원을 받아 수행했다.

2022.07.29

조회수 11300

-

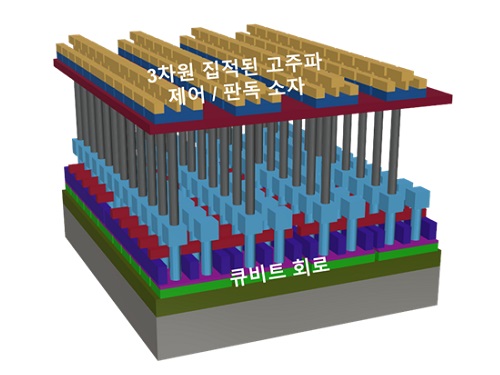

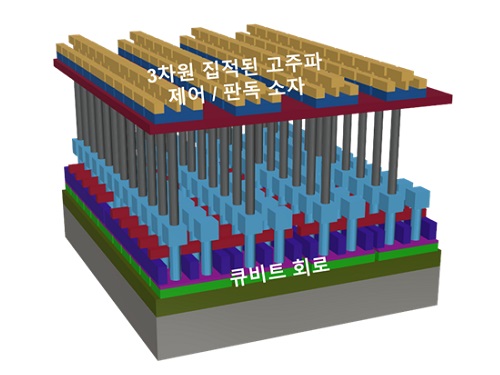

양자컴퓨팅 한계를 극복하는 3차원 반도체 제어/해독 소자 집적 기술 개발

우리 대학 전기및전자공학부 김상현 교수 연구팀이 *모놀리식 3차원 집적의 장점을 활용해 기존 양자 컴퓨팅 시스템의 대규모 큐비트 구현의 한계를 극복하는 3차원 집적된 화합물 반도체 해독 소자 집적 기술을 개발했다고 24일 밝혔다. ‘모놀리식 3차원 집적 초고속 소자’ 연구 (2021년 VLSI 발표, 2021년 IEDM 발표, 2022년 ACS Nano 게재)를 활발하게 진행해 온 연구팀은 양자컴퓨터 판독/해독 소자를 3차원으로 집적할 수 있음을 처음으로 보였다.

☞ 모놀리식 3차원 집적: 반도체 하부 소자 공정 후, 상부의 박막층을 형성하고 상부 소자 공정을 순차적으로 진행함으로써 상하부 소자 간의 정렬도를 극대화할 수 있는 기술로 궁극적 3차원 반도체 집적 기술로 불린다.

우리 대학 전기및전자공학부 김상현 교수 연구팀의 정재용 박사과정이 제1 저자로 주도하고 한국나노기술원 김종민 박사, 한국기초과학지원연구원 박승영 박사 연구팀과의 협업으로 진행한 이번 연구는 반도체 올림픽이라 불리는 ‘VLSI 기술 심포지엄(Symposium on VLSI Technology)’에서 발표됐다. (논문명 : 3D stackable cryogenic InGaAs HEMTs for heterogeneous and monolithic 3D integrated highly scalable quantum computing system).

VLSI 기술 심포지엄은 국제전자소자학회(International Electron Device Meetings, IEDM)와 더불어 대학 논문의 채택 비율이 25%가 되지 않는 저명한 반도체 소자 분야 최고 권위 학회다.

양자컴퓨터는 큐비트 하나에 0과 1을 동시에 담아 여러 연산을 한 번에 처리할 수 있는 차세대 컴퓨터로, 최근에 IBM과 구글 등의 글로벌 기업이 양자 컴퓨터 제작에 성공하면서 양자 컴퓨터가 차세대 컴퓨터로 주목받고 있다.

기존 컴퓨터의 정보 단위인 `비트'의 경우 1 비트당 1개의 값만 가지는 것에 반해, 양자 컴퓨터의 정보 단위인 `큐비트'는 1 큐비트가 0과 1의 상태를 동시에 가진다. 따라서 비트에 비해 큐비트는 2배 빠른 계산이 가능하고, 2큐비트, 4큐비트, 8큐비트로 큐비트 수가 선형적으로 커질수록 처리 계산 속도는 4배, 8배, 16배로 지수적으로 증가한다. 따라서 많은 수의 큐비트를 활용한 대규모 양자컴퓨터 개발이 매우 중요하다. IBM에서는 큐비트 수를 127개로 늘린 `이글'을 작년에 발표했고, IBM 로드맵에 따르면 오는 2025년까지 4,000큐비트, 10년 이내에 10,000큐비트 이상을 탑재한 대규모 양자컴퓨터 개발을 목표로 하고 있다.

특히 큐비트의 수가 많은 대규모 양자컴퓨터 개발을 위해서는 큐비트를 제어/해독하는 소자에 대한 개발이 필수적이다. 기존 컴퓨터와 다르게 양자컴퓨터는 통상 –273 oC 내외의 극저온에서 동작하는 큐비트 하나당 최소 하나의 제어와 해독 연결이 필요하다. 현재는 큐비트 수가 많지 않아 극저온에서 동작하는 큐비트와 상온의 측정 장비를 긴 동축케이블로 연결해 제어/해독하는 방식을 사용하고 있다.

하지만 수천 혹은 수만 개 이상의 큐비트를 활용하는 대규모 양자 컴퓨팅에서 이러한 방식을 활용하면 양자 컴퓨터 크기가 매우 커지고 긴 연결 거리로 인해 신호 손실도 커 대규모 양자컴퓨터 구현이 매우 어려워진다. 따라서 큐비트를 제어/해독에 활용할 수 있는 저전력, 저잡음, 초고속 특성의 극저온 소자를 큐비트와 일대일로 연결할 수 있는 시스템 구성이 매우 중요하다.

연구팀은 이러한 문제 해결을 위해 큐비트 회로 위에 저전력, 저잡음 초고속 특성이 매우 뛰어난 *III-V 화합물 반도체 *고전자 이동 트랜지스터(HEMT)를 3차원으로 집적해 수천 혹은 수만 개의 큐비트에 아주 짧은 거리에서 일대일로 연결 가능한 구조를 제시했다.

☞ III-V 화합물 반도체: 주기율표 III족 원소와 V족 원소가 화합물을 이루고 있는 반도체로 전하 수송 특성 및 광 특성이 매우 우수한 소재.

☞ HEMT: High-Electron Mobility Transistor

연구팀은 250oC 이하에서 상부 제어/해독 소자를 집적하는 웨이퍼 본딩 등의 초저온 공정을 활용해 이후 하부 큐비트 회로의 성능 저하 없이 3차원 집적을 할 수 있도록 했다.

연구진은 이러한 3차원 집적 형태의 제어/해독 소자를 최초로 제시 및 구현했을 뿐만 아니라 소자의 성능 면에서도 극저온에서 세계 최고 수준의 차단주파수 특성을 달성했다.

김상현 교수는 "이번 기술은 향후 대규모 양자컴퓨터의 제어/판독 회로에 응용이 가능할 것으로 생각한다ˮ라며 "모놀리식 3차원 초고속 소자의 경우 양자컴퓨터뿐만이 아니라 6G 무선통신 등 다양한 분야에서 응용할 수 있어 그 확장성이 매우 큰 기술이며 앞으로도 다양한 분야에서 활용할 수 있도록 후속 연구에 힘쓰겠다ˮ라고 말했다.

한편 이번 연구는 한국연구재단 지능형반도체기술개발사업, 경기도 시스템반도체 국산화 연구지원 사업, 한국기초과학지원연구원 분석과학연구장비개발사업(BIG사업) 등의 지원을 받아 수행됐다.

양자컴퓨팅 한계를 극복하는 3차원 반도체 제어/해독 소자 집적 기술 개발

우리 대학 전기및전자공학부 김상현 교수 연구팀이 *모놀리식 3차원 집적의 장점을 활용해 기존 양자 컴퓨팅 시스템의 대규모 큐비트 구현의 한계를 극복하는 3차원 집적된 화합물 반도체 해독 소자 집적 기술을 개발했다고 24일 밝혔다. ‘모놀리식 3차원 집적 초고속 소자’ 연구 (2021년 VLSI 발표, 2021년 IEDM 발표, 2022년 ACS Nano 게재)를 활발하게 진행해 온 연구팀은 양자컴퓨터 판독/해독 소자를 3차원으로 집적할 수 있음을 처음으로 보였다.

☞ 모놀리식 3차원 집적: 반도체 하부 소자 공정 후, 상부의 박막층을 형성하고 상부 소자 공정을 순차적으로 진행함으로써 상하부 소자 간의 정렬도를 극대화할 수 있는 기술로 궁극적 3차원 반도체 집적 기술로 불린다.

우리 대학 전기및전자공학부 김상현 교수 연구팀의 정재용 박사과정이 제1 저자로 주도하고 한국나노기술원 김종민 박사, 한국기초과학지원연구원 박승영 박사 연구팀과의 협업으로 진행한 이번 연구는 반도체 올림픽이라 불리는 ‘VLSI 기술 심포지엄(Symposium on VLSI Technology)’에서 발표됐다. (논문명 : 3D stackable cryogenic InGaAs HEMTs for heterogeneous and monolithic 3D integrated highly scalable quantum computing system).

VLSI 기술 심포지엄은 국제전자소자학회(International Electron Device Meetings, IEDM)와 더불어 대학 논문의 채택 비율이 25%가 되지 않는 저명한 반도체 소자 분야 최고 권위 학회다.

양자컴퓨터는 큐비트 하나에 0과 1을 동시에 담아 여러 연산을 한 번에 처리할 수 있는 차세대 컴퓨터로, 최근에 IBM과 구글 등의 글로벌 기업이 양자 컴퓨터 제작에 성공하면서 양자 컴퓨터가 차세대 컴퓨터로 주목받고 있다.

기존 컴퓨터의 정보 단위인 `비트'의 경우 1 비트당 1개의 값만 가지는 것에 반해, 양자 컴퓨터의 정보 단위인 `큐비트'는 1 큐비트가 0과 1의 상태를 동시에 가진다. 따라서 비트에 비해 큐비트는 2배 빠른 계산이 가능하고, 2큐비트, 4큐비트, 8큐비트로 큐비트 수가 선형적으로 커질수록 처리 계산 속도는 4배, 8배, 16배로 지수적으로 증가한다. 따라서 많은 수의 큐비트를 활용한 대규모 양자컴퓨터 개발이 매우 중요하다. IBM에서는 큐비트 수를 127개로 늘린 `이글'을 작년에 발표했고, IBM 로드맵에 따르면 오는 2025년까지 4,000큐비트, 10년 이내에 10,000큐비트 이상을 탑재한 대규모 양자컴퓨터 개발을 목표로 하고 있다.

특히 큐비트의 수가 많은 대규모 양자컴퓨터 개발을 위해서는 큐비트를 제어/해독하는 소자에 대한 개발이 필수적이다. 기존 컴퓨터와 다르게 양자컴퓨터는 통상 –273 oC 내외의 극저온에서 동작하는 큐비트 하나당 최소 하나의 제어와 해독 연결이 필요하다. 현재는 큐비트 수가 많지 않아 극저온에서 동작하는 큐비트와 상온의 측정 장비를 긴 동축케이블로 연결해 제어/해독하는 방식을 사용하고 있다.

하지만 수천 혹은 수만 개 이상의 큐비트를 활용하는 대규모 양자 컴퓨팅에서 이러한 방식을 활용하면 양자 컴퓨터 크기가 매우 커지고 긴 연결 거리로 인해 신호 손실도 커 대규모 양자컴퓨터 구현이 매우 어려워진다. 따라서 큐비트를 제어/해독에 활용할 수 있는 저전력, 저잡음, 초고속 특성의 극저온 소자를 큐비트와 일대일로 연결할 수 있는 시스템 구성이 매우 중요하다.

연구팀은 이러한 문제 해결을 위해 큐비트 회로 위에 저전력, 저잡음 초고속 특성이 매우 뛰어난 *III-V 화합물 반도체 *고전자 이동 트랜지스터(HEMT)를 3차원으로 집적해 수천 혹은 수만 개의 큐비트에 아주 짧은 거리에서 일대일로 연결 가능한 구조를 제시했다.

☞ III-V 화합물 반도체: 주기율표 III족 원소와 V족 원소가 화합물을 이루고 있는 반도체로 전하 수송 특성 및 광 특성이 매우 우수한 소재.

☞ HEMT: High-Electron Mobility Transistor

연구팀은 250oC 이하에서 상부 제어/해독 소자를 집적하는 웨이퍼 본딩 등의 초저온 공정을 활용해 이후 하부 큐비트 회로의 성능 저하 없이 3차원 집적을 할 수 있도록 했다.

연구진은 이러한 3차원 집적 형태의 제어/해독 소자를 최초로 제시 및 구현했을 뿐만 아니라 소자의 성능 면에서도 극저온에서 세계 최고 수준의 차단주파수 특성을 달성했다.

김상현 교수는 "이번 기술은 향후 대규모 양자컴퓨터의 제어/판독 회로에 응용이 가능할 것으로 생각한다ˮ라며 "모놀리식 3차원 초고속 소자의 경우 양자컴퓨터뿐만이 아니라 6G 무선통신 등 다양한 분야에서 응용할 수 있어 그 확장성이 매우 큰 기술이며 앞으로도 다양한 분야에서 활용할 수 있도록 후속 연구에 힘쓰겠다ˮ라고 말했다.

한편 이번 연구는 한국연구재단 지능형반도체기술개발사업, 경기도 시스템반도체 국산화 연구지원 사업, 한국기초과학지원연구원 분석과학연구장비개발사업(BIG사업) 등의 지원을 받아 수행됐다.

2022.06.24

조회수 11067

-

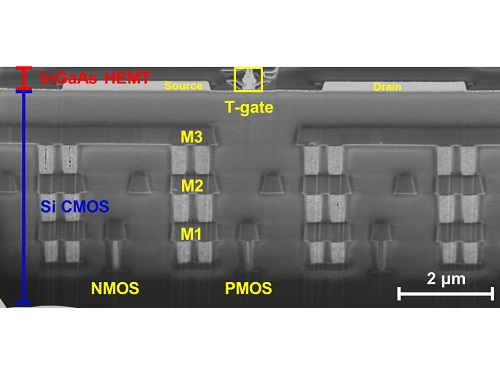

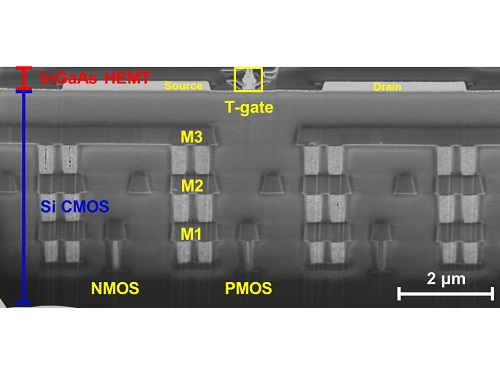

3차원 적층형 화합물 반도체 소자 제작 성공

우리 대학 전기및전자공학부 김상현 교수 연구팀이 *모놀리식 3차원 집적의 장점을 극대화해 기존의 통신 소자의 단점을 극복하는 화합물 반도체 소자 집적 기술을 개발했다고 14일 밝혔다.

☞ 모놀리식 3차원 집적: 하부 소자 공정 후, 상부의 박막층을 형성하고 상부 소자 공정을 순차적으로 진행함으로써 상하부 소자 간의 정렬도를 극대화할 수 있는 기술로 궁극적 3차원 집적 기술로 불린다.

우리 대학 전기및전자공학부 정재용 박사과정이 제1 저자로 주도하고 한국나노기술원 김종민 박사, 광주과학기술원 장재형 교수 연구팀과의 협업으로 진행한 이번 연구는 반도체 올림픽이라 불리는 ‘VLSI 기술 심포지엄(Symposium on VLSI Technology)’에서 발표됐다. (논문명 : High-performance InGaAs-On-Insulator HEMTs on Si CMOS for Substrate Coupling Noise-free Monolithic 3D Mixed-Signal IC).

VLSI 기술 심포지엄은 국제전자소자학회(International Electron Device Meetings, IEDM)와 더불어 대학 논문의 채택비율이 25%가 되지 않는 저명한 반도체 소자 분야 최고 권위 학회다.

반도체 소자는 4차 산업 혁명의 특징인 초연결성 구현을 위한 핵심 통신 소재 및 부품으로서 주목받고 있다.

특히 통신 신호, 양자 신호는 아날로그 형태의 신호이고 신호전달 과정에서 신호의 크기가 약해지거나 잡음이 생겨 신호의 왜곡이 생기기도 한다. 따라서 이러한 신호를 주고받을 때 고속으로 신호의 증폭이 필요한데 이러한 증폭 소자에서는 초고속, 고출력, 저전력, 저잡음 등의 특성이 매우 중요하다. 또한 통신 기술이 발전함에 따라 이를 구성하는 시스템은 점점 더 복잡해져 고집적 소자 제작기술이 매우 중요하다.

통신 소자는 통상적으로 두 가지 방식으로 구현된다. 실리콘(Si)을 사용해 집적도 높은 Si CMOS를 이용해 증폭 소자를 구현하는 방법과 *III-V 화합물 반도체를 증폭 소자로 제작하고 기타 소자들을 Si CMOS로 제작해 패키징 하는 방식이 있다. 그러나 각각의 방식은 단점이 존재한다. 기존의 실리콘(Si) 기술은 물성적 한계로 인해 차단주파수 특성 등 통신 소자에 중요한 소자 성능 향상이 어려우며 기판 커플링 잡음 등 복잡한 신호 간섭에 의한 잡음 증가 문제가 존재한다. 반면, III-V 화합물 반도체 기술은 소자 자체의 잡음 특성은 우수하지만 다른 부품과의 집적/패키징 공정이 복잡하고 이러한 패키징 공정으로 인해 신호의 손실이 발생하는 문제가 존재한다.

☞ III-V 화합물 반도체: 주기율표 III족 원소와 V족 원소가 화합물을 이루고 있는 반도체로 전하 수송 특성 및 광 특성이 매우 우수한 소재

연구팀은 이러한 문제 해결을 위해 증폭 소자 이외의 소자 및 디지털 회로에서 좋은 성능을 낼 수 있는 Si CMOS 기판 위에 아날로그 신호 증폭 성능이 매우 우수한 III-V 화합물 반도체 *HEMT를 3차원 집적해 Si CMOS와 III-V HEMT의 장점을 극대화하는 공정 및 소자 구조를 제시했다. 3층으로 소자를 쌓아나감으로써 같은 기판 위에 집적할 수 있는 방식이다. 이와 동시에 기판 신호 간섭에 의한 잡음을 제거할 수 있음을 증명했다.

☞ HEMT: High-Electron Mobility Transistor

연구팀은 하부 Si CMOS의 성능 저하 방지를 위해 300oC 이하에서 상부 III-V 소자를 집적하는 웨이퍼 본딩 등의 초저온 공정을 활용해 상부 소자 집적 후에도 하부 Si CMOS의 성능을 그대로 유지할 수 있었다.

또한 고성능 상부 III-V 소자 제작을 위해서 InGaAs/InAs/InGaAs의 양자우물 구조를 도입해 높은 전자 수송 특성을 실현했으며 100 나노미터(nm) 노드 공정 수준으로도 세계 최고 수준의 차단 주파수 특성을 달성했다. 이는 10 나노미터(nm) 이하 급의 최첨단 공정을 사용하지 않고도 그 이상의 우수한 성능을 낼 수 있는 융합 기술로 향후 기존과 다른 형태의 파운드리 비즈니스 방식의 도입 가능성을 증명했다고 할 수 있다.

더불어 연구진은 이러한 3차원 집적 형태로 소자를 제작함으로써 기존에 SI CMOS에서 존재하는 기판 간섭에 의한 잡음을 해결할 수 있음을 실험을 통해 최초로 증명했다.

김상현 교수는 “디지털 회로 및 다양한 수동소자 제작에 최적화된 Si CMOS 기판 위에 증폭기 등의 능동소자 특성이 현존하는 어떤 물질보다 우수한 III-V 화합물 반도체 소자를 동시 집적할 가능성을 최초로 입증한 연구로, 향후 통신 소자 등에 응용이 가능할 것으로 생각한다”라며 “이번 기술은 향후 양자 큐빗의 해독 회로에도 응용할 수 있어 그 확장성이 매우 큰 기술이다. 다양한 분야에서 활용할 수 있도록 후속 연구에 힘쓰겠다”라고 말했다.

한편 이번 연구는 한국연구재단 지능형반도체기술개발사업, 경기도 시스템반도체 국산화 연구지원 사업 등의 지원을 받아 수행됐다.

3차원 적층형 화합물 반도체 소자 제작 성공

우리 대학 전기및전자공학부 김상현 교수 연구팀이 *모놀리식 3차원 집적의 장점을 극대화해 기존의 통신 소자의 단점을 극복하는 화합물 반도체 소자 집적 기술을 개발했다고 14일 밝혔다.

☞ 모놀리식 3차원 집적: 하부 소자 공정 후, 상부의 박막층을 형성하고 상부 소자 공정을 순차적으로 진행함으로써 상하부 소자 간의 정렬도를 극대화할 수 있는 기술로 궁극적 3차원 집적 기술로 불린다.

우리 대학 전기및전자공학부 정재용 박사과정이 제1 저자로 주도하고 한국나노기술원 김종민 박사, 광주과학기술원 장재형 교수 연구팀과의 협업으로 진행한 이번 연구는 반도체 올림픽이라 불리는 ‘VLSI 기술 심포지엄(Symposium on VLSI Technology)’에서 발표됐다. (논문명 : High-performance InGaAs-On-Insulator HEMTs on Si CMOS for Substrate Coupling Noise-free Monolithic 3D Mixed-Signal IC).

VLSI 기술 심포지엄은 국제전자소자학회(International Electron Device Meetings, IEDM)와 더불어 대학 논문의 채택비율이 25%가 되지 않는 저명한 반도체 소자 분야 최고 권위 학회다.

반도체 소자는 4차 산업 혁명의 특징인 초연결성 구현을 위한 핵심 통신 소재 및 부품으로서 주목받고 있다.

특히 통신 신호, 양자 신호는 아날로그 형태의 신호이고 신호전달 과정에서 신호의 크기가 약해지거나 잡음이 생겨 신호의 왜곡이 생기기도 한다. 따라서 이러한 신호를 주고받을 때 고속으로 신호의 증폭이 필요한데 이러한 증폭 소자에서는 초고속, 고출력, 저전력, 저잡음 등의 특성이 매우 중요하다. 또한 통신 기술이 발전함에 따라 이를 구성하는 시스템은 점점 더 복잡해져 고집적 소자 제작기술이 매우 중요하다.

통신 소자는 통상적으로 두 가지 방식으로 구현된다. 실리콘(Si)을 사용해 집적도 높은 Si CMOS를 이용해 증폭 소자를 구현하는 방법과 *III-V 화합물 반도체를 증폭 소자로 제작하고 기타 소자들을 Si CMOS로 제작해 패키징 하는 방식이 있다. 그러나 각각의 방식은 단점이 존재한다. 기존의 실리콘(Si) 기술은 물성적 한계로 인해 차단주파수 특성 등 통신 소자에 중요한 소자 성능 향상이 어려우며 기판 커플링 잡음 등 복잡한 신호 간섭에 의한 잡음 증가 문제가 존재한다. 반면, III-V 화합물 반도체 기술은 소자 자체의 잡음 특성은 우수하지만 다른 부품과의 집적/패키징 공정이 복잡하고 이러한 패키징 공정으로 인해 신호의 손실이 발생하는 문제가 존재한다.

☞ III-V 화합물 반도체: 주기율표 III족 원소와 V족 원소가 화합물을 이루고 있는 반도체로 전하 수송 특성 및 광 특성이 매우 우수한 소재

연구팀은 이러한 문제 해결을 위해 증폭 소자 이외의 소자 및 디지털 회로에서 좋은 성능을 낼 수 있는 Si CMOS 기판 위에 아날로그 신호 증폭 성능이 매우 우수한 III-V 화합물 반도체 *HEMT를 3차원 집적해 Si CMOS와 III-V HEMT의 장점을 극대화하는 공정 및 소자 구조를 제시했다. 3층으로 소자를 쌓아나감으로써 같은 기판 위에 집적할 수 있는 방식이다. 이와 동시에 기판 신호 간섭에 의한 잡음을 제거할 수 있음을 증명했다.

☞ HEMT: High-Electron Mobility Transistor

연구팀은 하부 Si CMOS의 성능 저하 방지를 위해 300oC 이하에서 상부 III-V 소자를 집적하는 웨이퍼 본딩 등의 초저온 공정을 활용해 상부 소자 집적 후에도 하부 Si CMOS의 성능을 그대로 유지할 수 있었다.

또한 고성능 상부 III-V 소자 제작을 위해서 InGaAs/InAs/InGaAs의 양자우물 구조를 도입해 높은 전자 수송 특성을 실현했으며 100 나노미터(nm) 노드 공정 수준으로도 세계 최고 수준의 차단 주파수 특성을 달성했다. 이는 10 나노미터(nm) 이하 급의 최첨단 공정을 사용하지 않고도 그 이상의 우수한 성능을 낼 수 있는 융합 기술로 향후 기존과 다른 형태의 파운드리 비즈니스 방식의 도입 가능성을 증명했다고 할 수 있다.

더불어 연구진은 이러한 3차원 집적 형태로 소자를 제작함으로써 기존에 SI CMOS에서 존재하는 기판 간섭에 의한 잡음을 해결할 수 있음을 실험을 통해 최초로 증명했다.

김상현 교수는 “디지털 회로 및 다양한 수동소자 제작에 최적화된 Si CMOS 기판 위에 증폭기 등의 능동소자 특성이 현존하는 어떤 물질보다 우수한 III-V 화합물 반도체 소자를 동시 집적할 가능성을 최초로 입증한 연구로, 향후 통신 소자 등에 응용이 가능할 것으로 생각한다”라며 “이번 기술은 향후 양자 큐빗의 해독 회로에도 응용할 수 있어 그 확장성이 매우 큰 기술이다. 다양한 분야에서 활용할 수 있도록 후속 연구에 힘쓰겠다”라고 말했다.

한편 이번 연구는 한국연구재단 지능형반도체기술개발사업, 경기도 시스템반도체 국산화 연구지원 사업 등의 지원을 받아 수행됐다.

2021.06.14

조회수 55072

KAIST, 인공지능 반도체 생태계를 선도하다

인공지능 반도체(이하 AI 반도체)가 국가적인 전략기술로 두드러지면서 KAIST의 관련 성과도 주목받고 있다. 과학기술정보통신부는 지난해 2030년 세계 AI 반도체 시장 20% 점유를 목표로 인공지능 반도체 지원사업에 본격적으로 착수한 바 있다. 올해에는 산학연 논의를 거쳐 5년간 1조 200억 원을 투입하는 `인공지능 반도체 산업 성장 지원대책'으로 지원을 확대했다. 이에 따라 AI 반도체 전문가 양성을 위해 주요 대학들의 행보도 분주해졌다.

KAIST는 반도체와 인공지능 양대 핵심 분야에서 최상급의 교육, 연구 역량을 쌓아 왔다. 반도체 분야에서는 지난 17년 동안 메사추세츠 공과대학(이하 MIT), 스탠퍼드(Stanford)와 같은 세계적인 학교를 제치고 국제반도체회로학회(이하 ISSCC, International Solid State Circuit Conference)에서 대학 중 1위를 지켜 왔다는 점이 돋보인다. ISSCC는 1954년 설립된 반도체 집적회로 설계 분야 세계 최고 권위 학회다. 참가자 중 60% 이상이 삼성, 퀄컴, TSMC, 인텔을 비롯한 산업계 소속일만큼 산업적인 실용성을 중시해서 `반도체 설계 올림픽'이라는 별명도 있다.

KAIST는 ISSCC에서 채택 논문 수 기준 매년 전 세계 대학교 중 1~2위를 유지했다. 최근 17년간 평균 채택 논문 수를 살펴보면 압도적인 선두다. 해당 기간 채택된 KAIST의 논문은 평균 8.4편으로, 경쟁자인 MIT(4.6편)와 캘리포니아대학교 로스앤젤레스(UCLA)(3.6편)에 비해 두 배 가까운 성과다. 국내에서는 반도체 설계 분야 부동의 1위인 삼성에 이어 종합 2위 자리를 유지하고 있다. 그럴 뿐만 아니라 ISSCC와 쌍벽을 이루는 집적회로 분야 학술대회인 초고밀도집적회로학회에서도 KAIST는 2022년 전 세계 대학 중 1위를 기록했다.

KAIST의 연구진들이 반도체 산업 핵심 분야 전반에서 신기술을 발표해 연구의 질적인 수준도 높다. 전기및전자공학부 정명수 교수 연구팀은 고성능 저전력을 추구하는 현재 업계의 수요에 대응해 전력 공급 없이도 동작을 유지하는 컴퓨터를 개발했다. 소재 분야에서는 신소재공학과의 박병국 교수 연구팀이 기존의 메모리에 비해 동작 속도가 10배 이상 빠른 `스핀궤도토크 자성메모리' 소자를 개발해서 기존 `폰노이만 구조'의 한계를 극복하는 방안을 제시하기도 했다.

이처럼 현재 반도체 산업의 주요 과제에 솔루션을 제공하는 한편으로 미래의 새로운 반도체 분야를 선점하는 데 필요한 신기술 개발도 활발하다. 암호 및 비선형 연산 분야에서 차세대 컴퓨팅으로 주목받는 양자컴퓨팅 분야에서는 전기및전자공학부 김상현 교수 연구팀이 3차원 집적 기술을 세계 최초로 선보였다. 신경계의 원리를 활용해 인공지능 분야에서 발군의 성능을 보일 것으로 기대되는 뉴로모픽 컴퓨팅에서는 전기및전자공학부 최신현 교수 연구팀이 신경세포를 모사하는 차세대 멤리스터를 개발 중이다.

인공지능 분야에서도 비약적으로 성장했다. 인공지능 분야의 양대 세계 최고 권위 학회인 국제머신러닝학회(ICML)과 인공신경망학회(NeurIPS) 논문 수 기준으로 KAIST는 2020년 세계 6위, 아시아에서는 1위를 기록했다. KAIST의 순위는 2012년부터 꾸준히 우상향 그래프를 그려 8년만에 37위에서 6위로, 무려 31계단이나 도약했다. 2021년에는 인공지능 분야 톱 학회 11개에 발표된 한국 논문 중 약 40%에 달하는 129편이 KAIST에서 나왔다. KAIST의 이러한 활약에 힘입어 2021년 한국은 글로벌 인공지능 톱 학회 등재 논문 수 기준으로 미국, 중국, 영국, 캐나다, 독일에 이어 6위에 올랐다.

내용 면에서도 KAIST의 인공지능 연구는 최전선에 있다. 전기및전자공학부 유회준 교수 연구팀은 모바일기기에서 인공지능 실시간 학습을 구현해 에지 네트워크의 단점을 보완했다. 인공지능을 구현하려면 데이터 축적관 막대한 양의 연산이 필요한데, 이를 위해 고성능 서버가 방대한 연산을 담당하고 사용자 단말은 데이터 수집과 간단한 연산만 하는 `에지 네트워크'가 사용된다. 유 교수의 연구는 사용자 단말에 학습 능력을 부여함으로써 인공지능의 처리 속도와 성능을 크게 높일 수 있다.

지난 6월에는 전산학부 김민수 교수 연구팀이 초대규모 인공지능 모델 처리에 꼭 필요한 솔루션을 제시했다. 연구팀이 개발한 초대규모 기계학습 시스템은 현재 업계에서 주로 사용되는 구글의 텐서플로우(Tensorflow)나 IBM의 시스템DS 대비 최대 8.8배나 빠른 속도를 달성할 수 있을 것으로 기대된다.

KAIST는 반도체와 인공지능이 결합된 AI 반도체 분야에서도 주목할만한 성과를 내고 있다. 2020년 전기및전자공학부 유민수 교수 연구팀은 세계 최초로 추천시스템에 최적화된 AI 반도체를 개발하는 데 성공했다. 인공지능 추천시스템은 방대한 콘텐츠와 사용자 정보를 다룬다는 특성상 범용 인공지능 시스템으로 운영하면 병목현상으로 성능에 한계가 있다. 유민수 교수팀은 `프로세싱-인-메모리(이하 PIM, Processing-In-Memory)' 기술을 기반으로 기존 시스템 대비 최대 21배 빠른 속도를 낼 수 있는 반도체를 개발했다. PIM은 처리할 데이터를 임시로 저장하기만 하던 `램'에서 연산까지 수행해 효율을 높이는 기술이다. PIM 기술이 본격적으로 상용화되면 메모리 분야에서 강세인 한국 기업의 AI 반도체 시장 경쟁력이 비약적으로 높아질 것으로 기대된다.

KAIST는 그간의 성과에 안주하지 않고 인공지능 및 반도체, 그리고 AI 반도체 분야 초격차를 유지하고자 다각적인 노력을 기울이고 있다. 1990년 국내 최초로 인공지능연구센터를 설립한 데 이어 2019년에는 김재철AI대학원을 개설해 전문인력을 양성 중이다. 2020년에는 인공지능과 반도체 연구를 융합해 ITRC 인공지능반도체시스템 연구센터가 출범했으며, 2021년에는 인공지능을 다양한 분야에 접목하는 `AI+X' 연구를 활성화하고자 김재철AI대학원과 별도로 AI 연구원을 설립했다.

KAIST는 이러한 노력으로 축적된 내적 역량을 바탕으로 네이버 등 기업과 공동연구센터를 설립하는 한편, 화성시와 같은 지자체와 협력해 동시다발적인 전문인력 양성에 나섰다. 지난 2021년에는 삼성전자와 함께 반도체시스템공학과 설립 협약을 체결하고 새로운 반도체 전문인력 교육과정을 준비하고 있다. 새로 설립되는 반도체시스템공학과는 2023년부터 매년 100명 내외의 신입생을 선발하고, 이들이 전문역량을 꽃피울 수 있도록 학생 전원에게 특별장학금을 지급할 예정이다. 또한 산업계와의 긴밀한 협력을 통해 삼성전자 견학과 인턴십, 공동 워크숍을 지원해 현장에 밀착한 교육을 제공할 예정이다.

KAIST는 국내 반도체 분야 박사 인력의 25%, 박사 출신 중견 및 벤처기업 CEO의 20%를 배출하며 한국 반도체 산업 생태계가 성장하는 데 중대한 공헌을 했다. 본격적으로 열린 AI 반도체 경쟁 체제를 앞두고 KAIST가 다시 산업 생태계의 구심점 역할을 할지 귀추가 주목된다.

2022.08.04 조회수 18972

KAIST, 인공지능 반도체 생태계를 선도하다

인공지능 반도체(이하 AI 반도체)가 국가적인 전략기술로 두드러지면서 KAIST의 관련 성과도 주목받고 있다. 과학기술정보통신부는 지난해 2030년 세계 AI 반도체 시장 20% 점유를 목표로 인공지능 반도체 지원사업에 본격적으로 착수한 바 있다. 올해에는 산학연 논의를 거쳐 5년간 1조 200억 원을 투입하는 `인공지능 반도체 산업 성장 지원대책'으로 지원을 확대했다. 이에 따라 AI 반도체 전문가 양성을 위해 주요 대학들의 행보도 분주해졌다.

KAIST는 반도체와 인공지능 양대 핵심 분야에서 최상급의 교육, 연구 역량을 쌓아 왔다. 반도체 분야에서는 지난 17년 동안 메사추세츠 공과대학(이하 MIT), 스탠퍼드(Stanford)와 같은 세계적인 학교를 제치고 국제반도체회로학회(이하 ISSCC, International Solid State Circuit Conference)에서 대학 중 1위를 지켜 왔다는 점이 돋보인다. ISSCC는 1954년 설립된 반도체 집적회로 설계 분야 세계 최고 권위 학회다. 참가자 중 60% 이상이 삼성, 퀄컴, TSMC, 인텔을 비롯한 산업계 소속일만큼 산업적인 실용성을 중시해서 `반도체 설계 올림픽'이라는 별명도 있다.

KAIST는 ISSCC에서 채택 논문 수 기준 매년 전 세계 대학교 중 1~2위를 유지했다. 최근 17년간 평균 채택 논문 수를 살펴보면 압도적인 선두다. 해당 기간 채택된 KAIST의 논문은 평균 8.4편으로, 경쟁자인 MIT(4.6편)와 캘리포니아대학교 로스앤젤레스(UCLA)(3.6편)에 비해 두 배 가까운 성과다. 국내에서는 반도체 설계 분야 부동의 1위인 삼성에 이어 종합 2위 자리를 유지하고 있다. 그럴 뿐만 아니라 ISSCC와 쌍벽을 이루는 집적회로 분야 학술대회인 초고밀도집적회로학회에서도 KAIST는 2022년 전 세계 대학 중 1위를 기록했다.

KAIST의 연구진들이 반도체 산업 핵심 분야 전반에서 신기술을 발표해 연구의 질적인 수준도 높다. 전기및전자공학부 정명수 교수 연구팀은 고성능 저전력을 추구하는 현재 업계의 수요에 대응해 전력 공급 없이도 동작을 유지하는 컴퓨터를 개발했다. 소재 분야에서는 신소재공학과의 박병국 교수 연구팀이 기존의 메모리에 비해 동작 속도가 10배 이상 빠른 `스핀궤도토크 자성메모리' 소자를 개발해서 기존 `폰노이만 구조'의 한계를 극복하는 방안을 제시하기도 했다.

이처럼 현재 반도체 산업의 주요 과제에 솔루션을 제공하는 한편으로 미래의 새로운 반도체 분야를 선점하는 데 필요한 신기술 개발도 활발하다. 암호 및 비선형 연산 분야에서 차세대 컴퓨팅으로 주목받는 양자컴퓨팅 분야에서는 전기및전자공학부 김상현 교수 연구팀이 3차원 집적 기술을 세계 최초로 선보였다. 신경계의 원리를 활용해 인공지능 분야에서 발군의 성능을 보일 것으로 기대되는 뉴로모픽 컴퓨팅에서는 전기및전자공학부 최신현 교수 연구팀이 신경세포를 모사하는 차세대 멤리스터를 개발 중이다.

인공지능 분야에서도 비약적으로 성장했다. 인공지능 분야의 양대 세계 최고 권위 학회인 국제머신러닝학회(ICML)과 인공신경망학회(NeurIPS) 논문 수 기준으로 KAIST는 2020년 세계 6위, 아시아에서는 1위를 기록했다. KAIST의 순위는 2012년부터 꾸준히 우상향 그래프를 그려 8년만에 37위에서 6위로, 무려 31계단이나 도약했다. 2021년에는 인공지능 분야 톱 학회 11개에 발표된 한국 논문 중 약 40%에 달하는 129편이 KAIST에서 나왔다. KAIST의 이러한 활약에 힘입어 2021년 한국은 글로벌 인공지능 톱 학회 등재 논문 수 기준으로 미국, 중국, 영국, 캐나다, 독일에 이어 6위에 올랐다.

내용 면에서도 KAIST의 인공지능 연구는 최전선에 있다. 전기및전자공학부 유회준 교수 연구팀은 모바일기기에서 인공지능 실시간 학습을 구현해 에지 네트워크의 단점을 보완했다. 인공지능을 구현하려면 데이터 축적관 막대한 양의 연산이 필요한데, 이를 위해 고성능 서버가 방대한 연산을 담당하고 사용자 단말은 데이터 수집과 간단한 연산만 하는 `에지 네트워크'가 사용된다. 유 교수의 연구는 사용자 단말에 학습 능력을 부여함으로써 인공지능의 처리 속도와 성능을 크게 높일 수 있다.

지난 6월에는 전산학부 김민수 교수 연구팀이 초대규모 인공지능 모델 처리에 꼭 필요한 솔루션을 제시했다. 연구팀이 개발한 초대규모 기계학습 시스템은 현재 업계에서 주로 사용되는 구글의 텐서플로우(Tensorflow)나 IBM의 시스템DS 대비 최대 8.8배나 빠른 속도를 달성할 수 있을 것으로 기대된다.

KAIST는 반도체와 인공지능이 결합된 AI 반도체 분야에서도 주목할만한 성과를 내고 있다. 2020년 전기및전자공학부 유민수 교수 연구팀은 세계 최초로 추천시스템에 최적화된 AI 반도체를 개발하는 데 성공했다. 인공지능 추천시스템은 방대한 콘텐츠와 사용자 정보를 다룬다는 특성상 범용 인공지능 시스템으로 운영하면 병목현상으로 성능에 한계가 있다. 유민수 교수팀은 `프로세싱-인-메모리(이하 PIM, Processing-In-Memory)' 기술을 기반으로 기존 시스템 대비 최대 21배 빠른 속도를 낼 수 있는 반도체를 개발했다. PIM은 처리할 데이터를 임시로 저장하기만 하던 `램'에서 연산까지 수행해 효율을 높이는 기술이다. PIM 기술이 본격적으로 상용화되면 메모리 분야에서 강세인 한국 기업의 AI 반도체 시장 경쟁력이 비약적으로 높아질 것으로 기대된다.

KAIST는 그간의 성과에 안주하지 않고 인공지능 및 반도체, 그리고 AI 반도체 분야 초격차를 유지하고자 다각적인 노력을 기울이고 있다. 1990년 국내 최초로 인공지능연구센터를 설립한 데 이어 2019년에는 김재철AI대학원을 개설해 전문인력을 양성 중이다. 2020년에는 인공지능과 반도체 연구를 융합해 ITRC 인공지능반도체시스템 연구센터가 출범했으며, 2021년에는 인공지능을 다양한 분야에 접목하는 `AI+X' 연구를 활성화하고자 김재철AI대학원과 별도로 AI 연구원을 설립했다.

KAIST는 이러한 노력으로 축적된 내적 역량을 바탕으로 네이버 등 기업과 공동연구센터를 설립하는 한편, 화성시와 같은 지자체와 협력해 동시다발적인 전문인력 양성에 나섰다. 지난 2021년에는 삼성전자와 함께 반도체시스템공학과 설립 협약을 체결하고 새로운 반도체 전문인력 교육과정을 준비하고 있다. 새로 설립되는 반도체시스템공학과는 2023년부터 매년 100명 내외의 신입생을 선발하고, 이들이 전문역량을 꽃피울 수 있도록 학생 전원에게 특별장학금을 지급할 예정이다. 또한 산업계와의 긴밀한 협력을 통해 삼성전자 견학과 인턴십, 공동 워크숍을 지원해 현장에 밀착한 교육을 제공할 예정이다.

KAIST는 국내 반도체 분야 박사 인력의 25%, 박사 출신 중견 및 벤처기업 CEO의 20%를 배출하며 한국 반도체 산업 생태계가 성장하는 데 중대한 공헌을 했다. 본격적으로 열린 AI 반도체 경쟁 체제를 앞두고 KAIST가 다시 산업 생태계의 구심점 역할을 할지 귀추가 주목된다.

2022.08.04 조회수 18972 무한대 화소 수준의 초고해상도 AR/VR 디스플레이 기술 개발

우리 대학 전기및전자공학부 김상현 교수 연구팀이 *모놀리식 3차원 집적의 장점을 활용한 1,600PPI*에 상응하는 마이크로LED 디스플레이를 구현하는 데 성공했다고 29일 밝혔다. 1,600 PPI는 초고해상도 증강현실(AR)/가상현실(VR) 디스플레이에 적용 가능한 해상도로써 2020년 출시된 오큘러스(Oculus) 社(現 메타(Meta))의 메타 퀘스트 2(Meta quest 2, 442 PPI)의 3.6배에 해당하는 디스플레이 해상도다.

☞ 모놀리식 3차원 집적: 하부 소자 공정 후, 상부의 박막층을 형성하고 상부 소자 공정을 순차적으로 진행함으로써 상하부 소자 간의 정렬도를 극대화할 수 있는 기술로 궁극적 3차원 집적 기술로 불린다.

☞ PPI: Pixel per Inch. 디스플레이에서 1인치에 포함되는 픽셀의 갯수

전기및전자공학부 박주혁 박사과정과 금대명 박사가 제1 저자로 주도하고 백우진 박사과정과 대만의 제스퍼 디스플레이(Jasper Display)의 존슨 쉬(Johnson Shieh) 박사와 협업으로 진행한 이번 연구는 반도체 올림픽이라 불리는 하와이 호놀롤루에서 열린 `VLSI 기술 & 회로 심포지엄 (2022 IEEE Symposium on VLSI Technology & Circuits)'에서 지난 6월 16일에 발표됐다. (논문명 : Monolithic 3D sequential integration realizing 1600-PPI red micro-LED display on Si CMOS driver IC)

VLSI 기술 심포지엄은 국제전자소자학회(International Electron Device Meetings, IEDM)와 더불어 대학 논문의 채택 비율이 25%가 되지 않는 저명한 반도체 소자 분야 최고 권위 학회다.

최근 디스플레이 분야는 각종 TV, 모니터 및 모바일 기기뿐만 아니라 스마트 워치, 스마트 글라스 등의 웨어러블 디바이스까지 그 응용처가 크게 확장됐다. 이처럼 디스플레이의 활용이 점차 다양화되고 고도화됨에 따라 요구되는 픽셀의 크기가 점점 작아지고 있는데, 특히 증강현실(AR)/가상현실(VR) 스마트 글라스 등과 같이 사람의 눈과 매우 가까운 거리를 유지하는 디스플레이의 경우 *픽셀화가 없는 완벽한 이미지의 구현을 위해서는 4K 이상의 고해상도가 요구된다.

☞ 픽셀화(Pixelation): 컴퓨터 그래픽에서 비트맵을 구성하는 작은 단색 정사각형 디스플레이 요소인 개별 픽셀이 보이는 현상.

앞서 언급한 초고해상도 디스플레이를 구현하기 위한 차세대 디스플레이 소자로서 무기물 기반의 인듐갈륨나이트라이드/갈륨나이트라이드(InGaN/GaN), 혹은 알루미늄 갈륨 인듐 인화물/갈륨 인듐 인화물(AlGaInP/GaInP)로 대표되는 3-5(III-V)족 화합물 반도체를 활용한 마이크로 LED 소자가 핵심 소재 및 부품으로써 주목받고 있다. 마이크로 LED는 현재 TV, 모바일 기기에 많이 사용되고 있는 OLED, LCD 디스플레이에 비해 높은 휘도와 명암비, 긴 픽셀 수명 등의 장점이 있어 차세대 디스플레이 소자로서 장점이 뚜렷하다.

☞ III-V 화합물 반도체: 주기율표 III족 원소와 V족 원소가 화합물을 이루고 있는 반도체로 전하 수송 특성 및 광 특성이 매우 우수한 소재.

하지만 무기물 기반 마이크로 LED를 활용해 디스플레이를 제작하기 위해서는 적색, 청색, 녹색의 각 색상의 픽셀을 각각의 기판에서 분리해 디스플레이 패널로 옮기는 패키징 작업이 필수적이다.

기존에 사용돼온 픽앤플레이스(Pick-and-place) 방법은 각각의 픽셀을 일일이 기계적으로 옮겨서 디스플레이 패널에 결합하는 방법으로 픽셀의 크기가 수십 마이크로미터 미만 수준으로 작아지게 되면 기계적인 정렬 정밀도가 저하되고 전사 수율이 감소해 초고해상도 디스플레이에는 적용이 어려울 것이라는 평가를 받고 있다.

연구팀은 이러한 문제의 해결을 위해 디스플레이 구동용 규소 상보적 금속산화물 반도체(이하 Si CMOS) 회로 기판 위에 적색 발광용 LED를 모놀리식 3차원 집적하는 방식을 적용했다. 위 방식은 Si CMOS 회로 위에 마이크로 LED 필름층을 먼저 웨이퍼 본딩을 통해 전사한 뒤, 포토리소그래피 공정으로 픽셀을 구현하는 방법으로, 기계적 픽셀 전사 공정이 제외된다. 이후 연구팀은 Si CMOS 회로상에서 상단에서 하단 방향으로(Top-down) 연속적인 반도체 공정 과정을 통해 고해상도 디스플레이 데모에 성공했다.

이 과정에서 연구팀은 조명용으로 활용돼왔던 무기물 기반 LED 반도체가 아닌 디스플레이용 LED 반도체층을 설계해 발광을 위한 활성층의 두께를 기존의 1/3로 감소시켜, 픽셀 형성에 필요한 식각 공정의 난도를 크게 낮추어 이번 연구성과를 얻어냈다.

또한, 연구팀은 하부 디스플레이 구동 회로의 성능 저하 방지를 위해 350oC 이하에서 상부 III-V 소자를 집적하는 웨이퍼 본딩 등의 초저온 공정을 활용해 상부 소자 집적 후에도 하부 드라이버 IC(Driver IC)의 성능을 그대로 유지할 수 있었다.

이번 연구 결과는 적색 마이크로 LED를 3차원 적층 방식으로 집적해 세계적인 수준의 해상도인 1,600 PPI 구현에 성공한 연구로서 연구에서 활용된 모놀리식 3차원 집적에 관한 연구 결과는 차세대 초고해상도 디스플레이 구현을 위한 좋은 가이드가 될 것으로 예상된다.

김상현 교수는 "향후 유사 공정을 확대 적용해 적색, 녹색, 청색이 모두 포함된 풀 컬러 디스플레이 제작도 가능할 것으로 생각한다ˮ라고 말했다.

한편 이번 연구는 삼성 미래기술육성센터의 지원을 받아 수행했다.

2022.07.29 조회수 11300

무한대 화소 수준의 초고해상도 AR/VR 디스플레이 기술 개발

우리 대학 전기및전자공학부 김상현 교수 연구팀이 *모놀리식 3차원 집적의 장점을 활용한 1,600PPI*에 상응하는 마이크로LED 디스플레이를 구현하는 데 성공했다고 29일 밝혔다. 1,600 PPI는 초고해상도 증강현실(AR)/가상현실(VR) 디스플레이에 적용 가능한 해상도로써 2020년 출시된 오큘러스(Oculus) 社(現 메타(Meta))의 메타 퀘스트 2(Meta quest 2, 442 PPI)의 3.6배에 해당하는 디스플레이 해상도다.

☞ 모놀리식 3차원 집적: 하부 소자 공정 후, 상부의 박막층을 형성하고 상부 소자 공정을 순차적으로 진행함으로써 상하부 소자 간의 정렬도를 극대화할 수 있는 기술로 궁극적 3차원 집적 기술로 불린다.

☞ PPI: Pixel per Inch. 디스플레이에서 1인치에 포함되는 픽셀의 갯수

전기및전자공학부 박주혁 박사과정과 금대명 박사가 제1 저자로 주도하고 백우진 박사과정과 대만의 제스퍼 디스플레이(Jasper Display)의 존슨 쉬(Johnson Shieh) 박사와 협업으로 진행한 이번 연구는 반도체 올림픽이라 불리는 하와이 호놀롤루에서 열린 `VLSI 기술 & 회로 심포지엄 (2022 IEEE Symposium on VLSI Technology & Circuits)'에서 지난 6월 16일에 발표됐다. (논문명 : Monolithic 3D sequential integration realizing 1600-PPI red micro-LED display on Si CMOS driver IC)

VLSI 기술 심포지엄은 국제전자소자학회(International Electron Device Meetings, IEDM)와 더불어 대학 논문의 채택 비율이 25%가 되지 않는 저명한 반도체 소자 분야 최고 권위 학회다.

최근 디스플레이 분야는 각종 TV, 모니터 및 모바일 기기뿐만 아니라 스마트 워치, 스마트 글라스 등의 웨어러블 디바이스까지 그 응용처가 크게 확장됐다. 이처럼 디스플레이의 활용이 점차 다양화되고 고도화됨에 따라 요구되는 픽셀의 크기가 점점 작아지고 있는데, 특히 증강현실(AR)/가상현실(VR) 스마트 글라스 등과 같이 사람의 눈과 매우 가까운 거리를 유지하는 디스플레이의 경우 *픽셀화가 없는 완벽한 이미지의 구현을 위해서는 4K 이상의 고해상도가 요구된다.

☞ 픽셀화(Pixelation): 컴퓨터 그래픽에서 비트맵을 구성하는 작은 단색 정사각형 디스플레이 요소인 개별 픽셀이 보이는 현상.

앞서 언급한 초고해상도 디스플레이를 구현하기 위한 차세대 디스플레이 소자로서 무기물 기반의 인듐갈륨나이트라이드/갈륨나이트라이드(InGaN/GaN), 혹은 알루미늄 갈륨 인듐 인화물/갈륨 인듐 인화물(AlGaInP/GaInP)로 대표되는 3-5(III-V)족 화합물 반도체를 활용한 마이크로 LED 소자가 핵심 소재 및 부품으로써 주목받고 있다. 마이크로 LED는 현재 TV, 모바일 기기에 많이 사용되고 있는 OLED, LCD 디스플레이에 비해 높은 휘도와 명암비, 긴 픽셀 수명 등의 장점이 있어 차세대 디스플레이 소자로서 장점이 뚜렷하다.

☞ III-V 화합물 반도체: 주기율표 III족 원소와 V족 원소가 화합물을 이루고 있는 반도체로 전하 수송 특성 및 광 특성이 매우 우수한 소재.

하지만 무기물 기반 마이크로 LED를 활용해 디스플레이를 제작하기 위해서는 적색, 청색, 녹색의 각 색상의 픽셀을 각각의 기판에서 분리해 디스플레이 패널로 옮기는 패키징 작업이 필수적이다.

기존에 사용돼온 픽앤플레이스(Pick-and-place) 방법은 각각의 픽셀을 일일이 기계적으로 옮겨서 디스플레이 패널에 결합하는 방법으로 픽셀의 크기가 수십 마이크로미터 미만 수준으로 작아지게 되면 기계적인 정렬 정밀도가 저하되고 전사 수율이 감소해 초고해상도 디스플레이에는 적용이 어려울 것이라는 평가를 받고 있다.

연구팀은 이러한 문제의 해결을 위해 디스플레이 구동용 규소 상보적 금속산화물 반도체(이하 Si CMOS) 회로 기판 위에 적색 발광용 LED를 모놀리식 3차원 집적하는 방식을 적용했다. 위 방식은 Si CMOS 회로 위에 마이크로 LED 필름층을 먼저 웨이퍼 본딩을 통해 전사한 뒤, 포토리소그래피 공정으로 픽셀을 구현하는 방법으로, 기계적 픽셀 전사 공정이 제외된다. 이후 연구팀은 Si CMOS 회로상에서 상단에서 하단 방향으로(Top-down) 연속적인 반도체 공정 과정을 통해 고해상도 디스플레이 데모에 성공했다.

이 과정에서 연구팀은 조명용으로 활용돼왔던 무기물 기반 LED 반도체가 아닌 디스플레이용 LED 반도체층을 설계해 발광을 위한 활성층의 두께를 기존의 1/3로 감소시켜, 픽셀 형성에 필요한 식각 공정의 난도를 크게 낮추어 이번 연구성과를 얻어냈다.

또한, 연구팀은 하부 디스플레이 구동 회로의 성능 저하 방지를 위해 350oC 이하에서 상부 III-V 소자를 집적하는 웨이퍼 본딩 등의 초저온 공정을 활용해 상부 소자 집적 후에도 하부 드라이버 IC(Driver IC)의 성능을 그대로 유지할 수 있었다.

이번 연구 결과는 적색 마이크로 LED를 3차원 적층 방식으로 집적해 세계적인 수준의 해상도인 1,600 PPI 구현에 성공한 연구로서 연구에서 활용된 모놀리식 3차원 집적에 관한 연구 결과는 차세대 초고해상도 디스플레이 구현을 위한 좋은 가이드가 될 것으로 예상된다.

김상현 교수는 "향후 유사 공정을 확대 적용해 적색, 녹색, 청색이 모두 포함된 풀 컬러 디스플레이 제작도 가능할 것으로 생각한다ˮ라고 말했다.

한편 이번 연구는 삼성 미래기술육성센터의 지원을 받아 수행했다.

2022.07.29 조회수 11300 양자컴퓨팅 한계를 극복하는 3차원 반도체 제어/해독 소자 집적 기술 개발

우리 대학 전기및전자공학부 김상현 교수 연구팀이 *모놀리식 3차원 집적의 장점을 활용해 기존 양자 컴퓨팅 시스템의 대규모 큐비트 구현의 한계를 극복하는 3차원 집적된 화합물 반도체 해독 소자 집적 기술을 개발했다고 24일 밝혔다. ‘모놀리식 3차원 집적 초고속 소자’ 연구 (2021년 VLSI 발표, 2021년 IEDM 발표, 2022년 ACS Nano 게재)를 활발하게 진행해 온 연구팀은 양자컴퓨터 판독/해독 소자를 3차원으로 집적할 수 있음을 처음으로 보였다.

☞ 모놀리식 3차원 집적: 반도체 하부 소자 공정 후, 상부의 박막층을 형성하고 상부 소자 공정을 순차적으로 진행함으로써 상하부 소자 간의 정렬도를 극대화할 수 있는 기술로 궁극적 3차원 반도체 집적 기술로 불린다.

우리 대학 전기및전자공학부 김상현 교수 연구팀의 정재용 박사과정이 제1 저자로 주도하고 한국나노기술원 김종민 박사, 한국기초과학지원연구원 박승영 박사 연구팀과의 협업으로 진행한 이번 연구는 반도체 올림픽이라 불리는 ‘VLSI 기술 심포지엄(Symposium on VLSI Technology)’에서 발표됐다. (논문명 : 3D stackable cryogenic InGaAs HEMTs for heterogeneous and monolithic 3D integrated highly scalable quantum computing system).

VLSI 기술 심포지엄은 국제전자소자학회(International Electron Device Meetings, IEDM)와 더불어 대학 논문의 채택 비율이 25%가 되지 않는 저명한 반도체 소자 분야 최고 권위 학회다.

양자컴퓨터는 큐비트 하나에 0과 1을 동시에 담아 여러 연산을 한 번에 처리할 수 있는 차세대 컴퓨터로, 최근에 IBM과 구글 등의 글로벌 기업이 양자 컴퓨터 제작에 성공하면서 양자 컴퓨터가 차세대 컴퓨터로 주목받고 있다.

기존 컴퓨터의 정보 단위인 `비트'의 경우 1 비트당 1개의 값만 가지는 것에 반해, 양자 컴퓨터의 정보 단위인 `큐비트'는 1 큐비트가 0과 1의 상태를 동시에 가진다. 따라서 비트에 비해 큐비트는 2배 빠른 계산이 가능하고, 2큐비트, 4큐비트, 8큐비트로 큐비트 수가 선형적으로 커질수록 처리 계산 속도는 4배, 8배, 16배로 지수적으로 증가한다. 따라서 많은 수의 큐비트를 활용한 대규모 양자컴퓨터 개발이 매우 중요하다. IBM에서는 큐비트 수를 127개로 늘린 `이글'을 작년에 발표했고, IBM 로드맵에 따르면 오는 2025년까지 4,000큐비트, 10년 이내에 10,000큐비트 이상을 탑재한 대규모 양자컴퓨터 개발을 목표로 하고 있다.

특히 큐비트의 수가 많은 대규모 양자컴퓨터 개발을 위해서는 큐비트를 제어/해독하는 소자에 대한 개발이 필수적이다. 기존 컴퓨터와 다르게 양자컴퓨터는 통상 –273 oC 내외의 극저온에서 동작하는 큐비트 하나당 최소 하나의 제어와 해독 연결이 필요하다. 현재는 큐비트 수가 많지 않아 극저온에서 동작하는 큐비트와 상온의 측정 장비를 긴 동축케이블로 연결해 제어/해독하는 방식을 사용하고 있다.

하지만 수천 혹은 수만 개 이상의 큐비트를 활용하는 대규모 양자 컴퓨팅에서 이러한 방식을 활용하면 양자 컴퓨터 크기가 매우 커지고 긴 연결 거리로 인해 신호 손실도 커 대규모 양자컴퓨터 구현이 매우 어려워진다. 따라서 큐비트를 제어/해독에 활용할 수 있는 저전력, 저잡음, 초고속 특성의 극저온 소자를 큐비트와 일대일로 연결할 수 있는 시스템 구성이 매우 중요하다.

연구팀은 이러한 문제 해결을 위해 큐비트 회로 위에 저전력, 저잡음 초고속 특성이 매우 뛰어난 *III-V 화합물 반도체 *고전자 이동 트랜지스터(HEMT)를 3차원으로 집적해 수천 혹은 수만 개의 큐비트에 아주 짧은 거리에서 일대일로 연결 가능한 구조를 제시했다.

☞ III-V 화합물 반도체: 주기율표 III족 원소와 V족 원소가 화합물을 이루고 있는 반도체로 전하 수송 특성 및 광 특성이 매우 우수한 소재.

☞ HEMT: High-Electron Mobility Transistor

연구팀은 250oC 이하에서 상부 제어/해독 소자를 집적하는 웨이퍼 본딩 등의 초저온 공정을 활용해 이후 하부 큐비트 회로의 성능 저하 없이 3차원 집적을 할 수 있도록 했다.

연구진은 이러한 3차원 집적 형태의 제어/해독 소자를 최초로 제시 및 구현했을 뿐만 아니라 소자의 성능 면에서도 극저온에서 세계 최고 수준의 차단주파수 특성을 달성했다.

김상현 교수는 "이번 기술은 향후 대규모 양자컴퓨터의 제어/판독 회로에 응용이 가능할 것으로 생각한다ˮ라며 "모놀리식 3차원 초고속 소자의 경우 양자컴퓨터뿐만이 아니라 6G 무선통신 등 다양한 분야에서 응용할 수 있어 그 확장성이 매우 큰 기술이며 앞으로도 다양한 분야에서 활용할 수 있도록 후속 연구에 힘쓰겠다ˮ라고 말했다.

한편 이번 연구는 한국연구재단 지능형반도체기술개발사업, 경기도 시스템반도체 국산화 연구지원 사업, 한국기초과학지원연구원 분석과학연구장비개발사업(BIG사업) 등의 지원을 받아 수행됐다.

2022.06.24 조회수 11067

양자컴퓨팅 한계를 극복하는 3차원 반도체 제어/해독 소자 집적 기술 개발

우리 대학 전기및전자공학부 김상현 교수 연구팀이 *모놀리식 3차원 집적의 장점을 활용해 기존 양자 컴퓨팅 시스템의 대규모 큐비트 구현의 한계를 극복하는 3차원 집적된 화합물 반도체 해독 소자 집적 기술을 개발했다고 24일 밝혔다. ‘모놀리식 3차원 집적 초고속 소자’ 연구 (2021년 VLSI 발표, 2021년 IEDM 발표, 2022년 ACS Nano 게재)를 활발하게 진행해 온 연구팀은 양자컴퓨터 판독/해독 소자를 3차원으로 집적할 수 있음을 처음으로 보였다.

☞ 모놀리식 3차원 집적: 반도체 하부 소자 공정 후, 상부의 박막층을 형성하고 상부 소자 공정을 순차적으로 진행함으로써 상하부 소자 간의 정렬도를 극대화할 수 있는 기술로 궁극적 3차원 반도체 집적 기술로 불린다.

우리 대학 전기및전자공학부 김상현 교수 연구팀의 정재용 박사과정이 제1 저자로 주도하고 한국나노기술원 김종민 박사, 한국기초과학지원연구원 박승영 박사 연구팀과의 협업으로 진행한 이번 연구는 반도체 올림픽이라 불리는 ‘VLSI 기술 심포지엄(Symposium on VLSI Technology)’에서 발표됐다. (논문명 : 3D stackable cryogenic InGaAs HEMTs for heterogeneous and monolithic 3D integrated highly scalable quantum computing system).

VLSI 기술 심포지엄은 국제전자소자학회(International Electron Device Meetings, IEDM)와 더불어 대학 논문의 채택 비율이 25%가 되지 않는 저명한 반도체 소자 분야 최고 권위 학회다.

양자컴퓨터는 큐비트 하나에 0과 1을 동시에 담아 여러 연산을 한 번에 처리할 수 있는 차세대 컴퓨터로, 최근에 IBM과 구글 등의 글로벌 기업이 양자 컴퓨터 제작에 성공하면서 양자 컴퓨터가 차세대 컴퓨터로 주목받고 있다.

기존 컴퓨터의 정보 단위인 `비트'의 경우 1 비트당 1개의 값만 가지는 것에 반해, 양자 컴퓨터의 정보 단위인 `큐비트'는 1 큐비트가 0과 1의 상태를 동시에 가진다. 따라서 비트에 비해 큐비트는 2배 빠른 계산이 가능하고, 2큐비트, 4큐비트, 8큐비트로 큐비트 수가 선형적으로 커질수록 처리 계산 속도는 4배, 8배, 16배로 지수적으로 증가한다. 따라서 많은 수의 큐비트를 활용한 대규모 양자컴퓨터 개발이 매우 중요하다. IBM에서는 큐비트 수를 127개로 늘린 `이글'을 작년에 발표했고, IBM 로드맵에 따르면 오는 2025년까지 4,000큐비트, 10년 이내에 10,000큐비트 이상을 탑재한 대규모 양자컴퓨터 개발을 목표로 하고 있다.

특히 큐비트의 수가 많은 대규모 양자컴퓨터 개발을 위해서는 큐비트를 제어/해독하는 소자에 대한 개발이 필수적이다. 기존 컴퓨터와 다르게 양자컴퓨터는 통상 –273 oC 내외의 극저온에서 동작하는 큐비트 하나당 최소 하나의 제어와 해독 연결이 필요하다. 현재는 큐비트 수가 많지 않아 극저온에서 동작하는 큐비트와 상온의 측정 장비를 긴 동축케이블로 연결해 제어/해독하는 방식을 사용하고 있다.

하지만 수천 혹은 수만 개 이상의 큐비트를 활용하는 대규모 양자 컴퓨팅에서 이러한 방식을 활용하면 양자 컴퓨터 크기가 매우 커지고 긴 연결 거리로 인해 신호 손실도 커 대규모 양자컴퓨터 구현이 매우 어려워진다. 따라서 큐비트를 제어/해독에 활용할 수 있는 저전력, 저잡음, 초고속 특성의 극저온 소자를 큐비트와 일대일로 연결할 수 있는 시스템 구성이 매우 중요하다.

연구팀은 이러한 문제 해결을 위해 큐비트 회로 위에 저전력, 저잡음 초고속 특성이 매우 뛰어난 *III-V 화합물 반도체 *고전자 이동 트랜지스터(HEMT)를 3차원으로 집적해 수천 혹은 수만 개의 큐비트에 아주 짧은 거리에서 일대일로 연결 가능한 구조를 제시했다.

☞ III-V 화합물 반도체: 주기율표 III족 원소와 V족 원소가 화합물을 이루고 있는 반도체로 전하 수송 특성 및 광 특성이 매우 우수한 소재.

☞ HEMT: High-Electron Mobility Transistor

연구팀은 250oC 이하에서 상부 제어/해독 소자를 집적하는 웨이퍼 본딩 등의 초저온 공정을 활용해 이후 하부 큐비트 회로의 성능 저하 없이 3차원 집적을 할 수 있도록 했다.

연구진은 이러한 3차원 집적 형태의 제어/해독 소자를 최초로 제시 및 구현했을 뿐만 아니라 소자의 성능 면에서도 극저온에서 세계 최고 수준의 차단주파수 특성을 달성했다.

김상현 교수는 "이번 기술은 향후 대규모 양자컴퓨터의 제어/판독 회로에 응용이 가능할 것으로 생각한다ˮ라며 "모놀리식 3차원 초고속 소자의 경우 양자컴퓨터뿐만이 아니라 6G 무선통신 등 다양한 분야에서 응용할 수 있어 그 확장성이 매우 큰 기술이며 앞으로도 다양한 분야에서 활용할 수 있도록 후속 연구에 힘쓰겠다ˮ라고 말했다.

한편 이번 연구는 한국연구재단 지능형반도체기술개발사업, 경기도 시스템반도체 국산화 연구지원 사업, 한국기초과학지원연구원 분석과학연구장비개발사업(BIG사업) 등의 지원을 받아 수행됐다.

2022.06.24 조회수 11067 3차원 적층형 화합물 반도체 소자 제작 성공

우리 대학 전기및전자공학부 김상현 교수 연구팀이 *모놀리식 3차원 집적의 장점을 극대화해 기존의 통신 소자의 단점을 극복하는 화합물 반도체 소자 집적 기술을 개발했다고 14일 밝혔다.

☞ 모놀리식 3차원 집적: 하부 소자 공정 후, 상부의 박막층을 형성하고 상부 소자 공정을 순차적으로 진행함으로써 상하부 소자 간의 정렬도를 극대화할 수 있는 기술로 궁극적 3차원 집적 기술로 불린다.

우리 대학 전기및전자공학부 정재용 박사과정이 제1 저자로 주도하고 한국나노기술원 김종민 박사, 광주과학기술원 장재형 교수 연구팀과의 협업으로 진행한 이번 연구는 반도체 올림픽이라 불리는 ‘VLSI 기술 심포지엄(Symposium on VLSI Technology)’에서 발표됐다. (논문명 : High-performance InGaAs-On-Insulator HEMTs on Si CMOS for Substrate Coupling Noise-free Monolithic 3D Mixed-Signal IC).

VLSI 기술 심포지엄은 국제전자소자학회(International Electron Device Meetings, IEDM)와 더불어 대학 논문의 채택비율이 25%가 되지 않는 저명한 반도체 소자 분야 최고 권위 학회다.

반도체 소자는 4차 산업 혁명의 특징인 초연결성 구현을 위한 핵심 통신 소재 및 부품으로서 주목받고 있다.

특히 통신 신호, 양자 신호는 아날로그 형태의 신호이고 신호전달 과정에서 신호의 크기가 약해지거나 잡음이 생겨 신호의 왜곡이 생기기도 한다. 따라서 이러한 신호를 주고받을 때 고속으로 신호의 증폭이 필요한데 이러한 증폭 소자에서는 초고속, 고출력, 저전력, 저잡음 등의 특성이 매우 중요하다. 또한 통신 기술이 발전함에 따라 이를 구성하는 시스템은 점점 더 복잡해져 고집적 소자 제작기술이 매우 중요하다.

통신 소자는 통상적으로 두 가지 방식으로 구현된다. 실리콘(Si)을 사용해 집적도 높은 Si CMOS를 이용해 증폭 소자를 구현하는 방법과 *III-V 화합물 반도체를 증폭 소자로 제작하고 기타 소자들을 Si CMOS로 제작해 패키징 하는 방식이 있다. 그러나 각각의 방식은 단점이 존재한다. 기존의 실리콘(Si) 기술은 물성적 한계로 인해 차단주파수 특성 등 통신 소자에 중요한 소자 성능 향상이 어려우며 기판 커플링 잡음 등 복잡한 신호 간섭에 의한 잡음 증가 문제가 존재한다. 반면, III-V 화합물 반도체 기술은 소자 자체의 잡음 특성은 우수하지만 다른 부품과의 집적/패키징 공정이 복잡하고 이러한 패키징 공정으로 인해 신호의 손실이 발생하는 문제가 존재한다.

☞ III-V 화합물 반도체: 주기율표 III족 원소와 V족 원소가 화합물을 이루고 있는 반도체로 전하 수송 특성 및 광 특성이 매우 우수한 소재

연구팀은 이러한 문제 해결을 위해 증폭 소자 이외의 소자 및 디지털 회로에서 좋은 성능을 낼 수 있는 Si CMOS 기판 위에 아날로그 신호 증폭 성능이 매우 우수한 III-V 화합물 반도체 *HEMT를 3차원 집적해 Si CMOS와 III-V HEMT의 장점을 극대화하는 공정 및 소자 구조를 제시했다. 3층으로 소자를 쌓아나감으로써 같은 기판 위에 집적할 수 있는 방식이다. 이와 동시에 기판 신호 간섭에 의한 잡음을 제거할 수 있음을 증명했다.

☞ HEMT: High-Electron Mobility Transistor

연구팀은 하부 Si CMOS의 성능 저하 방지를 위해 300oC 이하에서 상부 III-V 소자를 집적하는 웨이퍼 본딩 등의 초저온 공정을 활용해 상부 소자 집적 후에도 하부 Si CMOS의 성능을 그대로 유지할 수 있었다.

또한 고성능 상부 III-V 소자 제작을 위해서 InGaAs/InAs/InGaAs의 양자우물 구조를 도입해 높은 전자 수송 특성을 실현했으며 100 나노미터(nm) 노드 공정 수준으로도 세계 최고 수준의 차단 주파수 특성을 달성했다. 이는 10 나노미터(nm) 이하 급의 최첨단 공정을 사용하지 않고도 그 이상의 우수한 성능을 낼 수 있는 융합 기술로 향후 기존과 다른 형태의 파운드리 비즈니스 방식의 도입 가능성을 증명했다고 할 수 있다.

더불어 연구진은 이러한 3차원 집적 형태로 소자를 제작함으로써 기존에 SI CMOS에서 존재하는 기판 간섭에 의한 잡음을 해결할 수 있음을 실험을 통해 최초로 증명했다.

김상현 교수는 “디지털 회로 및 다양한 수동소자 제작에 최적화된 Si CMOS 기판 위에 증폭기 등의 능동소자 특성이 현존하는 어떤 물질보다 우수한 III-V 화합물 반도체 소자를 동시 집적할 가능성을 최초로 입증한 연구로, 향후 통신 소자 등에 응용이 가능할 것으로 생각한다”라며 “이번 기술은 향후 양자 큐빗의 해독 회로에도 응용할 수 있어 그 확장성이 매우 큰 기술이다. 다양한 분야에서 활용할 수 있도록 후속 연구에 힘쓰겠다”라고 말했다.

한편 이번 연구는 한국연구재단 지능형반도체기술개발사업, 경기도 시스템반도체 국산화 연구지원 사업 등의 지원을 받아 수행됐다.

2021.06.14 조회수 55072

3차원 적층형 화합물 반도체 소자 제작 성공

우리 대학 전기및전자공학부 김상현 교수 연구팀이 *모놀리식 3차원 집적의 장점을 극대화해 기존의 통신 소자의 단점을 극복하는 화합물 반도체 소자 집적 기술을 개발했다고 14일 밝혔다.

☞ 모놀리식 3차원 집적: 하부 소자 공정 후, 상부의 박막층을 형성하고 상부 소자 공정을 순차적으로 진행함으로써 상하부 소자 간의 정렬도를 극대화할 수 있는 기술로 궁극적 3차원 집적 기술로 불린다.

우리 대학 전기및전자공학부 정재용 박사과정이 제1 저자로 주도하고 한국나노기술원 김종민 박사, 광주과학기술원 장재형 교수 연구팀과의 협업으로 진행한 이번 연구는 반도체 올림픽이라 불리는 ‘VLSI 기술 심포지엄(Symposium on VLSI Technology)’에서 발표됐다. (논문명 : High-performance InGaAs-On-Insulator HEMTs on Si CMOS for Substrate Coupling Noise-free Monolithic 3D Mixed-Signal IC).

VLSI 기술 심포지엄은 국제전자소자학회(International Electron Device Meetings, IEDM)와 더불어 대학 논문의 채택비율이 25%가 되지 않는 저명한 반도체 소자 분야 최고 권위 학회다.

반도체 소자는 4차 산업 혁명의 특징인 초연결성 구현을 위한 핵심 통신 소재 및 부품으로서 주목받고 있다.

특히 통신 신호, 양자 신호는 아날로그 형태의 신호이고 신호전달 과정에서 신호의 크기가 약해지거나 잡음이 생겨 신호의 왜곡이 생기기도 한다. 따라서 이러한 신호를 주고받을 때 고속으로 신호의 증폭이 필요한데 이러한 증폭 소자에서는 초고속, 고출력, 저전력, 저잡음 등의 특성이 매우 중요하다. 또한 통신 기술이 발전함에 따라 이를 구성하는 시스템은 점점 더 복잡해져 고집적 소자 제작기술이 매우 중요하다.

통신 소자는 통상적으로 두 가지 방식으로 구현된다. 실리콘(Si)을 사용해 집적도 높은 Si CMOS를 이용해 증폭 소자를 구현하는 방법과 *III-V 화합물 반도체를 증폭 소자로 제작하고 기타 소자들을 Si CMOS로 제작해 패키징 하는 방식이 있다. 그러나 각각의 방식은 단점이 존재한다. 기존의 실리콘(Si) 기술은 물성적 한계로 인해 차단주파수 특성 등 통신 소자에 중요한 소자 성능 향상이 어려우며 기판 커플링 잡음 등 복잡한 신호 간섭에 의한 잡음 증가 문제가 존재한다. 반면, III-V 화합물 반도체 기술은 소자 자체의 잡음 특성은 우수하지만 다른 부품과의 집적/패키징 공정이 복잡하고 이러한 패키징 공정으로 인해 신호의 손실이 발생하는 문제가 존재한다.

☞ III-V 화합물 반도체: 주기율표 III족 원소와 V족 원소가 화합물을 이루고 있는 반도체로 전하 수송 특성 및 광 특성이 매우 우수한 소재

연구팀은 이러한 문제 해결을 위해 증폭 소자 이외의 소자 및 디지털 회로에서 좋은 성능을 낼 수 있는 Si CMOS 기판 위에 아날로그 신호 증폭 성능이 매우 우수한 III-V 화합물 반도체 *HEMT를 3차원 집적해 Si CMOS와 III-V HEMT의 장점을 극대화하는 공정 및 소자 구조를 제시했다. 3층으로 소자를 쌓아나감으로써 같은 기판 위에 집적할 수 있는 방식이다. 이와 동시에 기판 신호 간섭에 의한 잡음을 제거할 수 있음을 증명했다.

☞ HEMT: High-Electron Mobility Transistor

연구팀은 하부 Si CMOS의 성능 저하 방지를 위해 300oC 이하에서 상부 III-V 소자를 집적하는 웨이퍼 본딩 등의 초저온 공정을 활용해 상부 소자 집적 후에도 하부 Si CMOS의 성능을 그대로 유지할 수 있었다.

또한 고성능 상부 III-V 소자 제작을 위해서 InGaAs/InAs/InGaAs의 양자우물 구조를 도입해 높은 전자 수송 특성을 실현했으며 100 나노미터(nm) 노드 공정 수준으로도 세계 최고 수준의 차단 주파수 특성을 달성했다. 이는 10 나노미터(nm) 이하 급의 최첨단 공정을 사용하지 않고도 그 이상의 우수한 성능을 낼 수 있는 융합 기술로 향후 기존과 다른 형태의 파운드리 비즈니스 방식의 도입 가능성을 증명했다고 할 수 있다.

더불어 연구진은 이러한 3차원 집적 형태로 소자를 제작함으로써 기존에 SI CMOS에서 존재하는 기판 간섭에 의한 잡음을 해결할 수 있음을 실험을 통해 최초로 증명했다.

김상현 교수는 “디지털 회로 및 다양한 수동소자 제작에 최적화된 Si CMOS 기판 위에 증폭기 등의 능동소자 특성이 현존하는 어떤 물질보다 우수한 III-V 화합물 반도체 소자를 동시 집적할 가능성을 최초로 입증한 연구로, 향후 통신 소자 등에 응용이 가능할 것으로 생각한다”라며 “이번 기술은 향후 양자 큐빗의 해독 회로에도 응용할 수 있어 그 확장성이 매우 큰 기술이다. 다양한 분야에서 활용할 수 있도록 후속 연구에 힘쓰겠다”라고 말했다.

한편 이번 연구는 한국연구재단 지능형반도체기술개발사업, 경기도 시스템반도체 국산화 연구지원 사업 등의 지원을 받아 수행됐다.

2021.06.14 조회수 55072