%EB%B0%98%EB%8F%84%EC%B2%B4

-

차세대 반도체 솔리톤 안정화 기술 최초 개발

초고속 초저전력 차세대 반도체 기술을 구현할 스핀트로닉스 기술을 한 단계 성장시키는 원동력으로 위상적 솔리톤이라는 구조체를 이용해 정보를 저장하고 전송할 수 있는 초고속 비휘발성 메모리 소자 기술이 개발되었다.

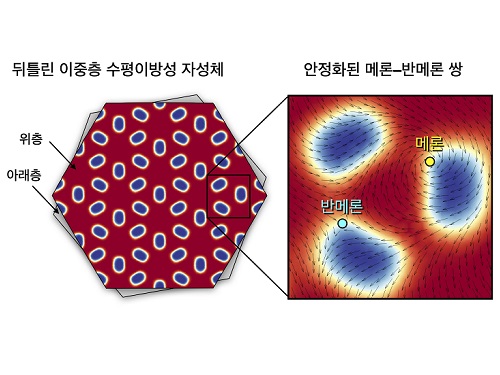

우리 대학 물리학과 김세권 교수 연구팀이 기초과학연구원 복잡계 이론물리 연구단(PCS-IBS) 김경민 박사팀, 한양대학교 물리학과 박문집 교수팀과의 공동 연구로 뒤틀림 자성체*를 이용해 위상적 솔리톤을 안정화시킬 수 있는 기술을 세계 최초로 개발해 물리 및 화학 분야 세계적인 학술지 `나노 레터스(Nano Letters)'에 게재했다고 20일 밝혔다.

*자성체: 자성을 띄는 여러 물체를 통칭함

스핀트로닉스는 성장 한계에 다다른 기존 반도체 기술의 근본적인 문제점들을 전자의 양자적 성질인 스핀을 이용해 해결하고자 하는 연구 분야다. 이는 기존 정보처리 기술을 혁신적으로 발전시켜 초고속 초저전력 차세대 반도체 기술을 구현할 것으로 기대되고 있다.

한편 솔리톤이란 특정한 구조가 주변과 상호작용을 통해 사라지지 않고 계속 유지하는 현상을 말하며, 위상적 솔리톤이라는 구조체를 이용해 정보를 저장하고 전송할 수 있는 초고속 비휘발성 메모리 소자 개발이 전 세계 각국 학계와 산업계에서 경쟁적으로 연구가 이뤄지고 있다.

이전까지 차세대 메모리 소자 개발을 위해 연구됐던 위상적 솔리톤으로는 스핀 구조체로 자연계에 존재하는 다양한 자성체 중 수직 이방성*이라고 하는 특수한 성질을 갖는 자성체에서만 안정하다고 알려져, 물질 선택의 제한으로 인해 솔리톤 기반 정보처리 기술 발전에 어려움이 있었다.

* 수직 이방성: 자화 방향이 자성체에 수직한 방향을 선호하게 되는 성질

김세권 교수 연구팀은 특정 단층 강자성체* 두 겹을 서로 뒤틀어 접합시켜 이중층 자성체를 구성할 경우, 수직 이방성을 띠지 않는 다른 종류의 자성체에서도 위상적 솔리톤을 안정화시킬 수 있음을 세계 최초로 발견했다.

*강자성체: 자성체 중에서도 상온의 철과 같이 자발적 자화를 띄는 물체를 뜻함

이번 연구를 통해 발견된 안정한 위상적 솔리톤은 수직이방성이 아닌 수평 이방성을 띄는 자성체에 존재하는 ‘메론’이라고 불리는 스핀 구조체로서 이전에는 그 안정화 메커니즘이 알려지지 않았던 솔리톤이다. 메론 안정화 기술의 확보로 지금까지 수직 이방성 자성체에만 국한되어 있었던 솔리톤 기반 차세대 반도체 기술 연구를 다양한 자성체로 확대 발전시킬 수 있을 것으로 기대되며, 스핀트로닉스 기술을 한 단계 성장시키는 원동력으로 작용할 것으로 예상된다.

이번 연구 결과는 자성체 내부에서는 안정하지 않은 위상적 솔리톤이 두 자성체를 뒤틀어 접합할 경우, 자성체 간 상호작용을 통해 안정화될 수 있다는 것을 보인 첫 예시다. 여러 자성체를 뒤틀어 접합시키는 경우 자성체의 종류와 뒤틀림 각도를 조절함으로써 무한히 많은 자성 시스템을 구현할 수 있으므로, 이번 연구 결과는 뒤틀림 자성체 기반 스핀 기술이라고 하는 넓은 연구 영역을 새로이 개척했다고 판단된다.

우리 대학 김세권 교수는 "이번 논문은 무한히 많은 가능성을 갖는 뒤틀림 자성체 기반의 새로운 물리 현상 탐색과 활용 연구의 시발점으로 작용할 것ˮ이라고 기대감을 내비쳤다.

이번 연구는 우리 대학 김세권 교수, 우리 대학 고경춘 박사, 그리고 PCS-IBS 김경민 박사, 한양대학교 박문집 교수의 공동 연구로 진행되었으며, 한국연구재단 해외우수과학자 유치사업 플러스(브레인 풀 플러스)의 지원을 받아 수행됐다.

2024.02.20 조회수 6882

차세대 반도체 솔리톤 안정화 기술 최초 개발

초고속 초저전력 차세대 반도체 기술을 구현할 스핀트로닉스 기술을 한 단계 성장시키는 원동력으로 위상적 솔리톤이라는 구조체를 이용해 정보를 저장하고 전송할 수 있는 초고속 비휘발성 메모리 소자 기술이 개발되었다.

우리 대학 물리학과 김세권 교수 연구팀이 기초과학연구원 복잡계 이론물리 연구단(PCS-IBS) 김경민 박사팀, 한양대학교 물리학과 박문집 교수팀과의 공동 연구로 뒤틀림 자성체*를 이용해 위상적 솔리톤을 안정화시킬 수 있는 기술을 세계 최초로 개발해 물리 및 화학 분야 세계적인 학술지 `나노 레터스(Nano Letters)'에 게재했다고 20일 밝혔다.

*자성체: 자성을 띄는 여러 물체를 통칭함

스핀트로닉스는 성장 한계에 다다른 기존 반도체 기술의 근본적인 문제점들을 전자의 양자적 성질인 스핀을 이용해 해결하고자 하는 연구 분야다. 이는 기존 정보처리 기술을 혁신적으로 발전시켜 초고속 초저전력 차세대 반도체 기술을 구현할 것으로 기대되고 있다.

한편 솔리톤이란 특정한 구조가 주변과 상호작용을 통해 사라지지 않고 계속 유지하는 현상을 말하며, 위상적 솔리톤이라는 구조체를 이용해 정보를 저장하고 전송할 수 있는 초고속 비휘발성 메모리 소자 개발이 전 세계 각국 학계와 산업계에서 경쟁적으로 연구가 이뤄지고 있다.

이전까지 차세대 메모리 소자 개발을 위해 연구됐던 위상적 솔리톤으로는 스핀 구조체로 자연계에 존재하는 다양한 자성체 중 수직 이방성*이라고 하는 특수한 성질을 갖는 자성체에서만 안정하다고 알려져, 물질 선택의 제한으로 인해 솔리톤 기반 정보처리 기술 발전에 어려움이 있었다.

* 수직 이방성: 자화 방향이 자성체에 수직한 방향을 선호하게 되는 성질

김세권 교수 연구팀은 특정 단층 강자성체* 두 겹을 서로 뒤틀어 접합시켜 이중층 자성체를 구성할 경우, 수직 이방성을 띠지 않는 다른 종류의 자성체에서도 위상적 솔리톤을 안정화시킬 수 있음을 세계 최초로 발견했다.

*강자성체: 자성체 중에서도 상온의 철과 같이 자발적 자화를 띄는 물체를 뜻함

이번 연구를 통해 발견된 안정한 위상적 솔리톤은 수직이방성이 아닌 수평 이방성을 띄는 자성체에 존재하는 ‘메론’이라고 불리는 스핀 구조체로서 이전에는 그 안정화 메커니즘이 알려지지 않았던 솔리톤이다. 메론 안정화 기술의 확보로 지금까지 수직 이방성 자성체에만 국한되어 있었던 솔리톤 기반 차세대 반도체 기술 연구를 다양한 자성체로 확대 발전시킬 수 있을 것으로 기대되며, 스핀트로닉스 기술을 한 단계 성장시키는 원동력으로 작용할 것으로 예상된다.

이번 연구 결과는 자성체 내부에서는 안정하지 않은 위상적 솔리톤이 두 자성체를 뒤틀어 접합할 경우, 자성체 간 상호작용을 통해 안정화될 수 있다는 것을 보인 첫 예시다. 여러 자성체를 뒤틀어 접합시키는 경우 자성체의 종류와 뒤틀림 각도를 조절함으로써 무한히 많은 자성 시스템을 구현할 수 있으므로, 이번 연구 결과는 뒤틀림 자성체 기반 스핀 기술이라고 하는 넓은 연구 영역을 새로이 개척했다고 판단된다.

우리 대학 김세권 교수는 "이번 논문은 무한히 많은 가능성을 갖는 뒤틀림 자성체 기반의 새로운 물리 현상 탐색과 활용 연구의 시발점으로 작용할 것ˮ이라고 기대감을 내비쳤다.

이번 연구는 우리 대학 김세권 교수, 우리 대학 고경춘 박사, 그리고 PCS-IBS 김경민 박사, 한양대학교 박문집 교수의 공동 연구로 진행되었으며, 한국연구재단 해외우수과학자 유치사업 플러스(브레인 풀 플러스)의 지원을 받아 수행됐다.

2024.02.20 조회수 6882 -

반도체가 곤충처럼 사물 움직임 감지한다

곤충의 시신경계를 모방하여 초고속, 저전력 동작이 가능한 신개념 ‘지능형 센서’ 반도체의 개발로 다양한 혁신적 기술로 확장가능한 기술이 개발되었다. 이 기술은 교통, 안전, 보안 시스템 등 다양한 분야에 응용되어 산업과 사회에 기여할 것으로 보인다.

우리 대학 신소재공학과 김경민 교수 연구팀이 다양한 멤리스터* 소자를 융합해 곤충의 시신경에서의 시각 지능*을 모사하는 지능형 동작인식 소자를 개발하는데 성공했다고 19일 밝혔다.

*멤리스터 (Memristor): 메모리(Memory)와 저항(Resistor)의 합성어로, 입력 신호에 따라 소자의 저항 상태가 변하는 전자소자.

*시각 지능 (Visual Intelligence): 시신경 내에서 시각 정보를 해석하고 연산을 수행하는 기능.

최근 인공지능(AI) 기술의 발전과 함께, 비전 시스템은 이미지 인식, 객체 탐지 및 동작 분석과 같은 다양한 작업에서 AI를 활용해 핵심적인 역할을 수행하고 있다. 하지만 기존 비전 시스템은 이미지 센서에서 수신된 신호를 복잡한 알고리즘을 이용해 물체와 그 동작을 인식하는 것이 일반적이다. 이러한 방식은 상당한 양의 데이터 트래픽과 높은 전력 소모가 필요하여 모바일 또는 사물인터넷 장치에 적용되기 어렵다.

한편, 곤충은 기본 동작 감지기(Elementary Motion Detector) 라는 시신경 회로를 통해 시각 정보를 효과적으로 처리해 물체를 탐지하고 그 동작을 인식하는데 탁월한 능력을 보인다. <그림1> 이를 구현하는 데 있어 기존 실리콘 집적회로(CMOS) 기술에서는 복잡한 회로가 요구되기 때문에, 실제 소자로 제작하기 어려운 한계가 있었다.

김경민 교수 연구팀은 다양한 기능의 멤리스터 소자들을 집적하여 고효율⋅초고속 동작 인식이 가능한 지능형 동작인식 소자를 개발했다. 동작인식 소자는 자체 개발한 두 종류의 멤리스터 소자와 저항 만으로 구성된 단순한 구조를 가지고 있다. 두 종류의 서로 다른 멤리스터는 각각 신호 지연 기능과 신호 통합 및 발화 기능을 수행하며, 이를 통해 곤충의 시신경을 직접 모사하여 사물의 움직임을 판단할 수 있음을 확인했다. <그림2>

연구팀은 개발된 동작인식 소자의 실질적인 활용에 대한 가능성을 입증하기 위해 차량 경로를 예측하는 뉴로모픽 컴퓨팅 시스템을 설계하였으며, 여기에 개발한 동작인식 소자를 적용하였다. <그림3> 그 결과 기존 기술 대비 에너지 소비를 92.9 % 감소하여 더 정확히 사물의 움직임을 예측할 수 있음을 검증하였다.

신소재공학과 김경민 교수는 “곤충은 매우 간단한 시각 지능을 활용해 놀랍도록 민첩하게 물체의 동작을 인지하는데, 이번 연구는 신경의 기능을 재현할 수 있는 멤리스터 소자를 활용해 이를 구현할 수 있었다는 점에 큰 의의가 있다”며, “최근 AI가 탑재된 휴대폰과 같이 에지(edge)형 인공지능 소자의 중요성이 매우 커지고 있는데, 이 연구는 동작 인식을 위한 효율적인 비전 시스템 구현에 기여할 수 있어, 향후 자율주행 자동차, 차량 운송 시스템, 로봇, 머신 비전 등과 같은 다양한 분야에 적용될 수 있을 것으로 기대된다”고 밝혔다.

이번 연구는 신소재공학과 송한찬 박사과정, 이민구 박사과정 학생이 공동 제1 저자로 참여했으며, 국제 학술지 ‘어드밴스드 머티리얼즈(Advanced Materials, IF: 29.4)’에 지난 1월 29일 字 온라인 게재됐다.

한편 이번 연구는 한국연구재단 중견연구사업, 차세대지능형반도체기술개발사업, PIM인공지능반도체핵심기술개발사업, 나노종합기술원 및 KAIST 도약연구사업의 지원을 받아 수행됐다. (논문명: Fully Memristive Elementary Motion Detectors for A Maneuver Prediction, 논문링크: https://doi.org/10.1002/adma.202309708)

2024.02.19 조회수 7660

반도체가 곤충처럼 사물 움직임 감지한다

곤충의 시신경계를 모방하여 초고속, 저전력 동작이 가능한 신개념 ‘지능형 센서’ 반도체의 개발로 다양한 혁신적 기술로 확장가능한 기술이 개발되었다. 이 기술은 교통, 안전, 보안 시스템 등 다양한 분야에 응용되어 산업과 사회에 기여할 것으로 보인다.

우리 대학 신소재공학과 김경민 교수 연구팀이 다양한 멤리스터* 소자를 융합해 곤충의 시신경에서의 시각 지능*을 모사하는 지능형 동작인식 소자를 개발하는데 성공했다고 19일 밝혔다.

*멤리스터 (Memristor): 메모리(Memory)와 저항(Resistor)의 합성어로, 입력 신호에 따라 소자의 저항 상태가 변하는 전자소자.

*시각 지능 (Visual Intelligence): 시신경 내에서 시각 정보를 해석하고 연산을 수행하는 기능.

최근 인공지능(AI) 기술의 발전과 함께, 비전 시스템은 이미지 인식, 객체 탐지 및 동작 분석과 같은 다양한 작업에서 AI를 활용해 핵심적인 역할을 수행하고 있다. 하지만 기존 비전 시스템은 이미지 센서에서 수신된 신호를 복잡한 알고리즘을 이용해 물체와 그 동작을 인식하는 것이 일반적이다. 이러한 방식은 상당한 양의 데이터 트래픽과 높은 전력 소모가 필요하여 모바일 또는 사물인터넷 장치에 적용되기 어렵다.

한편, 곤충은 기본 동작 감지기(Elementary Motion Detector) 라는 시신경 회로를 통해 시각 정보를 효과적으로 처리해 물체를 탐지하고 그 동작을 인식하는데 탁월한 능력을 보인다. <그림1> 이를 구현하는 데 있어 기존 실리콘 집적회로(CMOS) 기술에서는 복잡한 회로가 요구되기 때문에, 실제 소자로 제작하기 어려운 한계가 있었다.

김경민 교수 연구팀은 다양한 기능의 멤리스터 소자들을 집적하여 고효율⋅초고속 동작 인식이 가능한 지능형 동작인식 소자를 개발했다. 동작인식 소자는 자체 개발한 두 종류의 멤리스터 소자와 저항 만으로 구성된 단순한 구조를 가지고 있다. 두 종류의 서로 다른 멤리스터는 각각 신호 지연 기능과 신호 통합 및 발화 기능을 수행하며, 이를 통해 곤충의 시신경을 직접 모사하여 사물의 움직임을 판단할 수 있음을 확인했다. <그림2>

연구팀은 개발된 동작인식 소자의 실질적인 활용에 대한 가능성을 입증하기 위해 차량 경로를 예측하는 뉴로모픽 컴퓨팅 시스템을 설계하였으며, 여기에 개발한 동작인식 소자를 적용하였다. <그림3> 그 결과 기존 기술 대비 에너지 소비를 92.9 % 감소하여 더 정확히 사물의 움직임을 예측할 수 있음을 검증하였다.

신소재공학과 김경민 교수는 “곤충은 매우 간단한 시각 지능을 활용해 놀랍도록 민첩하게 물체의 동작을 인지하는데, 이번 연구는 신경의 기능을 재현할 수 있는 멤리스터 소자를 활용해 이를 구현할 수 있었다는 점에 큰 의의가 있다”며, “최근 AI가 탑재된 휴대폰과 같이 에지(edge)형 인공지능 소자의 중요성이 매우 커지고 있는데, 이 연구는 동작 인식을 위한 효율적인 비전 시스템 구현에 기여할 수 있어, 향후 자율주행 자동차, 차량 운송 시스템, 로봇, 머신 비전 등과 같은 다양한 분야에 적용될 수 있을 것으로 기대된다”고 밝혔다.

이번 연구는 신소재공학과 송한찬 박사과정, 이민구 박사과정 학생이 공동 제1 저자로 참여했으며, 국제 학술지 ‘어드밴스드 머티리얼즈(Advanced Materials, IF: 29.4)’에 지난 1월 29일 字 온라인 게재됐다.

한편 이번 연구는 한국연구재단 중견연구사업, 차세대지능형반도체기술개발사업, PIM인공지능반도체핵심기술개발사업, 나노종합기술원 및 KAIST 도약연구사업의 지원을 받아 수행됐다. (논문명: Fully Memristive Elementary Motion Detectors for A Maneuver Prediction, 논문링크: https://doi.org/10.1002/adma.202309708)

2024.02.19 조회수 7660 -

차세대 2차원 반도체 다기능 전자 소자 개발

공급 전압에 의한 2차원 반도체의 극성 전환을 이용해 새로운 전자 소자로의 응용이 보고된 바 있으나, 모두 누설 전류가 크거나 낮은 전류점멸비로 인해 실제 집적 회로(IC)칩에서 사용하기 어려웠다. 우리 대학 연구팀은 다기능 전자 소자를 통해 프로그램 및 기능성 변환이 가능한 회로 구현의 가능성을 제시하고 IC칩에서의 2차원 반도체의 활용성을 확장하는 기술을 개발하였다.

우리 대학 전기및전자공학부 이가영 교수 연구팀이 양극성 반도체 특성을 가진 2차원 나노 반도체 기반의 다기능 전자 소자를 개발했다고 2일 밝혔다. 다기능 전자 소자란 기존 트랜지스터와 달리 전압에 따라 기능을 변환할 수 있는 소자로, 연구팀의 소자는 양극성 트랜지스터, N형 트랜지스터, 다이오드, 항복 다이오드 그리고 광 감지 소자로 변환 가능하여 폭 넓은 사용이 가능하다.

기존 실리콘 반도체보다 성능이 뛰어난 이황화 몰리브덴(MoS2)는 층상 구조의 2차원 반도체 나노 소재로, 전자가 흐르는 N형 반도체 특성을 가지면서 대기에서 안정적이다. 또한, 기존 실리콘 반도체가 미세화될수록 성능 저하에 취약함에 반해, 이황화 몰리브덴은 관련 문제가 적어 차세대 반도체로서 학계뿐만 아니라 삼성, TSMC, 인텔과 같은 산업계에서의 연구도 활발하다.

그러나 상보적 금속산화막 반도체(CMOS) 구현을 위해서는 음(N) 전하를 띄는 전자뿐만 아니라 양(P) 전하를 띄는 정공 유도도 필요한 데, 이황화 몰리브덴에서는 정공 유도가 어려웠다. 이 문제를 해결하기 위해 이황화 몰리브덴에 추가적인 공정을 도입하거나 다른 P형 물질을 사용하는 방법이 시도됐으나, 공정 난이도가 높다. 이러한 문제점은 현재까지도 이황화 몰리브덴을 상용화하기 위해 해결해야 할 중요한 과제로 남아 있다.

이가영 교수 연구팀은 채널 하부에 전극을 배치하고 금속/반도체 접합 특성을 개선해 전자와 정공 모두 선택적으로 흐를 수 있는 양극성 특성을 구현하는 데 성공했다. 이로써 전류의 점멸 비율을 대폭 높일 뿐만 아니라, 양극성 트랜지스터, N형 트랜지스터, 다이오드, 항복 다이오드 그리고 광감지 소자로 다기능 변조 동작이 가능한 이황화 몰리브덴 전자 소자를 개발했다. 또한 이를 기반으로 집적도가 개선된 논리 연산이 가능함도 보였다.

이번 연구를 주도한 송준기, 이수연 학생은 “기존 실리콘 금속산화막 반도체(CMOS) 공정 호환성이 높은 공정 과정을 통해 차세대 2차원 반도체의 다양한 기능을 구현했다”며 “IC칩에서 이황화 몰리브덴의 전자소자로의 활용성 및 실용성을 넓히는 계기가 될 것이다”라고 덧붙였다.

이가영 교수는 “이번에 개발한 전자 소자는 주어진 전압 특성에 따라 다양한 기능을 수행하면서도 각 기능의 성능이 우수하다”며 “서로 다른 기능의 소자들은 대개 구조와 공정 방법들이 달라 함께 집적시 공정 난이도가 높고 회로 도면 변화에 따른 공정 전환이 까다롭다. 반면, 이번에 개발한 신개념 소자는 하나의 소자에서 다기능을 할 수 있어서 현재 수요가 급증하고 있는 맞춤형 반도체의 제작 및 공정 전환을 용이하게 할 것이다. 목적에 따라 회로 자체의 기능성을 변환할 수 있어 단일 칩 시스템의 소형화에도 기여할 것으로 기대한다”라고 말했다.

우리 대학 전기및전자공학부 송준기 석박통합과정 학생과 이수연 석사과정 학생이 공동 제1 저자로 참여한 이번 연구는 나노과학 분야 저명 국제 학술지 `ACS Nano'에 2024년 1월 26일 온라인판에 출판됐다. (논문명 : Drain-induced multifunctional ambipolar electronics based on junctionless MoS2)

한편 이번 연구는 한국연구재단의 기초연구사업 및 BK21, KAIST의 C2 사업, 그리고 LX 세미콘-KAIST 미래기술센터의 지원을 받아 수행됐다.

2024.02.05 조회수 7513

차세대 2차원 반도체 다기능 전자 소자 개발

공급 전압에 의한 2차원 반도체의 극성 전환을 이용해 새로운 전자 소자로의 응용이 보고된 바 있으나, 모두 누설 전류가 크거나 낮은 전류점멸비로 인해 실제 집적 회로(IC)칩에서 사용하기 어려웠다. 우리 대학 연구팀은 다기능 전자 소자를 통해 프로그램 및 기능성 변환이 가능한 회로 구현의 가능성을 제시하고 IC칩에서의 2차원 반도체의 활용성을 확장하는 기술을 개발하였다.

우리 대학 전기및전자공학부 이가영 교수 연구팀이 양극성 반도체 특성을 가진 2차원 나노 반도체 기반의 다기능 전자 소자를 개발했다고 2일 밝혔다. 다기능 전자 소자란 기존 트랜지스터와 달리 전압에 따라 기능을 변환할 수 있는 소자로, 연구팀의 소자는 양극성 트랜지스터, N형 트랜지스터, 다이오드, 항복 다이오드 그리고 광 감지 소자로 변환 가능하여 폭 넓은 사용이 가능하다.

기존 실리콘 반도체보다 성능이 뛰어난 이황화 몰리브덴(MoS2)는 층상 구조의 2차원 반도체 나노 소재로, 전자가 흐르는 N형 반도체 특성을 가지면서 대기에서 안정적이다. 또한, 기존 실리콘 반도체가 미세화될수록 성능 저하에 취약함에 반해, 이황화 몰리브덴은 관련 문제가 적어 차세대 반도체로서 학계뿐만 아니라 삼성, TSMC, 인텔과 같은 산업계에서의 연구도 활발하다.

그러나 상보적 금속산화막 반도체(CMOS) 구현을 위해서는 음(N) 전하를 띄는 전자뿐만 아니라 양(P) 전하를 띄는 정공 유도도 필요한 데, 이황화 몰리브덴에서는 정공 유도가 어려웠다. 이 문제를 해결하기 위해 이황화 몰리브덴에 추가적인 공정을 도입하거나 다른 P형 물질을 사용하는 방법이 시도됐으나, 공정 난이도가 높다. 이러한 문제점은 현재까지도 이황화 몰리브덴을 상용화하기 위해 해결해야 할 중요한 과제로 남아 있다.

이가영 교수 연구팀은 채널 하부에 전극을 배치하고 금속/반도체 접합 특성을 개선해 전자와 정공 모두 선택적으로 흐를 수 있는 양극성 특성을 구현하는 데 성공했다. 이로써 전류의 점멸 비율을 대폭 높일 뿐만 아니라, 양극성 트랜지스터, N형 트랜지스터, 다이오드, 항복 다이오드 그리고 광감지 소자로 다기능 변조 동작이 가능한 이황화 몰리브덴 전자 소자를 개발했다. 또한 이를 기반으로 집적도가 개선된 논리 연산이 가능함도 보였다.

이번 연구를 주도한 송준기, 이수연 학생은 “기존 실리콘 금속산화막 반도체(CMOS) 공정 호환성이 높은 공정 과정을 통해 차세대 2차원 반도체의 다양한 기능을 구현했다”며 “IC칩에서 이황화 몰리브덴의 전자소자로의 활용성 및 실용성을 넓히는 계기가 될 것이다”라고 덧붙였다.

이가영 교수는 “이번에 개발한 전자 소자는 주어진 전압 특성에 따라 다양한 기능을 수행하면서도 각 기능의 성능이 우수하다”며 “서로 다른 기능의 소자들은 대개 구조와 공정 방법들이 달라 함께 집적시 공정 난이도가 높고 회로 도면 변화에 따른 공정 전환이 까다롭다. 반면, 이번에 개발한 신개념 소자는 하나의 소자에서 다기능을 할 수 있어서 현재 수요가 급증하고 있는 맞춤형 반도체의 제작 및 공정 전환을 용이하게 할 것이다. 목적에 따라 회로 자체의 기능성을 변환할 수 있어 단일 칩 시스템의 소형화에도 기여할 것으로 기대한다”라고 말했다.

우리 대학 전기및전자공학부 송준기 석박통합과정 학생과 이수연 석사과정 학생이 공동 제1 저자로 참여한 이번 연구는 나노과학 분야 저명 국제 학술지 `ACS Nano'에 2024년 1월 26일 온라인판에 출판됐다. (논문명 : Drain-induced multifunctional ambipolar electronics based on junctionless MoS2)

한편 이번 연구는 한국연구재단의 기초연구사업 및 BK21, KAIST의 C2 사업, 그리고 LX 세미콘-KAIST 미래기술센터의 지원을 받아 수행됐다.

2024.02.05 조회수 7513 -

“반도체로 양자컴퓨터를 모방하다” 신개념 확률론적 컴퓨팅 핵심소자 개발

우리 대학 신소재공학과 김경민 교수 연구팀이 산화나이오븀(NbO2) 의 확률적 금속-절연체 전이 현상을 이용한 차세대 확률론적 컴퓨팅의 핵심 반도체 소자를 개발했다고 23일 밝혔다.

최근 IoT (Internet of Things), 자율주행, 빅데이터, 인공지능으로 대표되는 초연결시대가 진행됨에 따라 다양한 제한 조건과 구성 요소들이 상호작용하는 상황에서 최적의 해결책을 신속하게 찾아내는 '조합최적화 문제’의 해결이 중요한 과제로 부상하고 있다. 예를 들면, 네비게이션에 활용되는 최적 경로 탐색과 같은 문제가 조합최적화 문제에 해당한다. 조합최적화 문제는 복잡도가 증가함에 따라 해답을 찾기가 급격히 어려워지는 특성을 갖기에, 이를 효과적으로 해결할 수 있는 신개념 컴퓨팅 기술이 요구된다. 양자컴퓨팅은 그 대표적인 예시이지만 간섭, 오류 수정, 안정성 등의 이유로 양자 컴퓨팅의 상용화에는 여전히 많은 어려움이 남아 있다.

확률론적 컴퓨터의 기본 소자는 피비트* (pbit)라고 불리는데, 확률론적 컴퓨터는 피비트의 확률적 특성을 이용한다는 점에서 양자컴퓨터와 유사하지만, 기존 반도체 기술로 제작이 가능하여 상용화 측면에서 보다 현실적인 기술이다.

*피비트: Probabilistic bit의 줄임 말로 기존 디지털 시스템에서 사용하는 0, 1의 비트 정보를 출력하지만 각 상태 출력이 고정적이지 않고 확률적인 기본 소자

김경민 교수 연구팀은 산화나이오븀 (NbO2) 재료가 갖는 금속-절연체 전이 현상이 특정 조건에서 확률적으로 발생할 수 있음을 최초로 발견하였으며, 이를 활용해 확률론적 컴퓨팅을 위한 피비트의 제작에 성공하였다. 연구팀에서 개발한 피비트는 비트 당 평균 128pJ의 에너지, 260ns의 속도로 비트를 발생시키며, 이는 기존 저항변화메모리 기반 피비트 기술에 비해 약 20% 에너지 소모가 적으며, 약 4천 배 빠르다.

이에 더하여, 해당 반도체 피비트를 기반으로 하는 확률론적 컴퓨팅 시스템을 설계하였으며, 실제로 조합최적화 문제를 해결하는 사례를 통해 개발한 소자의 실질적인 활용에 대한 가능성을 입증했다.

김경민 교수는 “확률적 신호를 기존 CMOS 기반 회로를 통해 발생시키기 위해서는 매우 복잡한 구조가 요구되는데, 이번 연구는 모트 전이라고 하는 금속-절연체 전이 현상을 통해 확률적 신호를 직접 출력하는 단일 반도체 소자를 구현했다는 점에 큰 의의가 있다”며 “이 기술은 기존 반도체 기술과 융합될 수 있어 양자컴퓨팅의 기능을 수행할 수 있는 현실적인 대안이 될 것”이라고 말했다.

이번 연구는 신소재공학과 이학승 박사과정 학생이 제1 저자로 참여했으며, 국제 학술지 ‘네이처 커뮤니케이션즈 (Nature Communications, IF: 16.6)’에 11월 8일 字 게재됐으며 한국연구재단 PIM인공지능반도체 사업, 나노종합기술원, 그리고 KAIST의 지원을 받아 수행됐다.

논문명: Probabilistic computing with NbOx metal-insulator transition-based self-oscillatory pbit, 논문링크: https://doi.org/10.1038/s41467-023-43085-6

2023.11.23 조회수 11550

“반도체로 양자컴퓨터를 모방하다” 신개념 확률론적 컴퓨팅 핵심소자 개발

우리 대학 신소재공학과 김경민 교수 연구팀이 산화나이오븀(NbO2) 의 확률적 금속-절연체 전이 현상을 이용한 차세대 확률론적 컴퓨팅의 핵심 반도체 소자를 개발했다고 23일 밝혔다.

최근 IoT (Internet of Things), 자율주행, 빅데이터, 인공지능으로 대표되는 초연결시대가 진행됨에 따라 다양한 제한 조건과 구성 요소들이 상호작용하는 상황에서 최적의 해결책을 신속하게 찾아내는 '조합최적화 문제’의 해결이 중요한 과제로 부상하고 있다. 예를 들면, 네비게이션에 활용되는 최적 경로 탐색과 같은 문제가 조합최적화 문제에 해당한다. 조합최적화 문제는 복잡도가 증가함에 따라 해답을 찾기가 급격히 어려워지는 특성을 갖기에, 이를 효과적으로 해결할 수 있는 신개념 컴퓨팅 기술이 요구된다. 양자컴퓨팅은 그 대표적인 예시이지만 간섭, 오류 수정, 안정성 등의 이유로 양자 컴퓨팅의 상용화에는 여전히 많은 어려움이 남아 있다.

확률론적 컴퓨터의 기본 소자는 피비트* (pbit)라고 불리는데, 확률론적 컴퓨터는 피비트의 확률적 특성을 이용한다는 점에서 양자컴퓨터와 유사하지만, 기존 반도체 기술로 제작이 가능하여 상용화 측면에서 보다 현실적인 기술이다.

*피비트: Probabilistic bit의 줄임 말로 기존 디지털 시스템에서 사용하는 0, 1의 비트 정보를 출력하지만 각 상태 출력이 고정적이지 않고 확률적인 기본 소자

김경민 교수 연구팀은 산화나이오븀 (NbO2) 재료가 갖는 금속-절연체 전이 현상이 특정 조건에서 확률적으로 발생할 수 있음을 최초로 발견하였으며, 이를 활용해 확률론적 컴퓨팅을 위한 피비트의 제작에 성공하였다. 연구팀에서 개발한 피비트는 비트 당 평균 128pJ의 에너지, 260ns의 속도로 비트를 발생시키며, 이는 기존 저항변화메모리 기반 피비트 기술에 비해 약 20% 에너지 소모가 적으며, 약 4천 배 빠르다.

이에 더하여, 해당 반도체 피비트를 기반으로 하는 확률론적 컴퓨팅 시스템을 설계하였으며, 실제로 조합최적화 문제를 해결하는 사례를 통해 개발한 소자의 실질적인 활용에 대한 가능성을 입증했다.

김경민 교수는 “확률적 신호를 기존 CMOS 기반 회로를 통해 발생시키기 위해서는 매우 복잡한 구조가 요구되는데, 이번 연구는 모트 전이라고 하는 금속-절연체 전이 현상을 통해 확률적 신호를 직접 출력하는 단일 반도체 소자를 구현했다는 점에 큰 의의가 있다”며 “이 기술은 기존 반도체 기술과 융합될 수 있어 양자컴퓨팅의 기능을 수행할 수 있는 현실적인 대안이 될 것”이라고 말했다.

이번 연구는 신소재공학과 이학승 박사과정 학생이 제1 저자로 참여했으며, 국제 학술지 ‘네이처 커뮤니케이션즈 (Nature Communications, IF: 16.6)’에 11월 8일 字 게재됐으며 한국연구재단 PIM인공지능반도체 사업, 나노종합기술원, 그리고 KAIST의 지원을 받아 수행됐다.

논문명: Probabilistic computing with NbOx metal-insulator transition-based self-oscillatory pbit, 논문링크: https://doi.org/10.1038/s41467-023-43085-6

2023.11.23 조회수 11550 -

반도체 기술로 75배 향상된 초고효율 수소 생산 성공

반도체 공정기술을 활용하여 세계 최고 수준의 높은 수소 생산 효율을 장기간 유지하는 기술이 개발되어 화제다.

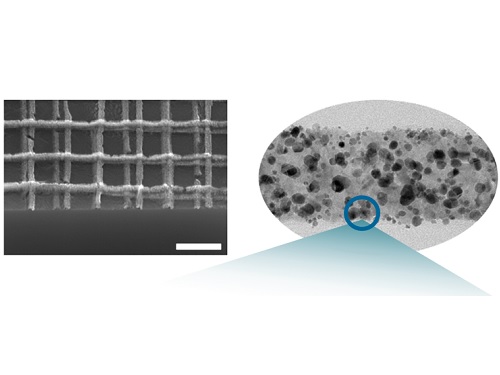

우리 대학 신소재공학과 정연식 교수·KIST(원장 윤석진) 김진영 박사·김동훈 박사 공동 연구팀이 수소 생산 촉매가 반응 중 잃어버리는 전자를 신개념 산화물 반도체로부터 보충받는 새로운 원리를 활용해 고효율 및 고내구성 수소 생산 기술을 개발했다고 25일 밝혔다.

고순도 그린 수소를 생산하기 위해 신재생에너지로 물을 전기분해하는 친환경적인 고분자 전해질막 수전해(PEMWE) 장치를 활용하게 된다. 이때 주로 사용되는 이리듐(Ir) 촉매의 경우 전자를 많이 가지고 있는 상태를 지속적으로 유지해야 고효율과 고내구성을 동시에 달성할 수 있게 된다. 하지만 일반적으로 쉽게 전자를 잃어버리고 산화되는 촉매 반응의 특성 때문에 효율과 수명이 현저히 저하되는 고질적인 문제가 있었다.

KAIST-KIST 공동 연구팀은 초미세 패턴을 적층하여 3차원 네트워크 구조를 구현할 수 있는 반도체 기술을 활용하였다. 이때 사용한 물질은 안티모니(Sb)가 도핑된 주석 산화물이며, 이 산화물 표면에는 ‘전자 저장소’역할을 하는 산소 이온이 고농도로 분포하도록 반도체 증착 기술을 적용하였다. 이 독특한 산화물 반도체를 촉매 지지체로 사용하게 되면 표면에 위치한 산소 이온이 이리듐(Ir) 촉매로 충분한 양의 전자를 지속적으로 보충해 줌으로써 촉매의 높은 수소 생산 효율을 장기간 유지해 주게 된다.

연구팀은 이를 고분자 전해질막 수전해(PEMWE) 장치에 적용한 결과, 기존 이리듐(Ir) 상용 나노입자 촉매에 비해 최대 75배 개선된 세계 최고 수준의 성능 향상을 달성함과 동시에 높은 전류 밀도에서 장시간 구동하는 우수한 내구성 또한 확보했다.

우리 대학 정연식 교수는 “일반적으로 반도체 기술과 수소 생산은 크게 다른 분야로 여겨지지만, 기존 합성 기술로는 얻기 어려운 독특한 조성의 소재를 정밀 반도체 공정 기술로 구현함으로써 높은 효율을 달성할 수 있었고, 이는 기술 분야 간 융합의 중요성을 잘 보여주는 연구 사례”라고 덧붙였다. KIST 김진영 박사는“기존 귀금속 촉매량의 1/10 이하만 사용하고도 동등 이상의 성능을 달성해, 앞으로 추가 연구를 통해 그린 수소 생산의 경제성을 확보할 수 있을 것으로 기대된다”고 언급했다.

신소재공학과 이규락 학생, KIST 김준 박사, 홍두선 박사가 공동 제1 저자로 참여한 이번 연구는 국제학술지 `네이처 커뮤니케이션스(Nature Communications)' 9월 5일 字 온라인판에 게재됐다. (논문명: Efficient and sustainable water electrolysis achieved by excess electron reservoir enabling charge replenishment to catalysts)

이번 연구는 산업자원통상부 에너지혁신인재양성사업, 과학기술정보통신부 미래수소원천기술개발사업, 그리고 과학기술정보통신부 나노소재기술개발 사업 등의 지원을 받아 수행됐다.

2023.09.25 조회수 10287

반도체 기술로 75배 향상된 초고효율 수소 생산 성공

반도체 공정기술을 활용하여 세계 최고 수준의 높은 수소 생산 효율을 장기간 유지하는 기술이 개발되어 화제다.

우리 대학 신소재공학과 정연식 교수·KIST(원장 윤석진) 김진영 박사·김동훈 박사 공동 연구팀이 수소 생산 촉매가 반응 중 잃어버리는 전자를 신개념 산화물 반도체로부터 보충받는 새로운 원리를 활용해 고효율 및 고내구성 수소 생산 기술을 개발했다고 25일 밝혔다.

고순도 그린 수소를 생산하기 위해 신재생에너지로 물을 전기분해하는 친환경적인 고분자 전해질막 수전해(PEMWE) 장치를 활용하게 된다. 이때 주로 사용되는 이리듐(Ir) 촉매의 경우 전자를 많이 가지고 있는 상태를 지속적으로 유지해야 고효율과 고내구성을 동시에 달성할 수 있게 된다. 하지만 일반적으로 쉽게 전자를 잃어버리고 산화되는 촉매 반응의 특성 때문에 효율과 수명이 현저히 저하되는 고질적인 문제가 있었다.

KAIST-KIST 공동 연구팀은 초미세 패턴을 적층하여 3차원 네트워크 구조를 구현할 수 있는 반도체 기술을 활용하였다. 이때 사용한 물질은 안티모니(Sb)가 도핑된 주석 산화물이며, 이 산화물 표면에는 ‘전자 저장소’역할을 하는 산소 이온이 고농도로 분포하도록 반도체 증착 기술을 적용하였다. 이 독특한 산화물 반도체를 촉매 지지체로 사용하게 되면 표면에 위치한 산소 이온이 이리듐(Ir) 촉매로 충분한 양의 전자를 지속적으로 보충해 줌으로써 촉매의 높은 수소 생산 효율을 장기간 유지해 주게 된다.

연구팀은 이를 고분자 전해질막 수전해(PEMWE) 장치에 적용한 결과, 기존 이리듐(Ir) 상용 나노입자 촉매에 비해 최대 75배 개선된 세계 최고 수준의 성능 향상을 달성함과 동시에 높은 전류 밀도에서 장시간 구동하는 우수한 내구성 또한 확보했다.

우리 대학 정연식 교수는 “일반적으로 반도체 기술과 수소 생산은 크게 다른 분야로 여겨지지만, 기존 합성 기술로는 얻기 어려운 독특한 조성의 소재를 정밀 반도체 공정 기술로 구현함으로써 높은 효율을 달성할 수 있었고, 이는 기술 분야 간 융합의 중요성을 잘 보여주는 연구 사례”라고 덧붙였다. KIST 김진영 박사는“기존 귀금속 촉매량의 1/10 이하만 사용하고도 동등 이상의 성능을 달성해, 앞으로 추가 연구를 통해 그린 수소 생산의 경제성을 확보할 수 있을 것으로 기대된다”고 언급했다.

신소재공학과 이규락 학생, KIST 김준 박사, 홍두선 박사가 공동 제1 저자로 참여한 이번 연구는 국제학술지 `네이처 커뮤니케이션스(Nature Communications)' 9월 5일 字 온라인판에 게재됐다. (논문명: Efficient and sustainable water electrolysis achieved by excess electron reservoir enabling charge replenishment to catalysts)

이번 연구는 산업자원통상부 에너지혁신인재양성사업, 과학기술정보통신부 미래수소원천기술개발사업, 그리고 과학기술정보통신부 나노소재기술개발 사업 등의 지원을 받아 수행됐다.

2023.09.25 조회수 10287 -

인간의 뇌를 모방한 3차원 집적 뉴로모픽 반도체 개발

우리 대학 전기및전자공학부 최양규 교수, 명현 교수, 그리고 신소재공학과 이건재 교수 공동연구팀이 ‘인간의 뇌를 모방한 3차원 집적 뉴로모픽 반도체’를 개발하는 데에 성공했다. ‘인간의 뇌를 모방해 동일평면 상에 수평 집적한 뉴로모픽 반도체’를 개발(2021년 Science Advances 게재)하는 데에 성공했던 연구팀은, 뉴런 소자와 시냅스 소자를 상하부에 3차원 방식으로 수직 집적해, 보다 높은 집적도와 전력 효율을 가지는 뉴로모픽 반도체를 구현할 수 있음을 처음으로 보였다.

전기및전자공학부 졸업생 한준규 박사, 전기및전자공학부 이정우 박사과정과 김예은 박사과정, 그리고 신소재공학과 김영빈 박사과정이 공동 제1저자로 참여한 이번 연구는 저명 국제 학술지 ‘Advanced Science’ 2023년 9월 온라인판에 출판됐다. (논문명 : 3D Neuromorphic Hardware with Single Thin-Film Transistor Synapses Over Single Thin-Body Transistor Neurons by Monolithic Vertical Integration). ‘Advanced Science’는 재료과학, 물리학, 화학, 생명과학, 엔지니어링 분야의 기초 및 응용 연구를 다루는 학제 간 오픈 액세스 저널이다. (impact factor : 17.521)

뉴로모픽(neuromorphic) 하드웨어는, 인간의 뇌가 매우 복잡한 기능을 수행하지만 소비하는 에너지는 20와트(W) 밖에 되지 않는다는 것에 착안해, 인간의 뇌를 모방해 인공지능 기능을 하드웨어로 구현하는 방식이다. 뉴로모픽 하드웨어는 기존의 폰 노이만(von Neumann) 방식과 다르게 인공지능 기능을 초저전력으로 수행할 수 있어 많은 주목을 받고 있다. 뉴로모픽 하드웨어를 구현하기 위해서는 생물학적 뇌와 동일하게 일정 신호가 통합되었을 때 스파이크를 발생하는 뉴런과 두 뉴런 사이의 연결성을 기억하는 시냅스가 필요하다.

연구팀은 단일 박막 트랜지스터(thin-film transistor) 기반 시냅스 소자를 단일 트랜지스터 기반 뉴런 소자 위에 3차원 방식으로 수직 집적해, 높은 집적도와 전력 효율을 가지는 3차원 집적 뉴로모픽 반도체를 개발했다. 아래층 뉴런 소자의 손상 없이 위층 시냅스 소자를 제작하기 위해, 엑시머 레이저 어닐링(excimer laser annealing) 기법을 활용했다. 또한, 아래층 뉴런 소자의 손상 없이 위층 시냅스 소자의 내구성을 향상시키기 위해, 소자 내부의 줄열(Joule heat)을 이용한 자체 어닐링 기법도 제안했다. 이러한 뛰어난 내구성을 바탕으로, 이벤트 카메라(event camera)를 기반으로 제작된 손동작 기반의 수화 (手話) 패턴을 높은 성공률로 인식할 수 있음을 보였다.

2023.09.21 조회수 8637

인간의 뇌를 모방한 3차원 집적 뉴로모픽 반도체 개발

우리 대학 전기및전자공학부 최양규 교수, 명현 교수, 그리고 신소재공학과 이건재 교수 공동연구팀이 ‘인간의 뇌를 모방한 3차원 집적 뉴로모픽 반도체’를 개발하는 데에 성공했다. ‘인간의 뇌를 모방해 동일평면 상에 수평 집적한 뉴로모픽 반도체’를 개발(2021년 Science Advances 게재)하는 데에 성공했던 연구팀은, 뉴런 소자와 시냅스 소자를 상하부에 3차원 방식으로 수직 집적해, 보다 높은 집적도와 전력 효율을 가지는 뉴로모픽 반도체를 구현할 수 있음을 처음으로 보였다.

전기및전자공학부 졸업생 한준규 박사, 전기및전자공학부 이정우 박사과정과 김예은 박사과정, 그리고 신소재공학과 김영빈 박사과정이 공동 제1저자로 참여한 이번 연구는 저명 국제 학술지 ‘Advanced Science’ 2023년 9월 온라인판에 출판됐다. (논문명 : 3D Neuromorphic Hardware with Single Thin-Film Transistor Synapses Over Single Thin-Body Transistor Neurons by Monolithic Vertical Integration). ‘Advanced Science’는 재료과학, 물리학, 화학, 생명과학, 엔지니어링 분야의 기초 및 응용 연구를 다루는 학제 간 오픈 액세스 저널이다. (impact factor : 17.521)

뉴로모픽(neuromorphic) 하드웨어는, 인간의 뇌가 매우 복잡한 기능을 수행하지만 소비하는 에너지는 20와트(W) 밖에 되지 않는다는 것에 착안해, 인간의 뇌를 모방해 인공지능 기능을 하드웨어로 구현하는 방식이다. 뉴로모픽 하드웨어는 기존의 폰 노이만(von Neumann) 방식과 다르게 인공지능 기능을 초저전력으로 수행할 수 있어 많은 주목을 받고 있다. 뉴로모픽 하드웨어를 구현하기 위해서는 생물학적 뇌와 동일하게 일정 신호가 통합되었을 때 스파이크를 발생하는 뉴런과 두 뉴런 사이의 연결성을 기억하는 시냅스가 필요하다.

연구팀은 단일 박막 트랜지스터(thin-film transistor) 기반 시냅스 소자를 단일 트랜지스터 기반 뉴런 소자 위에 3차원 방식으로 수직 집적해, 높은 집적도와 전력 효율을 가지는 3차원 집적 뉴로모픽 반도체를 개발했다. 아래층 뉴런 소자의 손상 없이 위층 시냅스 소자를 제작하기 위해, 엑시머 레이저 어닐링(excimer laser annealing) 기법을 활용했다. 또한, 아래층 뉴런 소자의 손상 없이 위층 시냅스 소자의 내구성을 향상시키기 위해, 소자 내부의 줄열(Joule heat)을 이용한 자체 어닐링 기법도 제안했다. 이러한 뛰어난 내구성을 바탕으로, 이벤트 카메라(event camera)를 기반으로 제작된 손동작 기반의 수화 (手話) 패턴을 높은 성공률로 인식할 수 있음을 보였다.

2023.09.21 조회수 8637 -

2.4배 가격 효율적인 챗GPT 핵심 AI반도체 개발

오픈AI가 출시한 챗GPT는 전 세계적으로 화두이며 이 기술이 가져올 변화에 모두 주목하고 있다. 이 기술은 거대 언어 모델을 기반으로 하고 있다. 거대 언어 모델은 기존 인공지능과는 달리 전례 없는 큰 규모의 인공지능 모델이다. 이를 운영하기 위해서는 수많은 고성능 GPU가 필요해, 천문학적인 컴퓨팅 비용이 든다는 문제점이 있다.

우리 대학 전기및전자공학부 김주영 교수 연구팀이 챗GPT에 핵심으로 사용되는 거대 언어 모델의 추론 연산을 효율적으로 가속하는 AI 반도체를 개발했다고 4일 밝혔다.

연구팀이 개발한 AI 반도체 ‘LPU(Latency Processing Unit)’는 거대 언어 모델의 추론 연산을 효율적으로 가속한다. 메모리 대역폭 사용을 극대화하고 추론에 필요한 모든 연산을 고속으로 수행 가능한 연산 엔진을 갖춘 AI 반도체이며, 자체 네트워킹을 내장하여 다수개 가속기로 확장이 용이하다. 이 LPU 기반의 가속 어플라이언스 서버는 업계 최고의 고성능 GPU인 엔비디아 A100 기반 슈퍼컴퓨터보다 성능은 최대 50%, 가격 대비 성능은 2.4배가량 높였다. 이는 최근 급격하게 생성형 AI 서비스 수요가 증가하고 있는 데이터센터의에서 고성능 GPU를 대체할 수 있을 것으로 기대한다.

이번 연구는 김주영 교수의 창업기업인 ㈜하이퍼엑셀에서 수행했으며 미국시간 7월 12일 샌프란시스코에서 진행된 국제 반도체 설계 자동화 학회(Design Automation Conference, 이하 DAC)에서 공학 부문 최고 발표상(Engineering Best Presentation Award)을 수상하는 쾌거를 이뤘다.

DAC은 국제 반도체 설계 분야의 대표 학회이며, 특히 전자 설계 자동화(Electronic Design Automation, EDA)와 반도체 설계자산(Semiconductor Intellectual Property, IP) 기술 관련하여 세계적인 반도체 설계 기술을 선보이는 학회다. DAC에는 인텔, 엔비디아, AMD, 구글, 마이크로소프트, 삼성, TSMC 등 세계적인 반도체 설계 기업이 참가하며, 하버드대학교, MIT, 스탠퍼드대학교 등 세계 최고의 대학도 많이 참가한다.

세계적인 반도체 기술들 사이에서 김 교수팀이 거대 언어 모델을 위한 AI 반도체 기술로 유일하게 수상한 것은 매우 의미가 크다. 이번 수상으로 거대 언어 모델의 추론에 필요한 막대한 비용을 획기적으로 절감할 수 있는 AI 반도체 솔루션으로 세계 무대에서 인정받은 것이다.

우리 대학 김주영 교수는 “미래 거대 인공지능 연산을 위한 새로운 프로세서 ‘LPU’로 글로벌 시장을 개척하고, 빅테크 기업들의 기술력보다 우위를 선점하겠다”라며 큰 포부를 밝혔다.

2023.08.04 조회수 9351

2.4배 가격 효율적인 챗GPT 핵심 AI반도체 개발

오픈AI가 출시한 챗GPT는 전 세계적으로 화두이며 이 기술이 가져올 변화에 모두 주목하고 있다. 이 기술은 거대 언어 모델을 기반으로 하고 있다. 거대 언어 모델은 기존 인공지능과는 달리 전례 없는 큰 규모의 인공지능 모델이다. 이를 운영하기 위해서는 수많은 고성능 GPU가 필요해, 천문학적인 컴퓨팅 비용이 든다는 문제점이 있다.

우리 대학 전기및전자공학부 김주영 교수 연구팀이 챗GPT에 핵심으로 사용되는 거대 언어 모델의 추론 연산을 효율적으로 가속하는 AI 반도체를 개발했다고 4일 밝혔다.

연구팀이 개발한 AI 반도체 ‘LPU(Latency Processing Unit)’는 거대 언어 모델의 추론 연산을 효율적으로 가속한다. 메모리 대역폭 사용을 극대화하고 추론에 필요한 모든 연산을 고속으로 수행 가능한 연산 엔진을 갖춘 AI 반도체이며, 자체 네트워킹을 내장하여 다수개 가속기로 확장이 용이하다. 이 LPU 기반의 가속 어플라이언스 서버는 업계 최고의 고성능 GPU인 엔비디아 A100 기반 슈퍼컴퓨터보다 성능은 최대 50%, 가격 대비 성능은 2.4배가량 높였다. 이는 최근 급격하게 생성형 AI 서비스 수요가 증가하고 있는 데이터센터의에서 고성능 GPU를 대체할 수 있을 것으로 기대한다.

이번 연구는 김주영 교수의 창업기업인 ㈜하이퍼엑셀에서 수행했으며 미국시간 7월 12일 샌프란시스코에서 진행된 국제 반도체 설계 자동화 학회(Design Automation Conference, 이하 DAC)에서 공학 부문 최고 발표상(Engineering Best Presentation Award)을 수상하는 쾌거를 이뤘다.

DAC은 국제 반도체 설계 분야의 대표 학회이며, 특히 전자 설계 자동화(Electronic Design Automation, EDA)와 반도체 설계자산(Semiconductor Intellectual Property, IP) 기술 관련하여 세계적인 반도체 설계 기술을 선보이는 학회다. DAC에는 인텔, 엔비디아, AMD, 구글, 마이크로소프트, 삼성, TSMC 등 세계적인 반도체 설계 기업이 참가하며, 하버드대학교, MIT, 스탠퍼드대학교 등 세계 최고의 대학도 많이 참가한다.

세계적인 반도체 기술들 사이에서 김 교수팀이 거대 언어 모델을 위한 AI 반도체 기술로 유일하게 수상한 것은 매우 의미가 크다. 이번 수상으로 거대 언어 모델의 추론에 필요한 막대한 비용을 획기적으로 절감할 수 있는 AI 반도체 솔루션으로 세계 무대에서 인정받은 것이다.

우리 대학 김주영 교수는 “미래 거대 인공지능 연산을 위한 새로운 프로세서 ‘LPU’로 글로벌 시장을 개척하고, 빅테크 기업들의 기술력보다 우위를 선점하겠다”라며 큰 포부를 밝혔다.

2023.08.04 조회수 9351 -

2진법에서 3진법으로 종횡무진, 신개념 반도체 회로 개발

자율주행 및 기타 인공 지능(AI) 기술이 일상생활에서 널리 사용되면서 반도체 집적 회로 (Integrated circuit, IC)의 정보 처리 능력에 대한 수요가 급격히 늘어나고 있다.

우리 대학 생명화학공학과 임성갑 교수 연구팀이 가천대(총장 이길여) 전자공학부 유호천 교수 연구팀과 공동 연구를 통해 더 높은 데이터 처리 효율성과 집적도를 제공할 신개념 디지털 논리 회로 구현을 세계 최초로 성공했다고 11일 밝혔다.

기존 `0', `1'의 두 가지 논리 상태를 사용하는 2진법 논리 회로와 비교해 3진법 논리 회로는 `0', `1', `2'의 세 가지 논리 상태를 사용해 정보를 표현하는 차세대 반도체 기술로, 같은 정보를 더 적은 논리로 표현할 수 있어 더 높은 정보 처리 효율성을 통해 반도체 칩의 고속화, 저전력화, 소형화가 가능하다. 하지만 논리 상태가 1개 더 추가됨에 따라 세 가지 논리 신호를 모두 안정적으로 출력하기 어려운 문제와 2진법 논리 체계가 3진법 논리 체계와 서로 호환이 되지 않는 문제가 3진법 논리 회로 상용화에 걸림돌로 여겨졌다.

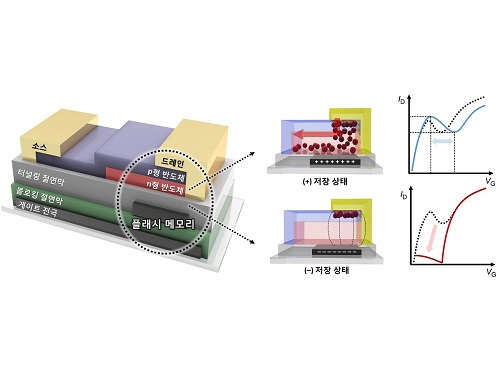

연구팀은 문제 해결을 위해 3진법 논리 회로의 출력 특성을 회로 동작 중에 실시간으로 조절할 수 있는 새로운 논리소자를 개발했다. 연구팀은 컴퓨터에서 필요에 따라 정보를 저장하거나 다시 지울 수 있는 장치인 플래시 메모리에 주목했으며, 3진법 논리 회로 자체에 정보를 저장할 수 있도록 회로를 구성하는 논리소자에 플래시 메모리를 집적했다. 연구팀은 3진법 논리 회로가 저장하고 있는 정보에 따라 논리 상태 `1'의 출력 특성이 체계적으로 조절될 수 있음을 확인하였으며, 이를 통해 3진법 논리 회로의 동작 안정성(잡음 여유)을 세계 최고 수준인 약 60%까지 달성하는데 성공했다.

또한 연구팀은 3진법 논리 회로에 저장된 정보를 완전히 지우는 경우에 논리 상태 `1'이 출력되지 않고 `0' 과 `2'의 두 논리 상태만 출력하는 점을 이용하여 2진법과 3진법 논리 동작이 모두 가능한 회로를 구현하는데 성공했다. 뿐만 아니라, 논리 회로를 구성하는 각각의 논리소자에 서로 다른 정보를 저장하는 방식으로 2진법과 3진법 논리 출력을 조합했고, 이에 따라 다양한 종류의 논리 출력을 갖는 논리 회로를 구현함으로써 3진법 논리 회로의 정보 처리 효율 및 집적도를 한 단계 더 향상시킬 수 있음 역시 확인했다.

연구팀이 개발한 논리소자는 동일한 반도체 칩 내에서 2진법 논리 회로와 3진법 논리 회로를 연동하여 데이터 및 신호 전달을 할 수 있다는 점에서 의의가 있다. 이것은 기존의 2진법 체계를 유지하면서 필요에 따라 3진법의 높은 정보 처리 능력을 탄력적으로 활용할 수 있다는 것을 의미하며, 향후 3진법 반도체의 상용화 시작 단계에 있어 핵심 기술이 될 것으로 기대가 크다.

우리 대학 임성갑 교수는 “기존 디지털 논리 회로와 비교해 다양한 연산이 가능하고 복잡한 연산을 훨씬 단순화할 수 있는 논리소자를 개발한 것으로, 이번 연구 결과는 향후 대용량 정보 처리가 필요한 인공지능, 사물인터넷 등 다양한 분야를 위한 신개념 반도체 소자에 있어 유용한 지침이 될 것으로 기대된다”고 말했다.

한편 선도연구센터 지원사업(웨어러블 플랫폼 소재 기술센터), 이공분야기초연구사업(과학기술정보통신부), 그리고 산업기술혁신사업(산업통상자원부)의 지원을 받아 수행된 이번 연구 결과는 우리 대학 생명화학공학과 이충열 박사과정 학생이 제1 저자로 참여했으며, 국제 학술지 `네이처 커뮤니케이션 (Nature Communications)' 6월 23일 자 온라인판에 게재됐다. (논문명: A reconfigurable binary/ternary logic conversion-in-memory based on drain-aligned floating-gate heterojunction transistors)

2023.07.11 조회수 8491

2진법에서 3진법으로 종횡무진, 신개념 반도체 회로 개발

자율주행 및 기타 인공 지능(AI) 기술이 일상생활에서 널리 사용되면서 반도체 집적 회로 (Integrated circuit, IC)의 정보 처리 능력에 대한 수요가 급격히 늘어나고 있다.

우리 대학 생명화학공학과 임성갑 교수 연구팀이 가천대(총장 이길여) 전자공학부 유호천 교수 연구팀과 공동 연구를 통해 더 높은 데이터 처리 효율성과 집적도를 제공할 신개념 디지털 논리 회로 구현을 세계 최초로 성공했다고 11일 밝혔다.

기존 `0', `1'의 두 가지 논리 상태를 사용하는 2진법 논리 회로와 비교해 3진법 논리 회로는 `0', `1', `2'의 세 가지 논리 상태를 사용해 정보를 표현하는 차세대 반도체 기술로, 같은 정보를 더 적은 논리로 표현할 수 있어 더 높은 정보 처리 효율성을 통해 반도체 칩의 고속화, 저전력화, 소형화가 가능하다. 하지만 논리 상태가 1개 더 추가됨에 따라 세 가지 논리 신호를 모두 안정적으로 출력하기 어려운 문제와 2진법 논리 체계가 3진법 논리 체계와 서로 호환이 되지 않는 문제가 3진법 논리 회로 상용화에 걸림돌로 여겨졌다.

연구팀은 문제 해결을 위해 3진법 논리 회로의 출력 특성을 회로 동작 중에 실시간으로 조절할 수 있는 새로운 논리소자를 개발했다. 연구팀은 컴퓨터에서 필요에 따라 정보를 저장하거나 다시 지울 수 있는 장치인 플래시 메모리에 주목했으며, 3진법 논리 회로 자체에 정보를 저장할 수 있도록 회로를 구성하는 논리소자에 플래시 메모리를 집적했다. 연구팀은 3진법 논리 회로가 저장하고 있는 정보에 따라 논리 상태 `1'의 출력 특성이 체계적으로 조절될 수 있음을 확인하였으며, 이를 통해 3진법 논리 회로의 동작 안정성(잡음 여유)을 세계 최고 수준인 약 60%까지 달성하는데 성공했다.

또한 연구팀은 3진법 논리 회로에 저장된 정보를 완전히 지우는 경우에 논리 상태 `1'이 출력되지 않고 `0' 과 `2'의 두 논리 상태만 출력하는 점을 이용하여 2진법과 3진법 논리 동작이 모두 가능한 회로를 구현하는데 성공했다. 뿐만 아니라, 논리 회로를 구성하는 각각의 논리소자에 서로 다른 정보를 저장하는 방식으로 2진법과 3진법 논리 출력을 조합했고, 이에 따라 다양한 종류의 논리 출력을 갖는 논리 회로를 구현함으로써 3진법 논리 회로의 정보 처리 효율 및 집적도를 한 단계 더 향상시킬 수 있음 역시 확인했다.

연구팀이 개발한 논리소자는 동일한 반도체 칩 내에서 2진법 논리 회로와 3진법 논리 회로를 연동하여 데이터 및 신호 전달을 할 수 있다는 점에서 의의가 있다. 이것은 기존의 2진법 체계를 유지하면서 필요에 따라 3진법의 높은 정보 처리 능력을 탄력적으로 활용할 수 있다는 것을 의미하며, 향후 3진법 반도체의 상용화 시작 단계에 있어 핵심 기술이 될 것으로 기대가 크다.

우리 대학 임성갑 교수는 “기존 디지털 논리 회로와 비교해 다양한 연산이 가능하고 복잡한 연산을 훨씬 단순화할 수 있는 논리소자를 개발한 것으로, 이번 연구 결과는 향후 대용량 정보 처리가 필요한 인공지능, 사물인터넷 등 다양한 분야를 위한 신개념 반도체 소자에 있어 유용한 지침이 될 것으로 기대된다”고 말했다.

한편 선도연구센터 지원사업(웨어러블 플랫폼 소재 기술센터), 이공분야기초연구사업(과학기술정보통신부), 그리고 산업기술혁신사업(산업통상자원부)의 지원을 받아 수행된 이번 연구 결과는 우리 대학 생명화학공학과 이충열 박사과정 학생이 제1 저자로 참여했으며, 국제 학술지 `네이처 커뮤니케이션 (Nature Communications)' 6월 23일 자 온라인판에 게재됐다. (논문명: A reconfigurable binary/ternary logic conversion-in-memory based on drain-aligned floating-gate heterojunction transistors)

2023.07.11 조회수 8491 -

광반도체 소자 집적도 100배 이상 높이다

라이다(LiDAR) 및 양자 센서·컴퓨터와 같은 복잡한 광학 시스템을 하나의 작은 칩으로 만들어 줄 수 있어 세계적으로 많은 연구와 투자가 이루어지고 있는 차세대 반도체 기술이 집적 광학 반도체(이하 광반도체) 기술이다. 기존의 반도체 기술에서 5나노, 2나노 등의 단위로 얼마나 작게 만드느냐가 관건이었는데, 광반도체 소자에서 집적도를 높이는 것은 성능, 가격, 에너지 효율 등을 결정짓는 핵심적인 기술이라 말할 수 있다.

우리 대학 전기및전자공학부 김상식 교수 연구팀이 광반도체 소자의 집적도를 100배 이상 높일 수 있는 새로운 광 결합 메커니즘을 발견했다고 19일 밝혔다.

하나의 칩당 구성할 수 있는 소자 수의 정도를 집적도(集積度)라고 하는데, 집적도가 높을수록 많은 연산을 할 수 있고 공정 단가 또한 낮춰준다. 하지만 광반도체 소자의 집적도를 높이기는 매우 어려운데, 이는 빛의 파동성으로 인해 근접한 소자 사이에서 광자 간에 혼선(crosstalk)이 발생하기 때문이다.

기존 연구에서는 특정 편광에서만 빛의 혼선을 줄여줄 수 있었는데, 연구팀은 이번 연구에서 새로운 광 결합(coupling) 메커니즘의 발견으로써 기존에는 불가능이라 여겨졌던 편광 조건에서도 집적도를 높이는 방법을 개발했다.

김상식 교수가 교신저자로 주도하고 미국 텍사스 공과대학 재직 당시 지도하던 학생들과 함께한 이번 연구는 국제학술지‘라이트: 사이언스 앤 어플리케이션(Light: Science & Applications)’ [IF=20.257]에 6월 2일 字 게재됐다. (논문명: Anisotropic leaky-like perturbation with subwavelength gratings enables zero crosstalk).

김상식 교수는 “이번 연구가 흥미로운 점은 기존에는 오히려 빛의 혼선을 크게 해줄 거라고 여겨졌던 누설파(leaky wave, 빛이 옆으로 잘 퍼지는 특성을 가짐)를 통해 역설적으로 혼선을 없애준 점이다”라며 “이번 연구에서 밝혀진 누설파를 이용한 광 결합 방법을 응용한다면 더욱 작고 노이즈가 적은 다양한 광반도체 소자를 개발할 수 있을 것이다”라고 말했다.

김상식 교수는 광반도체의 집적도에 있어서 전문성과 연구 업적을 인정받는 연구자다. 선행 연구를 통해 반도체 구조물을 파장보다 작은 크기로 패턴화해 빛이 옆으로 퍼지는 정도를 제어할 수 있는 무손실 메타물질(all-dielectric metamaterial)을 개발했고, 실험을 통해 이를 입증해 광반도체 집적도에 있어서 세계적인 기록을 보유하고 있다. 이러한 연구는 ‘네이처 커뮤니케이션즈(Nature Communications) 9, 1893 (2018)’와 ‘옵티카(Optica) 7, 881-887 (2020)’에 보고됐다. 김 교수는 이러한 성과를 인정받아 미국 국립과학재단(National Science Foundation, NSF)에서 NSF 커리어 어워드(NSF Career Award)와 재미한인과학기술자협회에서 젊은과학기술자상을 수상한 바 있다.

한편 이번 연구는 한국연구재단 우수신진연구 사업 및 미국 NSF의 지원을 받아 수행됐다.

2023.06.19 조회수 6409

광반도체 소자 집적도 100배 이상 높이다

라이다(LiDAR) 및 양자 센서·컴퓨터와 같은 복잡한 광학 시스템을 하나의 작은 칩으로 만들어 줄 수 있어 세계적으로 많은 연구와 투자가 이루어지고 있는 차세대 반도체 기술이 집적 광학 반도체(이하 광반도체) 기술이다. 기존의 반도체 기술에서 5나노, 2나노 등의 단위로 얼마나 작게 만드느냐가 관건이었는데, 광반도체 소자에서 집적도를 높이는 것은 성능, 가격, 에너지 효율 등을 결정짓는 핵심적인 기술이라 말할 수 있다.

우리 대학 전기및전자공학부 김상식 교수 연구팀이 광반도체 소자의 집적도를 100배 이상 높일 수 있는 새로운 광 결합 메커니즘을 발견했다고 19일 밝혔다.

하나의 칩당 구성할 수 있는 소자 수의 정도를 집적도(集積度)라고 하는데, 집적도가 높을수록 많은 연산을 할 수 있고 공정 단가 또한 낮춰준다. 하지만 광반도체 소자의 집적도를 높이기는 매우 어려운데, 이는 빛의 파동성으로 인해 근접한 소자 사이에서 광자 간에 혼선(crosstalk)이 발생하기 때문이다.

기존 연구에서는 특정 편광에서만 빛의 혼선을 줄여줄 수 있었는데, 연구팀은 이번 연구에서 새로운 광 결합(coupling) 메커니즘의 발견으로써 기존에는 불가능이라 여겨졌던 편광 조건에서도 집적도를 높이는 방법을 개발했다.

김상식 교수가 교신저자로 주도하고 미국 텍사스 공과대학 재직 당시 지도하던 학생들과 함께한 이번 연구는 국제학술지‘라이트: 사이언스 앤 어플리케이션(Light: Science & Applications)’ [IF=20.257]에 6월 2일 字 게재됐다. (논문명: Anisotropic leaky-like perturbation with subwavelength gratings enables zero crosstalk).

김상식 교수는 “이번 연구가 흥미로운 점은 기존에는 오히려 빛의 혼선을 크게 해줄 거라고 여겨졌던 누설파(leaky wave, 빛이 옆으로 잘 퍼지는 특성을 가짐)를 통해 역설적으로 혼선을 없애준 점이다”라며 “이번 연구에서 밝혀진 누설파를 이용한 광 결합 방법을 응용한다면 더욱 작고 노이즈가 적은 다양한 광반도체 소자를 개발할 수 있을 것이다”라고 말했다.

김상식 교수는 광반도체의 집적도에 있어서 전문성과 연구 업적을 인정받는 연구자다. 선행 연구를 통해 반도체 구조물을 파장보다 작은 크기로 패턴화해 빛이 옆으로 퍼지는 정도를 제어할 수 있는 무손실 메타물질(all-dielectric metamaterial)을 개발했고, 실험을 통해 이를 입증해 광반도체 집적도에 있어서 세계적인 기록을 보유하고 있다. 이러한 연구는 ‘네이처 커뮤니케이션즈(Nature Communications) 9, 1893 (2018)’와 ‘옵티카(Optica) 7, 881-887 (2020)’에 보고됐다. 김 교수는 이러한 성과를 인정받아 미국 국립과학재단(National Science Foundation, NSF)에서 NSF 커리어 어워드(NSF Career Award)와 재미한인과학기술자협회에서 젊은과학기술자상을 수상한 바 있다.

한편 이번 연구는 한국연구재단 우수신진연구 사업 및 미국 NSF의 지원을 받아 수행됐다.

2023.06.19 조회수 6409 -

고성능 조립형 SSD 시스템반도체 최초 개발

최근 인공지능을 훈련하기 위해 더 많은 데이터가 필요해지면서 그 중요성은 더욱 증가하고 있으며, 이에 데이터 센터 및 클라우드 서비스를 위한 주요 저장장치인 고성능 SSD(Solid State Drive, 반도체 기억소자를 사용하는 저장장치) 제품의 필요성이 높아지고 있다. 하지만, 고성능 SSD 제품일수록 SSD 내부의 구성요소들이 서로의 성능에 크게 영향을 미치는 상호-결합형(tightly-coupled) 구조의 한계에 부딪혀 성능을 극대화하기 어려웠다.

우리 대학 전기및전자공학부 김동준 교수 연구팀이 고성능 조립형 SSD 시스템 개발을 통해 차세대 SSD의 읽기/쓰기 성능을 비약적으로 높일 뿐 아니라 SSD 수명연장에도 적용 가능한 SSD 시스템 반도체 구조를 세계 최초로 개발했다고 15일 밝혔다.

김동준 교수 연구팀은 기존 SSD 설계가 갖는 상호-결합형 구조의 한계를 밝히고, CPU, GPU 등의 비메모리 시스템 반도체 설계에서 주로 활용되는 칩 내부에서 패킷-기반 데이터를 자유롭게 전송하는 온-칩 네트워크 기술을 바탕으로 SSD 내부에 플래시 메모리 전용 온-칩 네트워크를 구성함으로써 성능을 극대화하는 상호-분리형(de-coupled) 구조를 제안했으며, 이를 통해 SSD의 프론트-엔드 설계와 백-엔드 설계의 상호 의존도를 줄여 독립적으로 설계하고 조립 가능한 ‘조립형 SSD’를 개발했다.

※온-칩 네트워크(on-chip network): CPU/GPU등의 시스템 반도체 설계에 쓰이는 칩 내부의 요소에 대한 패킷-기반 연결구조를 말한다. 온-칩 네트워크는 고성능 시스템 반도체를 위한 필수적인 설계 요소중 하나로서 반도체칩의 규모가 증가할수록 더욱 중요해지는 특징이 있다.

김동준 교수팀이 개발한 조립형 SSD 시스템 구조는 내부 구성요소 중 SSD 컨트롤러 내부, 플래시 메모리 인터페이스를 기점으로 CPU에 가까운 부분을 프론트-엔드(front-end), 플래시 메모리에 가까운 부분을 백-엔드(back-end)로 구분하고, 백-엔드의 플래시 컨트롤러 사이 간 데이터 이동이 가능한 플래시 메모리 전용 온-칩 네트워크를 새롭게 구성해, 성능 감소를 최소화하는 상호-분리형 구조를 제안했다.

SSD를 구동하는 핵심 요소인 플래시 변환 계층의 일부 기능을 하드웨어로 가속하여 플래시 메모리가 갖는 한계를 능동적으로 극복할 수 있는 계기를 마련하였고 상호-분리형 구조는 플래시 변환 계층이 특정 플래시 메모리의 특성에 국한되지 않고, 프론트-엔드 설계와 백-엔드 설계를 독립적으로 수행하는 설계의 용이성을 가지는 점이 ‘조립형’ SSD 구조의 장점이라고 밝혔다. 이를 통해, 기존 시스템 대비 응답시간을 31배 줄일 수 있었고 SSD 불량 블록 관리기법에도 적용해 약 23%의 SSD 수명을 연장할 수 있다고 연구팀 관계자는 설명했다.

전기및전자공학부 김지호 박사과정이 제1 저자, 전기및전자공학부 정명수 교수가 공동 저자로 참여한 이번 연구는 미국 플로리다주 올랜도에서 열리는 컴퓨터 구조 분야 최우수 국제 학술대회인 `제50회 국제 컴퓨터 구조 심포지엄(50th IEEE/ACM International Symposium on Computer Architecture, ISCA 2023)'에서 6월 19일 발표될 예정이다. (논문명: Decoupled SSD: Rethinking SSD Architecture through Network-based Flash Controllers).

연구를 주도한 김동준 교수는 “이번 연구는 기존의 SSD가 가지는 구조적 한계를 규명했다는 점과 CPU와 같은 시스템 메모리 반도체 중심의 온-칩 네트워크 기술을 적용해 하드웨어가 능동적으로 필요한 일을 수행할 수 있다는 점에서 의의가 있으며 차세대 고성능 SSD 시장에 기여할 것으로 보인다”며, “상호-분리형 구조는 수명연장을 위해서도 능동적으로 동작하는 SSD 구조로써 그 가치가 성능에만 국한되지 않아 다양한 쓰임새를 가진다며”연구의 의의를 설명했다.

이번 연구는 컴퓨터 시스템 저장장치 분야의 저명한 연구자인 KAIST 정명수 교수와 컴퓨터 구조 및 인터커넥션 네트워크(Interconnection Network) 분야의 권위자인 김동준 교수, 두 세계적인 연구자의 융합연구를 통해 이루어낸 연구라는 의미가 있다고 관계자는 설명했다.

한편 이번 연구는 한국연구재단, 삼성전자, 반도체설계교육센터(IDEC), 정보통신기획평가원 차세대지능형반도체기술개발사업의 지원을 받아 수행됐다.

2023.06.15 조회수 7686

고성능 조립형 SSD 시스템반도체 최초 개발

최근 인공지능을 훈련하기 위해 더 많은 데이터가 필요해지면서 그 중요성은 더욱 증가하고 있으며, 이에 데이터 센터 및 클라우드 서비스를 위한 주요 저장장치인 고성능 SSD(Solid State Drive, 반도체 기억소자를 사용하는 저장장치) 제품의 필요성이 높아지고 있다. 하지만, 고성능 SSD 제품일수록 SSD 내부의 구성요소들이 서로의 성능에 크게 영향을 미치는 상호-결합형(tightly-coupled) 구조의 한계에 부딪혀 성능을 극대화하기 어려웠다.

우리 대학 전기및전자공학부 김동준 교수 연구팀이 고성능 조립형 SSD 시스템 개발을 통해 차세대 SSD의 읽기/쓰기 성능을 비약적으로 높일 뿐 아니라 SSD 수명연장에도 적용 가능한 SSD 시스템 반도체 구조를 세계 최초로 개발했다고 15일 밝혔다.

김동준 교수 연구팀은 기존 SSD 설계가 갖는 상호-결합형 구조의 한계를 밝히고, CPU, GPU 등의 비메모리 시스템 반도체 설계에서 주로 활용되는 칩 내부에서 패킷-기반 데이터를 자유롭게 전송하는 온-칩 네트워크 기술을 바탕으로 SSD 내부에 플래시 메모리 전용 온-칩 네트워크를 구성함으로써 성능을 극대화하는 상호-분리형(de-coupled) 구조를 제안했으며, 이를 통해 SSD의 프론트-엔드 설계와 백-엔드 설계의 상호 의존도를 줄여 독립적으로 설계하고 조립 가능한 ‘조립형 SSD’를 개발했다.

※온-칩 네트워크(on-chip network): CPU/GPU등의 시스템 반도체 설계에 쓰이는 칩 내부의 요소에 대한 패킷-기반 연결구조를 말한다. 온-칩 네트워크는 고성능 시스템 반도체를 위한 필수적인 설계 요소중 하나로서 반도체칩의 규모가 증가할수록 더욱 중요해지는 특징이 있다.

김동준 교수팀이 개발한 조립형 SSD 시스템 구조는 내부 구성요소 중 SSD 컨트롤러 내부, 플래시 메모리 인터페이스를 기점으로 CPU에 가까운 부분을 프론트-엔드(front-end), 플래시 메모리에 가까운 부분을 백-엔드(back-end)로 구분하고, 백-엔드의 플래시 컨트롤러 사이 간 데이터 이동이 가능한 플래시 메모리 전용 온-칩 네트워크를 새롭게 구성해, 성능 감소를 최소화하는 상호-분리형 구조를 제안했다.

SSD를 구동하는 핵심 요소인 플래시 변환 계층의 일부 기능을 하드웨어로 가속하여 플래시 메모리가 갖는 한계를 능동적으로 극복할 수 있는 계기를 마련하였고 상호-분리형 구조는 플래시 변환 계층이 특정 플래시 메모리의 특성에 국한되지 않고, 프론트-엔드 설계와 백-엔드 설계를 독립적으로 수행하는 설계의 용이성을 가지는 점이 ‘조립형’ SSD 구조의 장점이라고 밝혔다. 이를 통해, 기존 시스템 대비 응답시간을 31배 줄일 수 있었고 SSD 불량 블록 관리기법에도 적용해 약 23%의 SSD 수명을 연장할 수 있다고 연구팀 관계자는 설명했다.

전기및전자공학부 김지호 박사과정이 제1 저자, 전기및전자공학부 정명수 교수가 공동 저자로 참여한 이번 연구는 미국 플로리다주 올랜도에서 열리는 컴퓨터 구조 분야 최우수 국제 학술대회인 `제50회 국제 컴퓨터 구조 심포지엄(50th IEEE/ACM International Symposium on Computer Architecture, ISCA 2023)'에서 6월 19일 발표될 예정이다. (논문명: Decoupled SSD: Rethinking SSD Architecture through Network-based Flash Controllers).

연구를 주도한 김동준 교수는 “이번 연구는 기존의 SSD가 가지는 구조적 한계를 규명했다는 점과 CPU와 같은 시스템 메모리 반도체 중심의 온-칩 네트워크 기술을 적용해 하드웨어가 능동적으로 필요한 일을 수행할 수 있다는 점에서 의의가 있으며 차세대 고성능 SSD 시장에 기여할 것으로 보인다”며, “상호-분리형 구조는 수명연장을 위해서도 능동적으로 동작하는 SSD 구조로써 그 가치가 성능에만 국한되지 않아 다양한 쓰임새를 가진다며”연구의 의의를 설명했다.

이번 연구는 컴퓨터 시스템 저장장치 분야의 저명한 연구자인 KAIST 정명수 교수와 컴퓨터 구조 및 인터커넥션 네트워크(Interconnection Network) 분야의 권위자인 김동준 교수, 두 세계적인 연구자의 융합연구를 통해 이루어낸 연구라는 의미가 있다고 관계자는 설명했다.

한편 이번 연구는 한국연구재단, 삼성전자, 반도체설계교육센터(IDEC), 정보통신기획평가원 차세대지능형반도체기술개발사업의 지원을 받아 수행됐다.

2023.06.15 조회수 7686 -

111배 빠른 검색엔진용 CXL 3.0 기반 AI반도체 세계 최초 개발

최근 각광받고 있는 이미지 검색, 데이터베이스, 추천 시스템, 광고 등의 서비스들은 마이크로소프트, 메타, 알리바바 등의 글로벌 IT 기업들에서 활발히 제공되고 있다. 하지만 실제 서비스에서 사용되는 데이터 셋은 크기가 매우 커, 많은 양의 메모리를 요구하여 기존 시스템에서는 추가할 수 있는 메모리 용량에 제한이 있어 이러한 요구사항을 만족할 수 없었다.

우리 대학 전기및전자공학부 정명수 교수 연구팀(컴퓨터 아키텍처 및 메모리 시스템 연구실)에서 대용량으로 메모리 확장이 가능한 컴퓨트 익스프레스 링크 3.0 기술(Compute eXpress Link, 이하 CXL)을 활용해 검색 엔진을 위한 AI 반도체를 세계 최초로 개발했다고 25일 밝혔다.

최근 검색 서비스에서 사용되는 알고리즘은 근사 근접 이웃 탐색(Approximate Nearest Neighbor Search, ANNS)으로 어떤 데이터든지 특징 벡터로 표현할 수 있다. 특징 벡터란 데이터가 가지는 특징들 각각을 숫자로 표현해 나열한 것으로, 이들 사이의 거리를 통해 우리는 데이터 간의 유사도를 구할 수 있다. 하지만 벡터 데이터 용량이 매우 커서 이를 압축해 메모리에 적재하는 압축 방식과 메모리보다 큰 용량과 느린 속도를 가지는 저장 장치를 사용하는 스토리지 방식(마이크로소프트에서 사용 중)이 사용되어 왔다. 하지만 이들 각각은 낮은 정확도와 성능을 가지는 문제가 있었다.

이에 정명수 교수 연구팀은 메모리 확장의 제한이라는 근본적인 문제를 해결하기 위해 CXL이라는 기술에 주목했다. CXL은 CPU-장치 간 연결을 위한 프로토콜로, 가속기 및 메모리 확장기의 고속 연결을 제공한다. 또한 CXL 스위치를 통해 여러 대의 메모리 확장기를 하나의 포트에 연결할 수 있는 확장성을 제공한다. 하지만 CXL을 통한 메모리 확장은 로컬 메모리와 비교해 메모리 접근 시간이 증가하는 단점을 가지고 있다.

데이터를 책으로 비유하자면 기존 시스템은 집에 해당하는 CPU 크기의 제한으로 서재(메모리 용량)를 무한정 늘릴 수 없어, 보관할 수 있는 책 개수에 제한이 있는 것이다. 이에 압축 방식은 책의 내용을 압축하여 더 많은 책을 보관하는 방법이고, 스토리지 방식은 필요한 책들을 거리가 먼 도서관에서 구해오는 것과 비슷하다. CXL을 통한 메모리 확장은 집 옆에 창고를 지어 책을 보관하는 것으로 이해될 수 있다.

연구진이 개발한 AI 반도체(CXL-ANNS)는 CXL 스위치와 CXL 메모리 확장기를 사용해 근사 근접 이웃 탐색에서 필요한 모든 데이터를 메모리에 적재할 수 있어 정확도를 높이고 성능 감소를 없앴다. 또한 근사 근접 이웃 탐색의 특징을 활용해 데이터 근처 처리 기법과 지역성을 활용한 데이터 배치 기법으로 CXL-ANNS의 성능을 한 단계 향상했다. 이는 마치 창고 스스로가 필요한 책들의 내용을 요약하고 정리해 전달하고, 자주 보는 책들은 서재에 배치해 집과 창고를 오가는 시간을 줄이는 것과 유사하다.

연구진은 CXL-ANNS의 프로토타입을 자체 제작해 실효성을 확인하고, CXL-ANNS 성능을 기존 연구들과 비교했다. 마이크로소프트, 메타, 얀덱스 등의 글로벌 IT 기업에서 공개한 검색 데이터 셋을 사용한 근사 근접 이웃 탐색의 성능 비교에서 CXL-ANNS는 기존 연구들 대비 평균 111배 성능 향상이 있었다. 특히, 마이크로소프트의 상용화된 서비스에서 사용되는 방식과 비교하였을 때 92배의 성능 향상을 보여줬다.

정명수 교수는 "이번에 개발한 CXL-ANNS는 기존 검색 엔진의 문제였던 메모리 용량 제한 문제를 해결하고, CXL 기반의 메모리 확장이 실제 적용될 때 발생하는 메모리 접근 시간 지연 문제를 해결했다ˮ며, “제안하는 CXL 기반 메모리 확장과 데이터 근처 처리 가속의 패러다임은 검색 엔진뿐만 아니라 빅 데이터가 필요한 고성능 컴퓨팅, 유전자 탐색, 영상 처리 등의 다양한 분야에도 적용할 수 있다ˮ라고 말했다.

이번 연구는 미국 보스턴에서 오는 7월에 열릴 시스템 분야 최우수 학술대회인 유즈닉스 연례 회의 `USENIX Annual Technical Conference, 2023'에 ‘CXL-ANNS’이라는 이름으로 발표된 예정이다. (논문명: CXL-ANNS: Software-Hardware Collaborative Memory Disaggregation and Computation for Billion-Scale Approximate Nearest Neighbor Search)

한편 해당 연구는 파네시아(http://panmnesia.com)의 지원을 받아 진행됐다.

2023.05.25 조회수 8679

111배 빠른 검색엔진용 CXL 3.0 기반 AI반도체 세계 최초 개발

최근 각광받고 있는 이미지 검색, 데이터베이스, 추천 시스템, 광고 등의 서비스들은 마이크로소프트, 메타, 알리바바 등의 글로벌 IT 기업들에서 활발히 제공되고 있다. 하지만 실제 서비스에서 사용되는 데이터 셋은 크기가 매우 커, 많은 양의 메모리를 요구하여 기존 시스템에서는 추가할 수 있는 메모리 용량에 제한이 있어 이러한 요구사항을 만족할 수 없었다.

우리 대학 전기및전자공학부 정명수 교수 연구팀(컴퓨터 아키텍처 및 메모리 시스템 연구실)에서 대용량으로 메모리 확장이 가능한 컴퓨트 익스프레스 링크 3.0 기술(Compute eXpress Link, 이하 CXL)을 활용해 검색 엔진을 위한 AI 반도체를 세계 최초로 개발했다고 25일 밝혔다.

최근 검색 서비스에서 사용되는 알고리즘은 근사 근접 이웃 탐색(Approximate Nearest Neighbor Search, ANNS)으로 어떤 데이터든지 특징 벡터로 표현할 수 있다. 특징 벡터란 데이터가 가지는 특징들 각각을 숫자로 표현해 나열한 것으로, 이들 사이의 거리를 통해 우리는 데이터 간의 유사도를 구할 수 있다. 하지만 벡터 데이터 용량이 매우 커서 이를 압축해 메모리에 적재하는 압축 방식과 메모리보다 큰 용량과 느린 속도를 가지는 저장 장치를 사용하는 스토리지 방식(마이크로소프트에서 사용 중)이 사용되어 왔다. 하지만 이들 각각은 낮은 정확도와 성능을 가지는 문제가 있었다.

이에 정명수 교수 연구팀은 메모리 확장의 제한이라는 근본적인 문제를 해결하기 위해 CXL이라는 기술에 주목했다. CXL은 CPU-장치 간 연결을 위한 프로토콜로, 가속기 및 메모리 확장기의 고속 연결을 제공한다. 또한 CXL 스위치를 통해 여러 대의 메모리 확장기를 하나의 포트에 연결할 수 있는 확장성을 제공한다. 하지만 CXL을 통한 메모리 확장은 로컬 메모리와 비교해 메모리 접근 시간이 증가하는 단점을 가지고 있다.

데이터를 책으로 비유하자면 기존 시스템은 집에 해당하는 CPU 크기의 제한으로 서재(메모리 용량)를 무한정 늘릴 수 없어, 보관할 수 있는 책 개수에 제한이 있는 것이다. 이에 압축 방식은 책의 내용을 압축하여 더 많은 책을 보관하는 방법이고, 스토리지 방식은 필요한 책들을 거리가 먼 도서관에서 구해오는 것과 비슷하다. CXL을 통한 메모리 확장은 집 옆에 창고를 지어 책을 보관하는 것으로 이해될 수 있다.

연구진이 개발한 AI 반도체(CXL-ANNS)는 CXL 스위치와 CXL 메모리 확장기를 사용해 근사 근접 이웃 탐색에서 필요한 모든 데이터를 메모리에 적재할 수 있어 정확도를 높이고 성능 감소를 없앴다. 또한 근사 근접 이웃 탐색의 특징을 활용해 데이터 근처 처리 기법과 지역성을 활용한 데이터 배치 기법으로 CXL-ANNS의 성능을 한 단계 향상했다. 이는 마치 창고 스스로가 필요한 책들의 내용을 요약하고 정리해 전달하고, 자주 보는 책들은 서재에 배치해 집과 창고를 오가는 시간을 줄이는 것과 유사하다.

연구진은 CXL-ANNS의 프로토타입을 자체 제작해 실효성을 확인하고, CXL-ANNS 성능을 기존 연구들과 비교했다. 마이크로소프트, 메타, 얀덱스 등의 글로벌 IT 기업에서 공개한 검색 데이터 셋을 사용한 근사 근접 이웃 탐색의 성능 비교에서 CXL-ANNS는 기존 연구들 대비 평균 111배 성능 향상이 있었다. 특히, 마이크로소프트의 상용화된 서비스에서 사용되는 방식과 비교하였을 때 92배의 성능 향상을 보여줬다.

정명수 교수는 "이번에 개발한 CXL-ANNS는 기존 검색 엔진의 문제였던 메모리 용량 제한 문제를 해결하고, CXL 기반의 메모리 확장이 실제 적용될 때 발생하는 메모리 접근 시간 지연 문제를 해결했다ˮ며, “제안하는 CXL 기반 메모리 확장과 데이터 근처 처리 가속의 패러다임은 검색 엔진뿐만 아니라 빅 데이터가 필요한 고성능 컴퓨팅, 유전자 탐색, 영상 처리 등의 다양한 분야에도 적용할 수 있다ˮ라고 말했다.

이번 연구는 미국 보스턴에서 오는 7월에 열릴 시스템 분야 최우수 학술대회인 유즈닉스 연례 회의 `USENIX Annual Technical Conference, 2023'에 ‘CXL-ANNS’이라는 이름으로 발표된 예정이다. (논문명: CXL-ANNS: Software-Hardware Collaborative Memory Disaggregation and Computation for Billion-Scale Approximate Nearest Neighbor Search)

한편 해당 연구는 파네시아(http://panmnesia.com)의 지원을 받아 진행됐다.

2023.05.25 조회수 8679 -

반도체 소자 내 과열 해결방법 제시

최근 반도체 소자의 소형화로 인해 과열점(hot spot)에서 발생한 열이 효과적으로 분산되지 않아 소자의 신뢰성과 내구성이 저하되고 있다. 기존의 열관리 기술만으로는 심각해지는 발열 문제를 관리하는 데 한계가 있으며, 소자가 더욱 집적화됨에 따라 전통적 열관리 기술에서 탈피해 극한 스케일에서의 열전달 현상에 대한 근본적 이해를 바탕으로 한 접근이 필요하다. 기판 위에 증착된 금속 박막에서 발생하는 표면파에 의한 새로운 열전달 방식을 발견해 해결책을 제시하여 화제다.

우리 대학 기계공학과 이봉재 교수 연구팀이 세계 최초로 기판 위에 증착된 금속 박막에서 ‘표면 플라즈몬 폴라리톤’에 의해 발생하는 새로운 열전달 모드를 측정하는 데 성공했다고 밝혔다.

☞ 표면 플라즈몬 폴라리톤: 유전체와 금속의 경계면의 전자기장과 금속 표면의 자유 전자가 집단적으로 진동하는 유사 입자들이 강하게 상호작용한 결과로, 금속 표면에 형성되는 표면파(surface wave)를 의미한다.

연구팀은 나노 스케일 두께의 금속 박막에서 열확산을 개선하기 위해 금속과 유전체 경계면에서 발생하는 표면파인 표면 플라즈몬 폴라리톤을 활용했다. 이 새로운 열전달 모드는 기판에 금속 박막을 증착하면 발생하기 때문에, 소자 제작과정에 활용성이 높으며 넓은 면적에 제작이 가능하다는 장점이 있다. 연구팀은 반경이 약 3cm인 100나노미터 두께의 티타늄 박막에서 발생하는 표면파에 의해 열전도도가 약 25% 증가함을 보였다.

연구를 주도한 이봉재 교수는 "이번 연구의 의의는 공정난이도가 낮은 기판 위에 증착된 금속 박막에서 일어나는 표면파에 의한 새로운 열전달 모드를 세계 최초로 규명한 것으로, 이는 초고발열 반도체 소자 내 과열점 바로 근처에서 효과적으로 열을 분산시킬 수 있는 나노스케일 열 분산기(heat spreader)로 응용 가능하다ˮ고 말했다.

연구팀의 연구는 나노스케일 두께의 박막에서 열을 평면 방향으로 빠르게 분산시키는데 적용될 수 있다는 점에서 향후 고성능 반도체 소자 개발에 시사하는 바가 크다. 특히, 나노스케일 두께에서는 경계 산란에 의해 박막의 열전도도가 감소하는데, 연구팀이 규명한 이 새로운 열전달 모드는 오히려 나노스케일 두께에서 효과적인 열전달을 가능하게 해 반도체 소자 단위 열관리의 근본적인 문제를 해결해 줄 것으로 기대된다.

이번 연구는 국제학술지 `피지컬 리뷰 레터스(Physical Review Letters)'에 지난 4월 26일 字에 온라인 게재됐으며, 편집자 추천 논문(Editors' Suggestion)에 선정됐다. 한편 이번 연구는 한국연구재단의 기초연구실 지원사업의 지원을 받아 수행됐다.

2023.05.18 조회수 9466

반도체 소자 내 과열 해결방법 제시

최근 반도체 소자의 소형화로 인해 과열점(hot spot)에서 발생한 열이 효과적으로 분산되지 않아 소자의 신뢰성과 내구성이 저하되고 있다. 기존의 열관리 기술만으로는 심각해지는 발열 문제를 관리하는 데 한계가 있으며, 소자가 더욱 집적화됨에 따라 전통적 열관리 기술에서 탈피해 극한 스케일에서의 열전달 현상에 대한 근본적 이해를 바탕으로 한 접근이 필요하다. 기판 위에 증착된 금속 박막에서 발생하는 표면파에 의한 새로운 열전달 방식을 발견해 해결책을 제시하여 화제다.

우리 대학 기계공학과 이봉재 교수 연구팀이 세계 최초로 기판 위에 증착된 금속 박막에서 ‘표면 플라즈몬 폴라리톤’에 의해 발생하는 새로운 열전달 모드를 측정하는 데 성공했다고 밝혔다.

☞ 표면 플라즈몬 폴라리톤: 유전체와 금속의 경계면의 전자기장과 금속 표면의 자유 전자가 집단적으로 진동하는 유사 입자들이 강하게 상호작용한 결과로, 금속 표면에 형성되는 표면파(surface wave)를 의미한다.

연구팀은 나노 스케일 두께의 금속 박막에서 열확산을 개선하기 위해 금속과 유전체 경계면에서 발생하는 표면파인 표면 플라즈몬 폴라리톤을 활용했다. 이 새로운 열전달 모드는 기판에 금속 박막을 증착하면 발생하기 때문에, 소자 제작과정에 활용성이 높으며 넓은 면적에 제작이 가능하다는 장점이 있다. 연구팀은 반경이 약 3cm인 100나노미터 두께의 티타늄 박막에서 발생하는 표면파에 의해 열전도도가 약 25% 증가함을 보였다.

연구를 주도한 이봉재 교수는 "이번 연구의 의의는 공정난이도가 낮은 기판 위에 증착된 금속 박막에서 일어나는 표면파에 의한 새로운 열전달 모드를 세계 최초로 규명한 것으로, 이는 초고발열 반도체 소자 내 과열점 바로 근처에서 효과적으로 열을 분산시킬 수 있는 나노스케일 열 분산기(heat spreader)로 응용 가능하다ˮ고 말했다.

연구팀의 연구는 나노스케일 두께의 박막에서 열을 평면 방향으로 빠르게 분산시키는데 적용될 수 있다는 점에서 향후 고성능 반도체 소자 개발에 시사하는 바가 크다. 특히, 나노스케일 두께에서는 경계 산란에 의해 박막의 열전도도가 감소하는데, 연구팀이 규명한 이 새로운 열전달 모드는 오히려 나노스케일 두께에서 효과적인 열전달을 가능하게 해 반도체 소자 단위 열관리의 근본적인 문제를 해결해 줄 것으로 기대된다.

이번 연구는 국제학술지 `피지컬 리뷰 레터스(Physical Review Letters)'에 지난 4월 26일 字에 온라인 게재됐으며, 편집자 추천 논문(Editors' Suggestion)에 선정됐다. 한편 이번 연구는 한국연구재단의 기초연구실 지원사업의 지원을 받아 수행됐다.

2023.05.18 조회수 9466