%EC%A0%84%EC%9E%90%EC%86%8C%EC%9E%90

-

도장 찍듯이 자유롭게 그래핀 옮기는 기술 개발

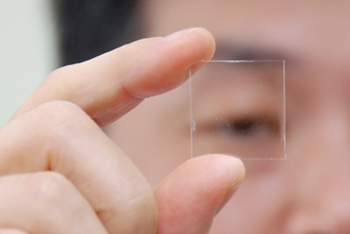

우리 학교 전기및전자공학과 최성율 교수 연구팀이 단원자층 그래핀을 금속촉매기판에서 직접 떼어내는 동시에 원하는 기판에 도장을 찍듯 자유롭게 옮길 수 있는 기술을 개발하는데 성공했다.

이 기술을 활용하면 기존의 직접박리 기반 전사공정으로 달성하기 어려웠던 그래핀 박막 적층, 구조물 표면이나 유연한 기판으로 전사, 4인치 웨이퍼 크기의 대면적 전사 등이 가능해진다. 향후 웨어러블 스마트기기 등 다양한 분야에 사용되는 그래핀 전자소자 상용화에 활용될 전망이다.

그래핀을 원하는 기판으로 옮기기 위해 현재 가장 널리 사용하는 방법인 습식전사법은 전사과정 중에 그래핀이 물리적으로 손상되고 표면이 오염 될 수 있어 전사된 그래핀의 전기적 특성이 심각하게 훼손될 수 있다는 단점이 있다.

최 교수 연구팀은 금속촉매기판 위에 성장된 그래핀을 수용성 고분자 용액으로 처리한 후 동일한 수용성 고분자 지지층을 그 위에 형성시켰다. 이 과정을 통해 지지층과 그래핀 사이에 강한 결합력이 형성되고 그 후 지지층을 탄성체 스탬프로 떼어내면 지지층과 함께 그래핀이 금속촉매기판으로부터 분리된다.

이렇게 분리된 그래핀은 탄성체 스탬프에 고립상태로 존재하기 때문에 원하는 기판 어디에든 도장 찍어내듯 자유롭게 옮길 수 있다. 또 금속촉매기판을 재활용 할 수 있고 유해한 화학물질을 전혀 사용하지 않기 때문에 친환경적인 전사법 이라는 장점도 가지고 있다.

최 교수는 이번 연구에 대해 “개발된 그래핀 전사방법은 그 공정이 범용적이고 대면적 전사도 가능하므로 그래핀 전자소자 상용화에 기여할 수 있을 것”이라며 “이 방법이 가지고 있는 높은 전사 자유도로 인해 향후 그래핀과 2차원 소재 접합 나노소자 구현에도 다양하게 활용될 것으로 기대된다”고 연구의의를 밝혔다.

이번 연구는 KAIST 전기및전자공학과 최성율 교수와 양상윤 연구교수가 주도하고 같은 과 조병진 교수, 한국전자통신연구원 최춘기 박사가 참여했으며, 미래창조과학부가 추진하는 글로벌 프론티어 사업인 ‘나노기반 소프트일렉트로닉스 연구단’의 지원으로 수행됐다.

연구 결과는 나노 및 마이크로 과학 분야의 국제 학술지 스몰(small) 1월 14일자 표지논문으로 게재됐다. 끝.

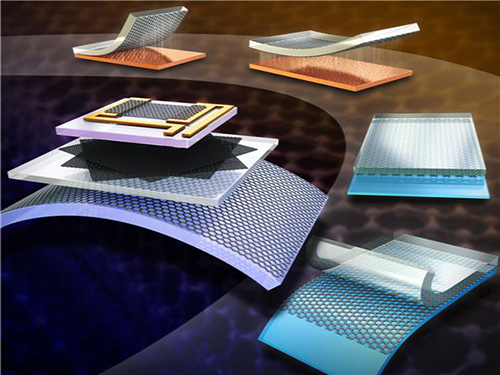

그림1. 본 연구결과를 설명하는 Small紙의 2015년 1월 14일자 표지 사진

그림2. 본 연구에서 개발된 ‘높은 자유도를 갖는 그래핀 직접박리/전사법’

그림3. 개발된 전사법으로 전사된 그래핀: (좌) 단원자층 그래핀을 3번 반복 전사하여 얻은 3층 그래핀 (3-layerd graphene), (우) 그래핀 트랜지스터 제작을 위해 금속 전극 구조물 표면에 전사한 그래핀

그림4. 대면적 전사된 그래핀: (좌) 4인치 실리콘 웨이퍼에 전사된 그래핀, (우) 플라스틱 (polyethersulfone, PES) 유연기판에 전사된 그래핀 (크기 7cm x 7cm)

2015.01.19 조회수 17997

도장 찍듯이 자유롭게 그래핀 옮기는 기술 개발

우리 학교 전기및전자공학과 최성율 교수 연구팀이 단원자층 그래핀을 금속촉매기판에서 직접 떼어내는 동시에 원하는 기판에 도장을 찍듯 자유롭게 옮길 수 있는 기술을 개발하는데 성공했다.

이 기술을 활용하면 기존의 직접박리 기반 전사공정으로 달성하기 어려웠던 그래핀 박막 적층, 구조물 표면이나 유연한 기판으로 전사, 4인치 웨이퍼 크기의 대면적 전사 등이 가능해진다. 향후 웨어러블 스마트기기 등 다양한 분야에 사용되는 그래핀 전자소자 상용화에 활용될 전망이다.

그래핀을 원하는 기판으로 옮기기 위해 현재 가장 널리 사용하는 방법인 습식전사법은 전사과정 중에 그래핀이 물리적으로 손상되고 표면이 오염 될 수 있어 전사된 그래핀의 전기적 특성이 심각하게 훼손될 수 있다는 단점이 있다.

최 교수 연구팀은 금속촉매기판 위에 성장된 그래핀을 수용성 고분자 용액으로 처리한 후 동일한 수용성 고분자 지지층을 그 위에 형성시켰다. 이 과정을 통해 지지층과 그래핀 사이에 강한 결합력이 형성되고 그 후 지지층을 탄성체 스탬프로 떼어내면 지지층과 함께 그래핀이 금속촉매기판으로부터 분리된다.

이렇게 분리된 그래핀은 탄성체 스탬프에 고립상태로 존재하기 때문에 원하는 기판 어디에든 도장 찍어내듯 자유롭게 옮길 수 있다. 또 금속촉매기판을 재활용 할 수 있고 유해한 화학물질을 전혀 사용하지 않기 때문에 친환경적인 전사법 이라는 장점도 가지고 있다.

최 교수는 이번 연구에 대해 “개발된 그래핀 전사방법은 그 공정이 범용적이고 대면적 전사도 가능하므로 그래핀 전자소자 상용화에 기여할 수 있을 것”이라며 “이 방법이 가지고 있는 높은 전사 자유도로 인해 향후 그래핀과 2차원 소재 접합 나노소자 구현에도 다양하게 활용될 것으로 기대된다”고 연구의의를 밝혔다.

이번 연구는 KAIST 전기및전자공학과 최성율 교수와 양상윤 연구교수가 주도하고 같은 과 조병진 교수, 한국전자통신연구원 최춘기 박사가 참여했으며, 미래창조과학부가 추진하는 글로벌 프론티어 사업인 ‘나노기반 소프트일렉트로닉스 연구단’의 지원으로 수행됐다.

연구 결과는 나노 및 마이크로 과학 분야의 국제 학술지 스몰(small) 1월 14일자 표지논문으로 게재됐다. 끝.

그림1. 본 연구결과를 설명하는 Small紙의 2015년 1월 14일자 표지 사진

그림2. 본 연구에서 개발된 ‘높은 자유도를 갖는 그래핀 직접박리/전사법’

그림3. 개발된 전사법으로 전사된 그래핀: (좌) 단원자층 그래핀을 3번 반복 전사하여 얻은 3층 그래핀 (3-layerd graphene), (우) 그래핀 트랜지스터 제작을 위해 금속 전극 구조물 표면에 전사한 그래핀

그림4. 대면적 전사된 그래핀: (좌) 4인치 실리콘 웨이퍼에 전사된 그래핀, (우) 플라스틱 (polyethersulfone, PES) 유연기판에 전사된 그래핀 (크기 7cm x 7cm)

2015.01.19 조회수 17997 -

휘어지는 고집적 반도체회로 구현

- 차세대 유연 스마트기기의 두뇌 상용화 길 열어 -

우리 학교 신소재공학과 이건재 교수팀이 입는 컴퓨터 및 플렉시블 디스플레이에서 가장 핵심적인 역할을 하는 유연한 고집적회로(LSI)를 구현하는데 성공했다.

자유롭게 휘어지는 스마트폰과 컴퓨터를 제작하기 위해서는 높은 집적도의 반도체회로, 즉 모바일 기기의 두뇌인 애플리케이션 프로세서(AP), 고용량 메모리 및 무선통신소자의 유연화가 필수적이다.

지금까지 플렉시블 디스플레이 구동에 필요한 박막트랜지스터(TFT)와 여러 유연소재들을 개발하는 연구는 활발히 진행되고 있다. 그러나 수천 개 이상의 고성능 나노반도체를 연결해 대량의 정보를 처리하고 저장할 수 있는 유연 고집적회로를 제작하지 못했다. 따라서 전체가 자유자재로 휘어지는 유연한 스마트기기 등 입을 수 있는 컴퓨터의 상용화에 어려움이 있었다.

이건재 교수팀은 고집적 무선통신소자를 단결정 실리콘에 형성한 뒤 100nm(나노미터) 두께의 매우 얇은 실리콘 칩의 회로를 뜯어내 플라스틱 기판위에 안정적으로 옮김으로써, 자유자재로 구부릴 수 있는 반도체회로를 구현했다.

이건재 교수는 “이번에 나노두께의 얇은 실리콘 소재로 개발한 반도체회로는 유연하면서도 고집적 고성능을 유지할 수 있고, 곧 상용화될 플렉시블 전자소자에 적용될 수 있을 뿐만 아니라, 인체 친화적 유연한 액정폴리머 소재위에 구현하였기 때문에 인체내부의 좁고 굴곡진 틈에 삽입할 수 있어서, 최근 미국 FDA가 승인한 인공망막의 통신 및 정보처리 기기에 적용하는 등 삶의 질을 향상시키는 데에도 기여할 수 있을 것이다"라고 말했다.

또한 이번 연구의 공저자로 참여한 KAIST 전기및전자공학과 이귀로 교수(나노종합기술원 원장)는 “이번성과는 세계 500조 규모의 반도체 및 디스플레이 시장에서 휘어지는 유연 고집적 회로로 패러다임이 바뀌는 시기에 개발된 핵심 원천기술”이라며 “향후 상용화를 위한 정부의 지원이 뒷받침 된다면 세계 시장에서 앞서가고 있는 한국 스마트폰, 반도체, 디스플레이 산업을 한 단계 더 업그레이드시켜 미래 먹거리로써 창조경제에도 이바지할 수 있을 것”이라고 평가했다.

이건재 교수는 현재 나노종합기술원, 한국기계연구원과 공동으로 이번 연구 결과물인 고집적 유연 반도체 회로를 롤투롤(Roll-to-Roll) 방식으로 양산하는 연구를 계획하고 있다.

한편, 이번 연구는 미국 화학회가 발행하는 나노과학기술(NT) 분야의 세계적 권위지인 ACS Nano 4월 25일자 온라인 판에 게재됐다.

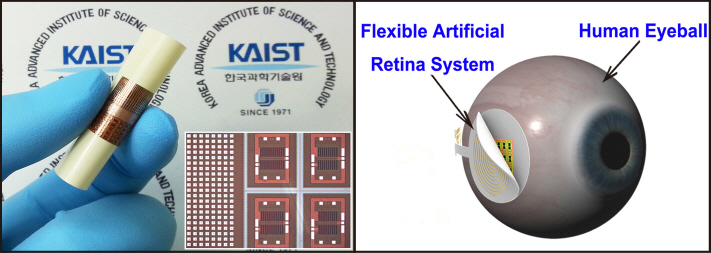

휘어지는 고집적 반도체회로의 모습(좌), 얇고 유연한 고집적 통신소자를 적용한 인공망막의 모습(우)

유튜브 링크:http://www.youtube.com/watch?v=5PpbM7m2PPs&feature=youtu.be

2013.05.07 조회수 19486

휘어지는 고집적 반도체회로 구현

- 차세대 유연 스마트기기의 두뇌 상용화 길 열어 -

우리 학교 신소재공학과 이건재 교수팀이 입는 컴퓨터 및 플렉시블 디스플레이에서 가장 핵심적인 역할을 하는 유연한 고집적회로(LSI)를 구현하는데 성공했다.

자유롭게 휘어지는 스마트폰과 컴퓨터를 제작하기 위해서는 높은 집적도의 반도체회로, 즉 모바일 기기의 두뇌인 애플리케이션 프로세서(AP), 고용량 메모리 및 무선통신소자의 유연화가 필수적이다.

지금까지 플렉시블 디스플레이 구동에 필요한 박막트랜지스터(TFT)와 여러 유연소재들을 개발하는 연구는 활발히 진행되고 있다. 그러나 수천 개 이상의 고성능 나노반도체를 연결해 대량의 정보를 처리하고 저장할 수 있는 유연 고집적회로를 제작하지 못했다. 따라서 전체가 자유자재로 휘어지는 유연한 스마트기기 등 입을 수 있는 컴퓨터의 상용화에 어려움이 있었다.

이건재 교수팀은 고집적 무선통신소자를 단결정 실리콘에 형성한 뒤 100nm(나노미터) 두께의 매우 얇은 실리콘 칩의 회로를 뜯어내 플라스틱 기판위에 안정적으로 옮김으로써, 자유자재로 구부릴 수 있는 반도체회로를 구현했다.

이건재 교수는 “이번에 나노두께의 얇은 실리콘 소재로 개발한 반도체회로는 유연하면서도 고집적 고성능을 유지할 수 있고, 곧 상용화될 플렉시블 전자소자에 적용될 수 있을 뿐만 아니라, 인체 친화적 유연한 액정폴리머 소재위에 구현하였기 때문에 인체내부의 좁고 굴곡진 틈에 삽입할 수 있어서, 최근 미국 FDA가 승인한 인공망막의 통신 및 정보처리 기기에 적용하는 등 삶의 질을 향상시키는 데에도 기여할 수 있을 것이다"라고 말했다.

또한 이번 연구의 공저자로 참여한 KAIST 전기및전자공학과 이귀로 교수(나노종합기술원 원장)는 “이번성과는 세계 500조 규모의 반도체 및 디스플레이 시장에서 휘어지는 유연 고집적 회로로 패러다임이 바뀌는 시기에 개발된 핵심 원천기술”이라며 “향후 상용화를 위한 정부의 지원이 뒷받침 된다면 세계 시장에서 앞서가고 있는 한국 스마트폰, 반도체, 디스플레이 산업을 한 단계 더 업그레이드시켜 미래 먹거리로써 창조경제에도 이바지할 수 있을 것”이라고 평가했다.

이건재 교수는 현재 나노종합기술원, 한국기계연구원과 공동으로 이번 연구 결과물인 고집적 유연 반도체 회로를 롤투롤(Roll-to-Roll) 방식으로 양산하는 연구를 계획하고 있다.

한편, 이번 연구는 미국 화학회가 발행하는 나노과학기술(NT) 분야의 세계적 권위지인 ACS Nano 4월 25일자 온라인 판에 게재됐다.

휘어지는 고집적 반도체회로의 모습(좌), 얇고 유연한 고집적 통신소자를 적용한 인공망막의 모습(우)

유튜브 링크:http://www.youtube.com/watch?v=5PpbM7m2PPs&feature=youtu.be

2013.05.07 조회수 19486 -

그래핀의 기계적 특성 세계 최초로 규명

- KAIST 박정영·김용현 교수 연구팀, 그래핀의 마찰력 제어기술 개발과 나노수준 마찰력이론 정립 -

- 나노분야 권위지 나노 레터스 6월 21일자 온라인판 게재 -

우리 대학 연구진이 차세대 ‘꿈의 신소재’로 불리는 그래핀의 기계적 특성을 밝히고 제어하는 데 성공했다.

우리 학교 EEWS대학원 박정영 교수가 나노과학기술대학원 김용현 교수와 공동으로 하나의 원자층으로 이루어진 그래핀을 불소화해 마찰력과 접착력을 제어하는 데 성공했다고 2일 밝혔다.

원자단위에서 그래핀에 대한 마찰력의 원리를 규명하고 제어하는 데 성공한 것은 이번 연구가 세계에서 처음인데 앞으로 나노 크기의 로봇 구동부 등 아주 미세한 부분의 윤활에 응용될 수 있을 것으로 기대된다.

그래핀은 구리보다 100배 이상 전기가 잘 통하면서도 구부려도 전기전도성이 유지돼 실리콘 반도체를 대체할 차세대 전자소자는 물론 휘어지는 디스플레이, 입는 컴퓨터 등 다양한 분야에 활용될 수 있어 ‘꿈의 신소재’로 불린다.

또 강철보다 200배 이상 강한 물성을 갖고 있어 기계 분야에도 응용가능성이 매우 높은 반면 마찰력과 접착력 등과 같은 기계적 성질에 대해서는 몇 가지 미해결 과제로 남아있었는데 이번 연구를 통해 상당부분 해소될 수 있을 것으로 전망된다.

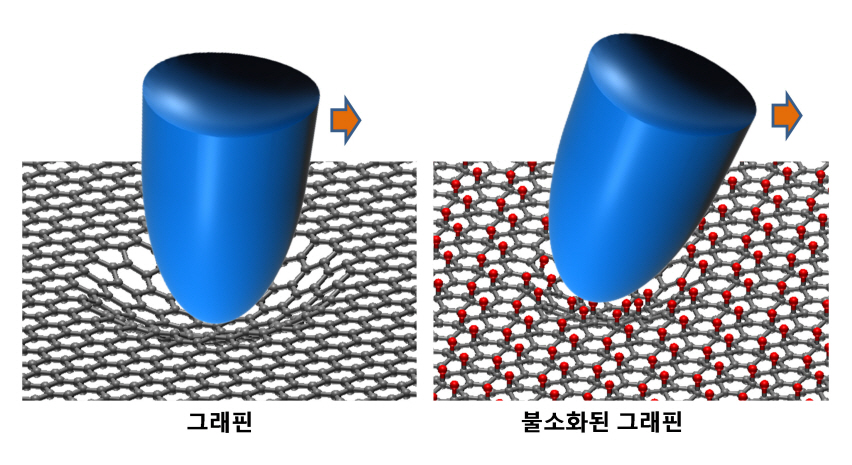

박 교수 연구팀은 그래핀을 플루오르화크세논(XeF₂) 가스에 넣고 열을 가해 하나의 원자층에 불소 결함을 갖고 있는 불소화된 개질 그래핀을 얻어냈다.

개질된 그래핀은 초고진공 원자력현미경에 넣고 마이크로 탐침을 사용, 시료의 표면을 스캔해 마찰력과 접착력 등의 역학적 특성을 측정했다.

연구팀은 실험 결과를 바탕으로 불소화된 그래핀은 기존보다 6배의 마찰력과 0.7배의 접착력을 나타내는 것을 밝혀냈다.

이와 함께 전기적인 측정을 통해 불소화를 확인하고 마찰력과 접착력의 원리를 분석해내 그래핀의 마찰력 변화에 대한 이론을 정립했다.

박정영 교수는 “꿈의 소재로 알려진 그래핀은 나노 스케일 기기의 구동부 윤활에 쓰일 수가 있어 이번 연구는 그래핀 기반의 작은 역학구동소자의 코팅 등의 응용을 가질 수 있다”고 말했다.

한편, 이번 연구 성과는 나노과학분야 권위 있는 학술지 ‘나노레터스(Nano Letters)" 6월 21일자 온라인판에 게재됐으며 교육과학기술부와 한국연구재단이 추진하는 WCU(세계수준의 연구중심대학)육성사업과 중견 연구자지원사업의 지원을 받았다.

2012.07.02 조회수 19946

그래핀의 기계적 특성 세계 최초로 규명

- KAIST 박정영·김용현 교수 연구팀, 그래핀의 마찰력 제어기술 개발과 나노수준 마찰력이론 정립 -

- 나노분야 권위지 나노 레터스 6월 21일자 온라인판 게재 -

우리 대학 연구진이 차세대 ‘꿈의 신소재’로 불리는 그래핀의 기계적 특성을 밝히고 제어하는 데 성공했다.

우리 학교 EEWS대학원 박정영 교수가 나노과학기술대학원 김용현 교수와 공동으로 하나의 원자층으로 이루어진 그래핀을 불소화해 마찰력과 접착력을 제어하는 데 성공했다고 2일 밝혔다.

원자단위에서 그래핀에 대한 마찰력의 원리를 규명하고 제어하는 데 성공한 것은 이번 연구가 세계에서 처음인데 앞으로 나노 크기의 로봇 구동부 등 아주 미세한 부분의 윤활에 응용될 수 있을 것으로 기대된다.

그래핀은 구리보다 100배 이상 전기가 잘 통하면서도 구부려도 전기전도성이 유지돼 실리콘 반도체를 대체할 차세대 전자소자는 물론 휘어지는 디스플레이, 입는 컴퓨터 등 다양한 분야에 활용될 수 있어 ‘꿈의 신소재’로 불린다.

또 강철보다 200배 이상 강한 물성을 갖고 있어 기계 분야에도 응용가능성이 매우 높은 반면 마찰력과 접착력 등과 같은 기계적 성질에 대해서는 몇 가지 미해결 과제로 남아있었는데 이번 연구를 통해 상당부분 해소될 수 있을 것으로 전망된다.

박 교수 연구팀은 그래핀을 플루오르화크세논(XeF₂) 가스에 넣고 열을 가해 하나의 원자층에 불소 결함을 갖고 있는 불소화된 개질 그래핀을 얻어냈다.

개질된 그래핀은 초고진공 원자력현미경에 넣고 마이크로 탐침을 사용, 시료의 표면을 스캔해 마찰력과 접착력 등의 역학적 특성을 측정했다.

연구팀은 실험 결과를 바탕으로 불소화된 그래핀은 기존보다 6배의 마찰력과 0.7배의 접착력을 나타내는 것을 밝혀냈다.

이와 함께 전기적인 측정을 통해 불소화를 확인하고 마찰력과 접착력의 원리를 분석해내 그래핀의 마찰력 변화에 대한 이론을 정립했다.

박정영 교수는 “꿈의 소재로 알려진 그래핀은 나노 스케일 기기의 구동부 윤활에 쓰일 수가 있어 이번 연구는 그래핀 기반의 작은 역학구동소자의 코팅 등의 응용을 가질 수 있다”고 말했다.

한편, 이번 연구 성과는 나노과학분야 권위 있는 학술지 ‘나노레터스(Nano Letters)" 6월 21일자 온라인판에 게재됐으며 교육과학기술부와 한국연구재단이 추진하는 WCU(세계수준의 연구중심대학)육성사업과 중견 연구자지원사업의 지원을 받았다.

2012.07.02 조회수 19946 -

누설전류의 원천적 차단 가능한 ‘20nm갭 기계식 나노집적소자’ 세계 최초 개발

- CPU, 메모리 적용 시 에너지 절감 年 7,480억원․329만톤의 CO2배출저감 효과 기대 -

고가의 반도체 기판 대신 저렴한 유리기판이나 플렉서블(flexible) 플라스틱 기판에도 적용이 가능하고, 3低(초저가․초저전력․초 저탄소) CPU를 실현할 수 있는 나노집적소자 원천 기술이 국내연구진에 의해 세계 최초로 개발되었다.

우리대학 전기 및 전자 공학과 윤준보 교수팀과 부설 나노종합팹센터(소장 이희철)는 공동연구를 통하여 세계 에서 가장 작은 이격거리를 가지는 “20nm갭 기계식 나노집적소자(3단자 나노전자 기계스위칭소자)”를 세계 최초로 개발하는데 성공했다고 밝혔다.

반도체로 만들어진 기존의 CPU는 반도체 특성을 활용하여 전기신호의 차폐를 제어함으로써 PC내에서 평균적으로 3.2W의 대기전력을 소모하고 있다. 업무용 PC 보급대수와 대기시간을 각각 1000만 대와 14시간으로 가정하면 대기전력은 년 163,520 MWh로 계산된다. 고리원자력발전소 1호기의 발전량(2007년 총 발전량 2,254,988 MWh) 7%에 해당하는 전력량이다.

이에 윤준보 교수팀은 나노종합팹의 첨단 장비․시설 등 인프라와 나노 전자기계 기술(Nano Electro Mechanical System, NEMS)을 적용하여, 트렌지스터와 동일한 역할을 수행하면서도 누설전류를 원천적으로 차단한 新개념 전자소자인 ‘기계식 나노집적 소자’를 개발했다.

본 소자의 핵심원리는 질화티타늄(TiN)으로 만든 3차원 나노구조물의 기계적인 움직임을 통해 기계적인 이격정도의 차이로 전기신호를 제어한다는 것이다. 대기 상태에서 누설전류를 원천적으로 차단하는 원리를 가지기 때문에, 이를 CPU에 적용하면 1W 미만의 대기전력을 가지는 CPU개발이 앞당겨 질 것으로 기대를 하고 있다.

사진설명: 20nm갭 기계식 나노집적 소자의 단면 사진

좌측- TEM (투사 전자 현미경) , 우측 - SEM (주사 전자 현미경)

또한, 저온 공정이 가능하기 때문에 기존의 반도체 회로 상부에 3차원으로 적층형 집적이 가능하고, 기존의 반도체를 만들던 단결정 실리콘보다 훨씬 저렴한 유리 기판이나 휘어지는 플라스틱 기판에서도 전자 스위치 소자를 형성할 수 있어, 초저가․초고성능․초저전력의 전자 회로를 만들 수 있다는 데 특징이 있다.

그리고, 무엇보다도 세계 최고 수준의 나노종합팹센터의 첨단 반도체 설비와 공정을 그대로 활용하여 본 소자의 핵심인 초미세 나노패턴 형성과 희생박막 형성 기술을 연구․실증했기 때문에, 상용화 실현 가능성이 매우 높다는 데 의의가 크다.

개발된 기계식 나노집적소자를 활용하여 대기전력 1W이하의 저전력 PC가 실현함으로써 기대되는 에너지 절감효과는 2010년 1,100GWh/年(1,210억원), 2020년 6,800GWh/年(7,480억원)에 이르고 각각 53만톤, 329만톤의 이산화탄소 배출량 억제효과를 가져올 수 있을 것으로 보인다.

또한, 기계식 나노집적소자의 시장 점유율을 전체 반도체 시장의 0.1%로만 잡더라도 시장규모가 2015년 3천 6백억원에 이를 것으로 전망하고 있다. 우주항공 장비와 통신용 소자 및 바이오소자 응용 등 관련 산업에 미치는 파급효과까지 고려하는 경우 그 경제적 부가가치는 매우 클 것으로 기대된다.

이번 연구결과는 12월 7일 미국 볼티모어에서 개막되는 국제 학술 회의인 “국제전자소자회의(International Electron Device Meeting, IEDM)”에서 발표될 예정으로 지난 50년간 반도체 소자를 이용하여 만들어 오던 초고집적회로(VLSI)에서 CMOS 반도체 소자가 극복 할 수 없었던 재료와 성능의 한계들을 극복할 수 있는 새로운 가능성을 제시했다는 것에 의미가 있다.

한편, 해당 기술과 관련하여 미국에 1건이 특허 등록되었으며 미국, 중국, 유럽, 일본 등에 4건의 후속 특허가 출원되어 있다. 국내에는 8건의 관련 특허 등록과 2건의 특허가 출원되어 있다.

나노종합팹센터 이희철 소장은 “나노전자 기계소자를 이용한 집적회로 기술은 2008년에서야 ITRS(세계반도체협회) 로드맵에 등재될 정도로 차세대 기술이며, 우리 기술진의 개발수준이 미국의 스탠포드대, UC버클리대학의 연구수준을 뛰어넘는 결과로 이번 기술 개발이 포스트-반도체 기술력을 선점할 수 있는 중요한 디딤돌이 될 것”이라고 내다보고 있다.

또, 연구개발에 주도적으로 참여한 이정언 박사과정은 “공동연구 개발을 통하여 얻은 기술은 실용화와 상용화를 목적으로 하고 있으며, 기술정보, 연구인력, 노하우 등 연구결과를 산업체에 제공하여 향후에 우리나라가 세계 차세대 반도체 시장에서 유리한 입지를 확보하는데 기여하고 싶다”고 앞으로의 계획을 밝혔다.

용어설명

○ 스위칭소자 : 전류를 on/off 시키는 장치, 스위치 장치를 조합하여 논리회로, 마이크로프로세서등 을 만들 수 있음.

○ 기계식 나노집적 소자 : 반도체 공정을 이용하여 만든 나노 크기의 기계장치로 전기신호에 의하여 제어되는 소자.

○ 3단자 스위칭 소자 : 3개의 단자로 구성된 전자 부품으로 1개의 단자에 인가된 전기신호로 나머지 2개의 단자의 단락 여부를 제어하는 전자 장치

○ 패키징 : 전자소자의 제품화를 위하여 기판상태에서 제작된 소자를 외부의 환경에 안정적인 상태가 되도록 최종적으로 마무리 하는 단계

○ 트랜지스터 : 규소나 저마늄으로 만들어진 반도체를 세 겹으로 접합하여 만든 전자회로로 전류나 전압흐름을 조절하여 증폭, 스위치 역할을 한다.

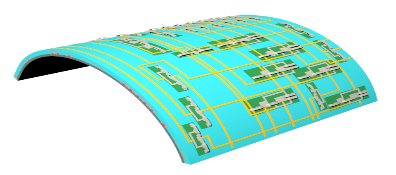

사진설명: 개발된 기계식 집적 소자를 활용한 미래형 전자 기판의 개념도

2009.12.07 조회수 24849

누설전류의 원천적 차단 가능한 ‘20nm갭 기계식 나노집적소자’ 세계 최초 개발

- CPU, 메모리 적용 시 에너지 절감 年 7,480억원․329만톤의 CO2배출저감 효과 기대 -

고가의 반도체 기판 대신 저렴한 유리기판이나 플렉서블(flexible) 플라스틱 기판에도 적용이 가능하고, 3低(초저가․초저전력․초 저탄소) CPU를 실현할 수 있는 나노집적소자 원천 기술이 국내연구진에 의해 세계 최초로 개발되었다.

우리대학 전기 및 전자 공학과 윤준보 교수팀과 부설 나노종합팹센터(소장 이희철)는 공동연구를 통하여 세계 에서 가장 작은 이격거리를 가지는 “20nm갭 기계식 나노집적소자(3단자 나노전자 기계스위칭소자)”를 세계 최초로 개발하는데 성공했다고 밝혔다.

반도체로 만들어진 기존의 CPU는 반도체 특성을 활용하여 전기신호의 차폐를 제어함으로써 PC내에서 평균적으로 3.2W의 대기전력을 소모하고 있다. 업무용 PC 보급대수와 대기시간을 각각 1000만 대와 14시간으로 가정하면 대기전력은 년 163,520 MWh로 계산된다. 고리원자력발전소 1호기의 발전량(2007년 총 발전량 2,254,988 MWh) 7%에 해당하는 전력량이다.

이에 윤준보 교수팀은 나노종합팹의 첨단 장비․시설 등 인프라와 나노 전자기계 기술(Nano Electro Mechanical System, NEMS)을 적용하여, 트렌지스터와 동일한 역할을 수행하면서도 누설전류를 원천적으로 차단한 新개념 전자소자인 ‘기계식 나노집적 소자’를 개발했다.

본 소자의 핵심원리는 질화티타늄(TiN)으로 만든 3차원 나노구조물의 기계적인 움직임을 통해 기계적인 이격정도의 차이로 전기신호를 제어한다는 것이다. 대기 상태에서 누설전류를 원천적으로 차단하는 원리를 가지기 때문에, 이를 CPU에 적용하면 1W 미만의 대기전력을 가지는 CPU개발이 앞당겨 질 것으로 기대를 하고 있다.

사진설명: 20nm갭 기계식 나노집적 소자의 단면 사진

좌측- TEM (투사 전자 현미경) , 우측 - SEM (주사 전자 현미경)

또한, 저온 공정이 가능하기 때문에 기존의 반도체 회로 상부에 3차원으로 적층형 집적이 가능하고, 기존의 반도체를 만들던 단결정 실리콘보다 훨씬 저렴한 유리 기판이나 휘어지는 플라스틱 기판에서도 전자 스위치 소자를 형성할 수 있어, 초저가․초고성능․초저전력의 전자 회로를 만들 수 있다는 데 특징이 있다.

그리고, 무엇보다도 세계 최고 수준의 나노종합팹센터의 첨단 반도체 설비와 공정을 그대로 활용하여 본 소자의 핵심인 초미세 나노패턴 형성과 희생박막 형성 기술을 연구․실증했기 때문에, 상용화 실현 가능성이 매우 높다는 데 의의가 크다.

개발된 기계식 나노집적소자를 활용하여 대기전력 1W이하의 저전력 PC가 실현함으로써 기대되는 에너지 절감효과는 2010년 1,100GWh/年(1,210억원), 2020년 6,800GWh/年(7,480억원)에 이르고 각각 53만톤, 329만톤의 이산화탄소 배출량 억제효과를 가져올 수 있을 것으로 보인다.

또한, 기계식 나노집적소자의 시장 점유율을 전체 반도체 시장의 0.1%로만 잡더라도 시장규모가 2015년 3천 6백억원에 이를 것으로 전망하고 있다. 우주항공 장비와 통신용 소자 및 바이오소자 응용 등 관련 산업에 미치는 파급효과까지 고려하는 경우 그 경제적 부가가치는 매우 클 것으로 기대된다.

이번 연구결과는 12월 7일 미국 볼티모어에서 개막되는 국제 학술 회의인 “국제전자소자회의(International Electron Device Meeting, IEDM)”에서 발표될 예정으로 지난 50년간 반도체 소자를 이용하여 만들어 오던 초고집적회로(VLSI)에서 CMOS 반도체 소자가 극복 할 수 없었던 재료와 성능의 한계들을 극복할 수 있는 새로운 가능성을 제시했다는 것에 의미가 있다.

한편, 해당 기술과 관련하여 미국에 1건이 특허 등록되었으며 미국, 중국, 유럽, 일본 등에 4건의 후속 특허가 출원되어 있다. 국내에는 8건의 관련 특허 등록과 2건의 특허가 출원되어 있다.

나노종합팹센터 이희철 소장은 “나노전자 기계소자를 이용한 집적회로 기술은 2008년에서야 ITRS(세계반도체협회) 로드맵에 등재될 정도로 차세대 기술이며, 우리 기술진의 개발수준이 미국의 스탠포드대, UC버클리대학의 연구수준을 뛰어넘는 결과로 이번 기술 개발이 포스트-반도체 기술력을 선점할 수 있는 중요한 디딤돌이 될 것”이라고 내다보고 있다.

또, 연구개발에 주도적으로 참여한 이정언 박사과정은 “공동연구 개발을 통하여 얻은 기술은 실용화와 상용화를 목적으로 하고 있으며, 기술정보, 연구인력, 노하우 등 연구결과를 산업체에 제공하여 향후에 우리나라가 세계 차세대 반도체 시장에서 유리한 입지를 확보하는데 기여하고 싶다”고 앞으로의 계획을 밝혔다.

용어설명

○ 스위칭소자 : 전류를 on/off 시키는 장치, 스위치 장치를 조합하여 논리회로, 마이크로프로세서등 을 만들 수 있음.

○ 기계식 나노집적 소자 : 반도체 공정을 이용하여 만든 나노 크기의 기계장치로 전기신호에 의하여 제어되는 소자.

○ 3단자 스위칭 소자 : 3개의 단자로 구성된 전자 부품으로 1개의 단자에 인가된 전기신호로 나머지 2개의 단자의 단락 여부를 제어하는 전자 장치

○ 패키징 : 전자소자의 제품화를 위하여 기판상태에서 제작된 소자를 외부의 환경에 안정적인 상태가 되도록 최종적으로 마무리 하는 단계

○ 트랜지스터 : 규소나 저마늄으로 만들어진 반도체를 세 겹으로 접합하여 만든 전자회로로 전류나 전압흐름을 조절하여 증폭, 스위치 역할을 한다.

사진설명: 개발된 기계식 집적 소자를 활용한 미래형 전자 기판의 개념도

2009.12.07 조회수 24849 -

박재우.유승협교수 산화티타늄 투명박막트랜지스터 독자기술 세계최초 개발

- 미국, 일본, 유럽에 특허출원, 관련 국제학회 발표예정

2002년에 개봉된 스티븐 스필버그 감독의 "마이너리티 리포트”(톰 크루즈 주연) 장면들 중에 보았던 투명디스플레이 구현이 꿈이 아니라 현실로 다가오고 있다.

‘꿈의 디스플레이’라 불리는 투명디스플레이, 에이엠올레드(AMOLED, 능동형 유기발광 다이오드) 디스플레이 및 플렉서블 디스플레이 등의 구동회로용으로 사용되는 투명박막트랜지스터(Transparent Thin Film Transistor) 기술이 국내 연구진에 의해 개발됐다.

전기전자공학과 박재우(朴在佑, 44) 교수와 유승협교수는 ㈜테크노세미켐, 삼성전자LCD총괄과 공동연구를 통해 미국, 일본 등이 원천특허를 보유하고 있는 산화아연(ZnO)기반 투명박막트랜지스터 기술에서 벗어나, 세계최초로 산화티타늄(TiO2)물질을 이용한 투명박막트랜지스터의 원천기술을 확보하는데 성공했다.

朴 교수팀은 미국, 일본 등과 기술특허분쟁이 일어나지 않을 뿐만 아니라 기존특허로 잡혀진 산화아연(ZnO) 물질에 포함된 In(인듐) 또는 Ga(갈륨)과 같은 희소성 금속을 사용하지 않고 지구상에 풍부한 금속자원을 이용한다는 원칙과 기존 반도체/디스플레이 산업용 대형 양산 장비로 검증 받은 화학기상증착(CVD, Chemical Vapor Deposition)법을 이용하여 낮은 온도에서 TiO2박막의 성막이 가능하게 함으로써 차세대 디스플레이의 대형화 가능성뿐만 아니라, 소다라임글래스(Soda-lime Glass)와 같은 저가 글라스기판 및 플렉서블 기판위에도 성막할 수 있는 원천 기술을 확보하는데 성공했다. 朴 교수팀은 미국, 일본이 보유한 원천기술이 스퍼터링 방식을 주로 사용하고 있으나 스퍼터링의 연속작업에 따른 물질 조성의 변화로 트랜지스터 특성의 재현성, 신뢰성에 문제점을 가지고 있다는 것에 착안, 재현성과 대형화가 검증된 CVD법을 이용하여 투명박막 트랜지스터 기술을 개발하게 되었다.

향후 2~3년을 목표로 지속적인 공동연구개발을 통해 신뢰성 검증 및 대형 CVD장비에서의 양산가능한 기술이 확보되면, 국내 디스플레이 산업체에서 생산하는 AMOLED 및 AMLCD 디스플레이 양산에도 곧바로 적용될 수 있도록 기술 이전 계획도 갖고 있다.

연구팀 관계자는 “이번 새로운 물질 기반 투명박막트랜지스터의 기술 개발 성공은 기존 외국기업의 기술 사용에 따른 로열티 지급으로부터 벗어날 수 있는 기술 독립선언이며, 앞으로도 세계디스플레이산업을 선도하는 종주국의 면모를 이어갈 수 있는 디딤돌 역할을 할 것으로 본다” 고 말했다.

이번 기술 개발과 관련하여 TiO2박막트랜지스터의 원천특허는 KAIST 소유로 돼 있는데, 2007년 3월 국내특허를 출원하여 오는 10~11월 중에 등록될 예정이다. 지난 3월에는 지식경제부 해외특허 지원프로그램으로 채택되어 미국, 일본, 유럽에 관련기술 특허 등이 출원 중에 있다. 지난 7월 이 기술과 관련한 기술적 내용의 일부는 미국 IEEE 전자소자誌(IEEE Electron Device Letters)에 발표되었고, 오는 12월 5일, 일본 니가타에서 열리는 국제디스플레이학회(IDW 2008, International Display Workshop 2008)에서도 발표될 예정이다.

신물질 TiO2기반 투명박막트랜지스터 기술개발팀 연구책임자인 朴 교수는 미국 미시간대학교 전자공학과에서 박사학위를 받았으며, 한국, 미국, 일본 등 여러 나라의 산업체에서 근무한 경력을 갖고 있다.

<보충설명>

■ 기술의 배경

현재 국내 대기업(삼성 LCD, SDI, LG디스플레이등) 과 일본업체(소니, 마츠시타, 샤프)들 중심으로 가까운 미래 다가올 AMOLED 및 미래 투명디스플레이의 구동회로용 TFT(Thin Film Transistor) 기술개발에 대한 관심이 뜨겁다. 불행히도 기존 a-Si이나 Poly-Si기술의 한계(신뢰성, 면적제한문제)로 향후 디스플레이 backplane용 TFT는 산화물반도체로 구현되어야 한다는 사실은 이미 산학연에서 공감하고 있으나, 지금까지 산화물반도체TFT는 주로 ZnO계열 중심으로 3원계(ZTO) 또는 4원계(IGZO)를 이용하여 개발되었고 관련 해외특허도 3,000건이상 출원되었거나 등록되어 있다. 또한 In이나 Ga을 포함한 ZnO TFT의 성능은 우수하나 희소성금속으로 높은 국제시장가격과 급작스런 수요 증가시 shortage의 불안감을 항상 가지고 있어 새로운 대체 산화물을 이용한 TFT개발이 필요한 시점이다.

■ 기술의 특징

TiO2(산화티타늄) 물질은 ZnO(산화아연)와 Optical Energy bandgap이 거의 같고(3.4eV) 전자이동도도 ZnO 못지 않게 높으며, 무엇보다도 성막시 재료비가 저렴하다는 장점을 가지고 있다. 최근 KAIST 전기전자과 박재우 교수팀과 ㈜테크노세미켐, 삼성LCD총괄이 공동연구를 통해 세계 최초로 TiO2 박막을 active channel(활성층)로 채택하여 투명 산화물 TFT를 구현하는 데 성공했다. 연구팀은 TiO2박막을 향후 디스플레이 산업에서 양산화와 대형화를 고려하여 기존 반도체/디스플레이 산업용 양산장비로 널리 알려진 CVD(Chemical Vapor Deposition: 화학기상증착)법으로 낮은 온도(250C)에서 성막하여 박막형 트랜지스터를 구현하는데 성공했다. 낮은 온도에서 CVD장치로 투명박막트랜지스터를 구현할 수 있다는 의미는 디스플레이의 대형화(현재 10, 11세대 규격 디스플레이기술 개발 중)가 가능하며, Soda-lime glass와 같은 저렴한 기판을 사용할 수 있기 때문에 재료비 절감효과를 가져올 수 있으며, 향후 투명 및 플렉시블 전자/디스플레이 응용에도 가능하다는 것이다.

2008.08.06 조회수 29416

박재우.유승협교수 산화티타늄 투명박막트랜지스터 독자기술 세계최초 개발

- 미국, 일본, 유럽에 특허출원, 관련 국제학회 발표예정

2002년에 개봉된 스티븐 스필버그 감독의 "마이너리티 리포트”(톰 크루즈 주연) 장면들 중에 보았던 투명디스플레이 구현이 꿈이 아니라 현실로 다가오고 있다.

‘꿈의 디스플레이’라 불리는 투명디스플레이, 에이엠올레드(AMOLED, 능동형 유기발광 다이오드) 디스플레이 및 플렉서블 디스플레이 등의 구동회로용으로 사용되는 투명박막트랜지스터(Transparent Thin Film Transistor) 기술이 국내 연구진에 의해 개발됐다.

전기전자공학과 박재우(朴在佑, 44) 교수와 유승협교수는 ㈜테크노세미켐, 삼성전자LCD총괄과 공동연구를 통해 미국, 일본 등이 원천특허를 보유하고 있는 산화아연(ZnO)기반 투명박막트랜지스터 기술에서 벗어나, 세계최초로 산화티타늄(TiO2)물질을 이용한 투명박막트랜지스터의 원천기술을 확보하는데 성공했다.

朴 교수팀은 미국, 일본 등과 기술특허분쟁이 일어나지 않을 뿐만 아니라 기존특허로 잡혀진 산화아연(ZnO) 물질에 포함된 In(인듐) 또는 Ga(갈륨)과 같은 희소성 금속을 사용하지 않고 지구상에 풍부한 금속자원을 이용한다는 원칙과 기존 반도체/디스플레이 산업용 대형 양산 장비로 검증 받은 화학기상증착(CVD, Chemical Vapor Deposition)법을 이용하여 낮은 온도에서 TiO2박막의 성막이 가능하게 함으로써 차세대 디스플레이의 대형화 가능성뿐만 아니라, 소다라임글래스(Soda-lime Glass)와 같은 저가 글라스기판 및 플렉서블 기판위에도 성막할 수 있는 원천 기술을 확보하는데 성공했다. 朴 교수팀은 미국, 일본이 보유한 원천기술이 스퍼터링 방식을 주로 사용하고 있으나 스퍼터링의 연속작업에 따른 물질 조성의 변화로 트랜지스터 특성의 재현성, 신뢰성에 문제점을 가지고 있다는 것에 착안, 재현성과 대형화가 검증된 CVD법을 이용하여 투명박막 트랜지스터 기술을 개발하게 되었다.

향후 2~3년을 목표로 지속적인 공동연구개발을 통해 신뢰성 검증 및 대형 CVD장비에서의 양산가능한 기술이 확보되면, 국내 디스플레이 산업체에서 생산하는 AMOLED 및 AMLCD 디스플레이 양산에도 곧바로 적용될 수 있도록 기술 이전 계획도 갖고 있다.

연구팀 관계자는 “이번 새로운 물질 기반 투명박막트랜지스터의 기술 개발 성공은 기존 외국기업의 기술 사용에 따른 로열티 지급으로부터 벗어날 수 있는 기술 독립선언이며, 앞으로도 세계디스플레이산업을 선도하는 종주국의 면모를 이어갈 수 있는 디딤돌 역할을 할 것으로 본다” 고 말했다.

이번 기술 개발과 관련하여 TiO2박막트랜지스터의 원천특허는 KAIST 소유로 돼 있는데, 2007년 3월 국내특허를 출원하여 오는 10~11월 중에 등록될 예정이다. 지난 3월에는 지식경제부 해외특허 지원프로그램으로 채택되어 미국, 일본, 유럽에 관련기술 특허 등이 출원 중에 있다. 지난 7월 이 기술과 관련한 기술적 내용의 일부는 미국 IEEE 전자소자誌(IEEE Electron Device Letters)에 발표되었고, 오는 12월 5일, 일본 니가타에서 열리는 국제디스플레이학회(IDW 2008, International Display Workshop 2008)에서도 발표될 예정이다.

신물질 TiO2기반 투명박막트랜지스터 기술개발팀 연구책임자인 朴 교수는 미국 미시간대학교 전자공학과에서 박사학위를 받았으며, 한국, 미국, 일본 등 여러 나라의 산업체에서 근무한 경력을 갖고 있다.

<보충설명>

■ 기술의 배경

현재 국내 대기업(삼성 LCD, SDI, LG디스플레이등) 과 일본업체(소니, 마츠시타, 샤프)들 중심으로 가까운 미래 다가올 AMOLED 및 미래 투명디스플레이의 구동회로용 TFT(Thin Film Transistor) 기술개발에 대한 관심이 뜨겁다. 불행히도 기존 a-Si이나 Poly-Si기술의 한계(신뢰성, 면적제한문제)로 향후 디스플레이 backplane용 TFT는 산화물반도체로 구현되어야 한다는 사실은 이미 산학연에서 공감하고 있으나, 지금까지 산화물반도체TFT는 주로 ZnO계열 중심으로 3원계(ZTO) 또는 4원계(IGZO)를 이용하여 개발되었고 관련 해외특허도 3,000건이상 출원되었거나 등록되어 있다. 또한 In이나 Ga을 포함한 ZnO TFT의 성능은 우수하나 희소성금속으로 높은 국제시장가격과 급작스런 수요 증가시 shortage의 불안감을 항상 가지고 있어 새로운 대체 산화물을 이용한 TFT개발이 필요한 시점이다.

■ 기술의 특징

TiO2(산화티타늄) 물질은 ZnO(산화아연)와 Optical Energy bandgap이 거의 같고(3.4eV) 전자이동도도 ZnO 못지 않게 높으며, 무엇보다도 성막시 재료비가 저렴하다는 장점을 가지고 있다. 최근 KAIST 전기전자과 박재우 교수팀과 ㈜테크노세미켐, 삼성LCD총괄이 공동연구를 통해 세계 최초로 TiO2 박막을 active channel(활성층)로 채택하여 투명 산화물 TFT를 구현하는 데 성공했다. 연구팀은 TiO2박막을 향후 디스플레이 산업에서 양산화와 대형화를 고려하여 기존 반도체/디스플레이 산업용 양산장비로 널리 알려진 CVD(Chemical Vapor Deposition: 화학기상증착)법으로 낮은 온도(250C)에서 성막하여 박막형 트랜지스터를 구현하는데 성공했다. 낮은 온도에서 CVD장치로 투명박막트랜지스터를 구현할 수 있다는 의미는 디스플레이의 대형화(현재 10, 11세대 규격 디스플레이기술 개발 중)가 가능하며, Soda-lime glass와 같은 저렴한 기판을 사용할 수 있기 때문에 재료비 절감효과를 가져올 수 있으며, 향후 투명 및 플렉시블 전자/디스플레이 응용에도 가능하다는 것이다.

2008.08.06 조회수 29416 -

세계에서 가장 작은 나노전자소자 공동 개발

KAIST 최양규 교수팀 / 나노종합팹센터 공동 연구

새로운 구조의 3차원 3nm급 나노전자소자(FinFET) 공동개발

현재 반도체소자 기술의 한계를 극복하여 향후 세계 반도체 시장에서 유리한 입지 확보

KAIST (총장 로버트 러플린) 최양규 교수팀과 나노종합팹센터(소장 이희철)가 테라급 차세대 반도체소자에 적용 가능한 세계에서 가장 작은 새로운 구조의 3차원 3nm급 ‘나노전자소자(FinFET)’를 공동 개발하는데 성공했다

이번에 공동 개발한 나노전자소자는 게이트가 채널의 전면을 감싸고 있는 새로운 형태의 3차원 구조를 고안하여 3nm급 트랜지스터를 개발한 것이다.

이것은 기존의 실리콘 반도체 기술의 한계를 한단계 진전시킨 의미 있는 연구 결과이다.

칩의 집적도를 높이기 위한 5nm급 나노소자 구현은 기존의 실리콘 기술이 아닌 탄소나노튜브나 분자소자 등과 같은 신소재를 사용해야 할 것으로 예상되었으나, 본 연구 결과는 실리콘 기술만으로도 5nm급 이하 소자 구현이 가능하고 ‘무어의 법칙’이 향후 20년 이상 계속 유지될 수 있다는 가능성을 제시했다.

현재까지 발표된 세계에서 가장 작은 소자는 2003년 12월 일본 NEC가 국제전자소자회의(IEDM)에서 발표한 ‘표준형 2차원 평면 소자구조를 이용한 4nm 소자’로 알려져 있으나, 이는 누설 전류가 크고 동작 시 충분한 전류를 얻지 못하는 등 만족스러운 소자 특성을 얻지는 못했다.

그러나 공동 개발된 3차원 구조(게이트가 채널의 전면을 감싸고 있는 구조)는 NEC의 4nm 소자에 비해 소자의 크기가 작을 뿐만 아니라 ‘단채널 효과’가 크게 개선된 결과를 얻었다.

이번에 공동 개발된 나노소자는 프로세서나 테라급 DRAM, SRAM, 플래시 메모리 소자로 응용이 가능하며, 휴대인터넷, 동영상 회의, 입는 컴퓨터 등의 차세대 정보처리 기기의 필수부품으로 사용될 것으로 전망되며, 컴퓨터의 두뇌에 해당되는 마이크로프로세서에 이 나노소자를 적용할 경우 처리속도가 100GHz (현재보다 25배 빠름)를 넘을 수 있을 것으로 예상된다.

전체 반도체 시장의 연평균 성장률을 7%로 가정할 경우 그 시장 규모가 2015년에는 480조로 예상되는데, 이 중 공동 개발된 3nm급 3차원 소자가 약 35% 정도를 차지할 것으로 기대된다.

이번 공동 연구개발을 통하여 얻은 차세대 나노 집적회로의 원천기술 및 응용기술은 앞으로도 우리나라가 세계 반도체 시장에서 유리한 입지를 확보하는데 기여할 것으로 평가된다.

이번 연구 성과는 오는 6월 13일 미국 하와이에서 개막되는 권위적인 국제 학술회의인 “초고집적회로 국제학회(Symposium on VLSI Technology)”에서 발표될 예정이다.

앞으로 한국과학기술원과 나노종합팹센터는 공동 프로젝트를 통하여 단위소자뿐만 아니라 3nm FinFET 제작 기술을 응용한 아날로그 및 디지털 RF 회로 등에 접목하는 양산성에 대한 추가적인 연구를 계속 진행할 예정이다.

※ 1테라 NAND 플래시는 엄지 손톱만한 크기의 칩 속에 12,500년분의 신문기사와 50만곡의 MP3 파일, 1,250편의 DVD 영화를 저장할 수 있고, 나노소자 칩을 가로, 세로에 각각 10개씩 배열하여 휴대하면 한 사람이 일생동안 보고 들은 것을 모두 저장할 수 있는 용량

2006.03.17 조회수 22492

세계에서 가장 작은 나노전자소자 공동 개발

KAIST 최양규 교수팀 / 나노종합팹센터 공동 연구

새로운 구조의 3차원 3nm급 나노전자소자(FinFET) 공동개발

현재 반도체소자 기술의 한계를 극복하여 향후 세계 반도체 시장에서 유리한 입지 확보

KAIST (총장 로버트 러플린) 최양규 교수팀과 나노종합팹센터(소장 이희철)가 테라급 차세대 반도체소자에 적용 가능한 세계에서 가장 작은 새로운 구조의 3차원 3nm급 ‘나노전자소자(FinFET)’를 공동 개발하는데 성공했다

이번에 공동 개발한 나노전자소자는 게이트가 채널의 전면을 감싸고 있는 새로운 형태의 3차원 구조를 고안하여 3nm급 트랜지스터를 개발한 것이다.

이것은 기존의 실리콘 반도체 기술의 한계를 한단계 진전시킨 의미 있는 연구 결과이다.

칩의 집적도를 높이기 위한 5nm급 나노소자 구현은 기존의 실리콘 기술이 아닌 탄소나노튜브나 분자소자 등과 같은 신소재를 사용해야 할 것으로 예상되었으나, 본 연구 결과는 실리콘 기술만으로도 5nm급 이하 소자 구현이 가능하고 ‘무어의 법칙’이 향후 20년 이상 계속 유지될 수 있다는 가능성을 제시했다.

현재까지 발표된 세계에서 가장 작은 소자는 2003년 12월 일본 NEC가 국제전자소자회의(IEDM)에서 발표한 ‘표준형 2차원 평면 소자구조를 이용한 4nm 소자’로 알려져 있으나, 이는 누설 전류가 크고 동작 시 충분한 전류를 얻지 못하는 등 만족스러운 소자 특성을 얻지는 못했다.

그러나 공동 개발된 3차원 구조(게이트가 채널의 전면을 감싸고 있는 구조)는 NEC의 4nm 소자에 비해 소자의 크기가 작을 뿐만 아니라 ‘단채널 효과’가 크게 개선된 결과를 얻었다.

이번에 공동 개발된 나노소자는 프로세서나 테라급 DRAM, SRAM, 플래시 메모리 소자로 응용이 가능하며, 휴대인터넷, 동영상 회의, 입는 컴퓨터 등의 차세대 정보처리 기기의 필수부품으로 사용될 것으로 전망되며, 컴퓨터의 두뇌에 해당되는 마이크로프로세서에 이 나노소자를 적용할 경우 처리속도가 100GHz (현재보다 25배 빠름)를 넘을 수 있을 것으로 예상된다.

전체 반도체 시장의 연평균 성장률을 7%로 가정할 경우 그 시장 규모가 2015년에는 480조로 예상되는데, 이 중 공동 개발된 3nm급 3차원 소자가 약 35% 정도를 차지할 것으로 기대된다.

이번 공동 연구개발을 통하여 얻은 차세대 나노 집적회로의 원천기술 및 응용기술은 앞으로도 우리나라가 세계 반도체 시장에서 유리한 입지를 확보하는데 기여할 것으로 평가된다.

이번 연구 성과는 오는 6월 13일 미국 하와이에서 개막되는 권위적인 국제 학술회의인 “초고집적회로 국제학회(Symposium on VLSI Technology)”에서 발표될 예정이다.

앞으로 한국과학기술원과 나노종합팹센터는 공동 프로젝트를 통하여 단위소자뿐만 아니라 3nm FinFET 제작 기술을 응용한 아날로그 및 디지털 RF 회로 등에 접목하는 양산성에 대한 추가적인 연구를 계속 진행할 예정이다.

※ 1테라 NAND 플래시는 엄지 손톱만한 크기의 칩 속에 12,500년분의 신문기사와 50만곡의 MP3 파일, 1,250편의 DVD 영화를 저장할 수 있고, 나노소자 칩을 가로, 세로에 각각 10개씩 배열하여 휴대하면 한 사람이 일생동안 보고 들은 것을 모두 저장할 수 있는 용량

2006.03.17 조회수 22492