%EB%B0%98%EB%8F%84%EC%B2%B4

-

천 조분의 1초 까지 정확한 반도체칩용 클럭 개발

최근 반도체 칩의 성능이 급격하게 향상됨에 따라, 보다 정확한 타이밍으로 칩 내의 다양한 회로 블록들의 동작을 동기화(synchronization)시키는 클럭(clock) 신호를 공급하는 기술이 중요해지고 있다.

우리 대학 기계공학과 김정원 교수 연구팀이 레이저를 이용해 반도체 칩 내에서 초저잡음 클럭 신호를 생성하고 분배할 수 있는 기술을 개발했다고 9일 밝혔다.

기존에는 클럭 신호의 정확성이 통상적으로 피코초(1조 분의 1초) 수준이었으나 이번에 개발된 기술을 이용하면 기존의 방식보다 월등한 펨토초(femtosecond, 10-15초, 천 조 분의 1초) 수준의 정확한 타이밍을 가지는 클럭 신호를 칩 내에서 생성하고 분배할 수 있으며, 클럭 분산 과정에서 발생하는 칩 내에서의 발열 또한 획기적으로 줄일 수 있다.

기계공학과 현민지 박사과정 학생이 제1 저자로 참여하고 고려대학교 세종캠퍼스 정하연 교수팀과의 공동연구로 이루어진 이번 논문은 국제학술지 `네이처 커뮤니케이션즈(Nature Communications)' 4월 24일 字에 게재됐다. (논문명: Femtosecond-precision electronic clock distribution in CMOS chips by injecting frequency comb-extracted photocurrent pulses)

고성능의 반도체 칩 내에서 클럭 신호를 분배하기 위해서는 클럭 분배 네트워크(clock distribution network, CDN)에 많은 수의 클럭 드라이버(clock driver)들을 사용해야 하는데, 이로 인해 발열과 전력 소모가 커질 뿐 아니라 클럭 타이밍도 나빠지게 된다. 칩 내의 클럭 타이밍은 무작위적으로 빠르게 변화하는 지터(jitter)와 칩 내의 서로 다른 지점 간의 클럭 도달 시간 차이에 해당하는 스큐(skew)에 의하여 결정되는데, 클럭 드라이버들의 개수가 늘어남에 따라 지터와 스큐 모두 통상 수 피코초 이상으로 커지게 된다.

연구팀은 이 문제를 해결하기 위해 펨토초 이하의 지터를 가지는 광주파수빗(optical frequency comb) 레이저를 마스터 클럭으로 하는 새로운 방식의 클럭 분배 네트워크 기술을 선보였다. 이는 광주파수빗 레이저에서 발생하는 광 펄스들을 고속 광다이오드를 이용해 광전류 펄스(photocurrent pulse)로 변환한 후 반도체 칩 내의 금속 구조 형태로 된 클럭 분배 네트워크를 충전 및 방전하는 과정을 통해 구형파 형태의 클럭 신호를 생성하는 방식이다.

특히 이 기술을 사용하면 클럭 분배 네트워크의 클럭 드라이버들을 제거한 금속 구조만을 통해 칩 내에서 클럭을 분배할 수 있어, 타이밍 성능을 개선할 수 있을 뿐 아니라 칩 내 발열도 획기적으로 줄일 수 있다. 그 결과 지터와 스큐를 기존 대비 1/100 수준인 20펨토초 이하로 낮춘 뛰어난 타이밍 성능을 보일 수 있었으며, 칩내 클럭 분산 과정에서의 전력소모 및 발열 역시 기존 방식 대비 1/100 수준으로 낮출 수 있었다.

김정원 교수는 "현재 아날로그-디지털 변환기와 같은 고속 회로에 매우 낮은 지터의 샘플링 클럭 신호를 공급해 성능을 향상하는 연구를 진행 중ˮ이라고 밝히면서 "3차원 적층 칩과 같은 구조에서 발열을 줄일 수 있을 지에 대한 후속 연구도 계획 중ˮ이라고 밝혔다.

한편 이번 연구는 삼성미래기술육성센터의 지원을 받아 수행됐다.

2023.05.09 조회수 9409

천 조분의 1초 까지 정확한 반도체칩용 클럭 개발

최근 반도체 칩의 성능이 급격하게 향상됨에 따라, 보다 정확한 타이밍으로 칩 내의 다양한 회로 블록들의 동작을 동기화(synchronization)시키는 클럭(clock) 신호를 공급하는 기술이 중요해지고 있다.

우리 대학 기계공학과 김정원 교수 연구팀이 레이저를 이용해 반도체 칩 내에서 초저잡음 클럭 신호를 생성하고 분배할 수 있는 기술을 개발했다고 9일 밝혔다.

기존에는 클럭 신호의 정확성이 통상적으로 피코초(1조 분의 1초) 수준이었으나 이번에 개발된 기술을 이용하면 기존의 방식보다 월등한 펨토초(femtosecond, 10-15초, 천 조 분의 1초) 수준의 정확한 타이밍을 가지는 클럭 신호를 칩 내에서 생성하고 분배할 수 있으며, 클럭 분산 과정에서 발생하는 칩 내에서의 발열 또한 획기적으로 줄일 수 있다.

기계공학과 현민지 박사과정 학생이 제1 저자로 참여하고 고려대학교 세종캠퍼스 정하연 교수팀과의 공동연구로 이루어진 이번 논문은 국제학술지 `네이처 커뮤니케이션즈(Nature Communications)' 4월 24일 字에 게재됐다. (논문명: Femtosecond-precision electronic clock distribution in CMOS chips by injecting frequency comb-extracted photocurrent pulses)

고성능의 반도체 칩 내에서 클럭 신호를 분배하기 위해서는 클럭 분배 네트워크(clock distribution network, CDN)에 많은 수의 클럭 드라이버(clock driver)들을 사용해야 하는데, 이로 인해 발열과 전력 소모가 커질 뿐 아니라 클럭 타이밍도 나빠지게 된다. 칩 내의 클럭 타이밍은 무작위적으로 빠르게 변화하는 지터(jitter)와 칩 내의 서로 다른 지점 간의 클럭 도달 시간 차이에 해당하는 스큐(skew)에 의하여 결정되는데, 클럭 드라이버들의 개수가 늘어남에 따라 지터와 스큐 모두 통상 수 피코초 이상으로 커지게 된다.

연구팀은 이 문제를 해결하기 위해 펨토초 이하의 지터를 가지는 광주파수빗(optical frequency comb) 레이저를 마스터 클럭으로 하는 새로운 방식의 클럭 분배 네트워크 기술을 선보였다. 이는 광주파수빗 레이저에서 발생하는 광 펄스들을 고속 광다이오드를 이용해 광전류 펄스(photocurrent pulse)로 변환한 후 반도체 칩 내의 금속 구조 형태로 된 클럭 분배 네트워크를 충전 및 방전하는 과정을 통해 구형파 형태의 클럭 신호를 생성하는 방식이다.

특히 이 기술을 사용하면 클럭 분배 네트워크의 클럭 드라이버들을 제거한 금속 구조만을 통해 칩 내에서 클럭을 분배할 수 있어, 타이밍 성능을 개선할 수 있을 뿐 아니라 칩 내 발열도 획기적으로 줄일 수 있다. 그 결과 지터와 스큐를 기존 대비 1/100 수준인 20펨토초 이하로 낮춘 뛰어난 타이밍 성능을 보일 수 있었으며, 칩내 클럭 분산 과정에서의 전력소모 및 발열 역시 기존 방식 대비 1/100 수준으로 낮출 수 있었다.

김정원 교수는 "현재 아날로그-디지털 변환기와 같은 고속 회로에 매우 낮은 지터의 샘플링 클럭 신호를 공급해 성능을 향상하는 연구를 진행 중ˮ이라고 밝히면서 "3차원 적층 칩과 같은 구조에서 발열을 줄일 수 있을 지에 대한 후속 연구도 계획 중ˮ이라고 밝혔다.

한편 이번 연구는 삼성미래기술육성센터의 지원을 받아 수행됐다.

2023.05.09 조회수 9409 -

온도 제어로 반도체 패키징 내구성 40% 향상

최근 반도체의 전공정에서 회로를 미세화하는 작업이 한계에 다다르면서 후공정인 반도체 패키징이 차세대 기술로 주목받고 있다. 반도체 패키지는 여러 개의 반도체 칩을 하나로 이어주며 외부 환경으로부터 보호해주는 공정을 말한다. 아울러, 반도체 패키지의 온도도 중요한데 반도체부품의 온도가 높아지면 반도체 수명이 급격이 줄어들고 작동하지 않기 때문이다.

우리 대학 기계공학과 김성수 교수 연구팀이 메사추세츠공과대학(MIT) 브라이언 워들(Brian L. Wardle) 교수 연구팀과 함께 ‘반도체 패키지의 신뢰성 강화를 위한 접합 온도 제어 기반의 경화 공정’을 개발하는 데 성공했다.

반도체 패키지의 주된 재료인 *EMC는 열을 가하면 화학반응이 일어나 단단해지는데 이 현상을 경화 반응(Curing reaction)이라고 한다. 경화 공정은 시간에 따른 온도 및 압력 변화를 반도체 패키지의 두께가 얇아짐에 따라 공정 후 재료간의 열수축 차이로 인한 뒤틀리는 휨(Warpage) 현상이 나타나게 된다. 이 문제를 해결하고자 공동연구팀은 EMC와 기판사이 접합 온도를 정확히 예측하고 휨현상을 제어할 수 있는 경화 공정을 개발했다.

☞ EMC (Epoxy Molding Compund) : 수분, 열, 충격 등 다양한 외부 환경으로부터 반도체 회로를 효과적으로 보호하는 회로 보호재를 말한다.

공동연구팀은 반도체 패키지의 접합 온도를 낮추기 이번 연구에서 두 재료의 접합이 일어나는 온도 직전에 급격히 온도를 낮춰주는 접합 온도 제어 기반의 EMC 경화 공정 기술을 개발하였다. 열경화성 고분자인 EMC는 경화 공정 중 기판과 접합이 발생하는 온도 직전에 상온으로 급랭을 하게 되면 경화 반응을 억제해 접합 온도를 상온에 가깝게 유도할 수 있으며, 이후 재가열을 통해 EMC를 완전히 경화시킬 수 있다. 이 과정을 통해 패키지의 접합 온도와 사용 온도 차이를 줄여줌으로써 요소 간 열수축 차이에 의한 길이 변화 차이를 최소화해 휨을 줄일 수 있다. 이를 위해서는 두 재료 사이의 정확한 접합 온도를 분석하는 것이 중요하며, 연구팀은 경화 공정 중에 발생하는 EMC의 화학적 수축을 고려한 접합 온도를 구하는 식을 유도했으며, 변형율 측정 시스템을 활용해 이를 검증했다.

이러한 과정을 통해 정확히 측정된 접합 온도 직전에서 급랭 과정을 도입한 새로운 경화 공정을 통해 기존 EMC 경화 공정 대비 반도체 패키지의 휨은 27% 감소했으며, EMC와 기판 경계면의 기계적 강도는 약 40% 상승했다. 또한, 급랭 과정을 포함하는 경화 공정을 거친 EMC의 기계적 물성은 기존 공정과 차이가 없음을 확인했다. 연구 책임자인 김성수 교수는 “접합 온도 제어 기반의 새로운 EMC 경화 공정은 경박단소화 되어가고 있는 반도체 패키지에서 지속적으로 대두되고 있는 휨 문제를 해결하여 반도체 패키지의 수율을 향상시킬 뿐만 아니라 내구성도 강화할 수 있을 기반 기술이 될 것”이라고 연구 의미를 설명했다.

기계공학과 박성연 박사가 제1 저자로 참여하고 한국연구재단, BK 사업 그리고 국제협력사업 시그니쳐 프로젝트(Signature project)의 지원으로 수행된 이번 연구는 국제 저명 학술지인 ‘ACS applied materials&interfaces’에 지난 3월 1일 자로 게재됐다. (논문명 : Electronic packaging engineered by reducing the bonding temperature via modified cure cycles. doi/10.1021/acsami.2c21229). 또한, 해당 논문의 우수성을 인정받아 표지 논문 (Supplementary cover)으로 선정됐다.

2023.05.02 조회수 8151

온도 제어로 반도체 패키징 내구성 40% 향상

최근 반도체의 전공정에서 회로를 미세화하는 작업이 한계에 다다르면서 후공정인 반도체 패키징이 차세대 기술로 주목받고 있다. 반도체 패키지는 여러 개의 반도체 칩을 하나로 이어주며 외부 환경으로부터 보호해주는 공정을 말한다. 아울러, 반도체 패키지의 온도도 중요한데 반도체부품의 온도가 높아지면 반도체 수명이 급격이 줄어들고 작동하지 않기 때문이다.

우리 대학 기계공학과 김성수 교수 연구팀이 메사추세츠공과대학(MIT) 브라이언 워들(Brian L. Wardle) 교수 연구팀과 함께 ‘반도체 패키지의 신뢰성 강화를 위한 접합 온도 제어 기반의 경화 공정’을 개발하는 데 성공했다.

반도체 패키지의 주된 재료인 *EMC는 열을 가하면 화학반응이 일어나 단단해지는데 이 현상을 경화 반응(Curing reaction)이라고 한다. 경화 공정은 시간에 따른 온도 및 압력 변화를 반도체 패키지의 두께가 얇아짐에 따라 공정 후 재료간의 열수축 차이로 인한 뒤틀리는 휨(Warpage) 현상이 나타나게 된다. 이 문제를 해결하고자 공동연구팀은 EMC와 기판사이 접합 온도를 정확히 예측하고 휨현상을 제어할 수 있는 경화 공정을 개발했다.

☞ EMC (Epoxy Molding Compund) : 수분, 열, 충격 등 다양한 외부 환경으로부터 반도체 회로를 효과적으로 보호하는 회로 보호재를 말한다.

공동연구팀은 반도체 패키지의 접합 온도를 낮추기 이번 연구에서 두 재료의 접합이 일어나는 온도 직전에 급격히 온도를 낮춰주는 접합 온도 제어 기반의 EMC 경화 공정 기술을 개발하였다. 열경화성 고분자인 EMC는 경화 공정 중 기판과 접합이 발생하는 온도 직전에 상온으로 급랭을 하게 되면 경화 반응을 억제해 접합 온도를 상온에 가깝게 유도할 수 있으며, 이후 재가열을 통해 EMC를 완전히 경화시킬 수 있다. 이 과정을 통해 패키지의 접합 온도와 사용 온도 차이를 줄여줌으로써 요소 간 열수축 차이에 의한 길이 변화 차이를 최소화해 휨을 줄일 수 있다. 이를 위해서는 두 재료 사이의 정확한 접합 온도를 분석하는 것이 중요하며, 연구팀은 경화 공정 중에 발생하는 EMC의 화학적 수축을 고려한 접합 온도를 구하는 식을 유도했으며, 변형율 측정 시스템을 활용해 이를 검증했다.

이러한 과정을 통해 정확히 측정된 접합 온도 직전에서 급랭 과정을 도입한 새로운 경화 공정을 통해 기존 EMC 경화 공정 대비 반도체 패키지의 휨은 27% 감소했으며, EMC와 기판 경계면의 기계적 강도는 약 40% 상승했다. 또한, 급랭 과정을 포함하는 경화 공정을 거친 EMC의 기계적 물성은 기존 공정과 차이가 없음을 확인했다. 연구 책임자인 김성수 교수는 “접합 온도 제어 기반의 새로운 EMC 경화 공정은 경박단소화 되어가고 있는 반도체 패키지에서 지속적으로 대두되고 있는 휨 문제를 해결하여 반도체 패키지의 수율을 향상시킬 뿐만 아니라 내구성도 강화할 수 있을 기반 기술이 될 것”이라고 연구 의미를 설명했다.

기계공학과 박성연 박사가 제1 저자로 참여하고 한국연구재단, BK 사업 그리고 국제협력사업 시그니쳐 프로젝트(Signature project)의 지원으로 수행된 이번 연구는 국제 저명 학술지인 ‘ACS applied materials&interfaces’에 지난 3월 1일 자로 게재됐다. (논문명 : Electronic packaging engineered by reducing the bonding temperature via modified cure cycles. doi/10.1021/acsami.2c21229). 또한, 해당 논문의 우수성을 인정받아 표지 논문 (Supplementary cover)으로 선정됐다.

2023.05.02 조회수 8151 -

생생한 3차원 실사 이미지 구현하는 ‘메타브레인’ 개발

우리 대학 전기및전자공학부 유회준 교수 연구팀이 실사에 가까운 이미지를 렌더링할 수 있는 인공지능 기반 3D 렌더링을 모바일 기기에서 구현, 고속, 저전력 인공지능(AI: Artificial Intelligent) 반도체*인 메타브레인(MetaVRain)’을 세계 최초로 개발했다고 7일 밝혔다.

* 인공지능 반도체 : 인식·추론·학습·판단 등 인공지능 처리 기능을 탑재하고, 초지능·초저전력·초신뢰 기반의 최적화된 기술로 구현한 반도체

연구팀이 개발한 인공지능 반도체는 GPU로 구동되는 기존 레이 트레이싱 (ray-tracing)* 기반 3D 렌더링을 새로 제작된 AI 반도체 상에서 인공지능 기반 3차원으로 만들어, 기존의 막대한 비용이 들어가는 3차원 영상 캡쳐 스튜디오가 필요없게 되므로 3D 모델 제작에 드는 비용을 크게 줄이고, 사용되는 메모리를 180배 이상 줄일 수 있다. 특히 블렌더(Blender) 등의 복잡한 소프트웨어를 사용하던 기존 3D 그래픽 편집과 디자인을 간단한 인공지능 학습만으로 대체하여, 일반인도 손쉽게 원하는 스타일을 입히고 편집할 수 있다는 장점이 있다.

*레이 트레이싱 (ray-tracing): 광원, 물체의 형태, 질감에 따라 바뀌는 모든 광선의 궤적을 추적함으로써 실사에 가까운 이미지를 얻도록 하는 기술

한동현 박사과정이 제1 저자로 참여한 이번 연구는 지난 2월 18일부터 22일까지 전 세계 반도체 연구자들이 미국 샌프란시스코에 모여 개최한 국제고체회로설계학회(ISSCC)에서 발표됐다. (논문번호 2.7, 논문명: 메타브레인: A 133mW Real-time Hyper-realistic 3D NeRF Processor with 1D-2D Hybrid Neural Engines for Metaverse on Mobile Devices (저자: 한동현, 류준하, 김상엽, 김상진, 유회준))

유 교수팀은 인공지능을 통해 3D 렌더링을 구현할 때 발생하는 비효율적인 연산들을 발견하고 이를 줄이기 위해 사람의 시각적 인식 방식을 결합한 새로운 컨셉의 반도체를 개발했다. 사람은 사물을 기억할 때, 대략적인 윤곽에서 시작하여, 점점 그 형태를 구체화하는 과정과 바로 직전에 보았던 물체라면 이를 토대로 현재의 물체가 어떻게 생겼는지 바로 추측하는 인지능을 가지고 있다. 이러한 사람의 인지 과정을 모방하여, 새롭게 개발한 반도체는 저해상도 복셀을 통해 미리 사물의 대략적인 형태를 파악하고, 과거 렌더링했던 결과를 토대로, 현재 렌더링할 때 필요한 연산량을 최소화하는 연산 방식을 채택하였다.

유 교수팀이 개발한 메타브레인은 사람의 시각적 인식 과정을 모방한 하드웨어 아키텍처뿐만 아니라 최첨단 CMOS 칩을 함께 개발하여, 세계 최고의 성능을 달성하였다. 메타브레인은 인공지능 기반 3D 렌더링 기술에 최적화되어, 최대 100 FPS 이상의 렌더링 속도를 달성하였으며, 이는 기존 GPU보다 911배 빠른 속도다. 뿐만아니라, 1개 영상화면 처리 당 소모에너지를 나타내는 에너지효율 역시 GPU 대비 26,400배 높인 연구 결과로 VR/AR 헤드셋, 모바일 기기에서도 인공지능 기반 실시간 렌더링의 가능성을 열었다.

연구팀은 메타브레인의 활용 예시를 보여주고자, 스마트 3D 렌더링 응용시스템을 함께 개발하였으며, 사용자가 선호하는 스타일에 맞춰, 3D 모델의 스타일을 바꾸는 예제를 보여주었다. 인공지능에게 원하는 스타일의 이미지를 주고 재학습만 수행하면 되기 때문에, 복잡한 소프트웨어의 도움 없이도 손쉽게 3D 모델의 스타일을 손쉽게 바꿀 수 있다. 유 교수팀이 구현한 응용시스템의 예시 이외에도, 사용자의 얼굴을 본떠 만든 실제에 가까운 3D 아바타를 만들거나, 각종 구조물들의 3D 모델을 만들고 영화 제작 환경에 맞춰 날씨를 바꾸는 등 다양한 응용 예시가 가능할 것으로 기대된다.

연구팀은 메타브레인을 시작으로, 앞으로의 3D 그래픽스 분야 역시 인공지능으로 대체되기 시작할 것으로 기대한다며, 인공지능과 3D 그래픽스의 결합은 메타버스 실현을 위한 큰 기술적 혁신이라는 점을 밝혔다.

연구를 주도한 KAIST 전기및전자공학부 유회준 교수는 “현재 3D 그래픽스는 사람이 사물을 어떻게 보고 있는지가 아니라, 사물이 어떻게 생겼는지를 묘사하는데 집중하고 있다”라며 “이번 연구는 인공지능이 사람의 공간 인지 능력을 모방하여 사람이 사물을 인식하고 표현하는 방법을 차용함으로써 효율적인 3D 그래픽스를 가능케 한 연구”라고 본 연구의 의의를 밝혔다. 또한 “메타버스의 실현은 본 연구에서 보인 것처럼 인공지능 기술의 혁신과 인공지능 반도체의 혁신이 함께 이루어질 것”이라 미래를 전망하였다.

데모 동영상 유튜브 주소: https://www.youtube.com/watch?v=m-aqnZhALv0

2023.03.07 조회수 8929

생생한 3차원 실사 이미지 구현하는 ‘메타브레인’ 개발

우리 대학 전기및전자공학부 유회준 교수 연구팀이 실사에 가까운 이미지를 렌더링할 수 있는 인공지능 기반 3D 렌더링을 모바일 기기에서 구현, 고속, 저전력 인공지능(AI: Artificial Intelligent) 반도체*인 메타브레인(MetaVRain)’을 세계 최초로 개발했다고 7일 밝혔다.

* 인공지능 반도체 : 인식·추론·학습·판단 등 인공지능 처리 기능을 탑재하고, 초지능·초저전력·초신뢰 기반의 최적화된 기술로 구현한 반도체

연구팀이 개발한 인공지능 반도체는 GPU로 구동되는 기존 레이 트레이싱 (ray-tracing)* 기반 3D 렌더링을 새로 제작된 AI 반도체 상에서 인공지능 기반 3차원으로 만들어, 기존의 막대한 비용이 들어가는 3차원 영상 캡쳐 스튜디오가 필요없게 되므로 3D 모델 제작에 드는 비용을 크게 줄이고, 사용되는 메모리를 180배 이상 줄일 수 있다. 특히 블렌더(Blender) 등의 복잡한 소프트웨어를 사용하던 기존 3D 그래픽 편집과 디자인을 간단한 인공지능 학습만으로 대체하여, 일반인도 손쉽게 원하는 스타일을 입히고 편집할 수 있다는 장점이 있다.

*레이 트레이싱 (ray-tracing): 광원, 물체의 형태, 질감에 따라 바뀌는 모든 광선의 궤적을 추적함으로써 실사에 가까운 이미지를 얻도록 하는 기술

한동현 박사과정이 제1 저자로 참여한 이번 연구는 지난 2월 18일부터 22일까지 전 세계 반도체 연구자들이 미국 샌프란시스코에 모여 개최한 국제고체회로설계학회(ISSCC)에서 발표됐다. (논문번호 2.7, 논문명: 메타브레인: A 133mW Real-time Hyper-realistic 3D NeRF Processor with 1D-2D Hybrid Neural Engines for Metaverse on Mobile Devices (저자: 한동현, 류준하, 김상엽, 김상진, 유회준))

유 교수팀은 인공지능을 통해 3D 렌더링을 구현할 때 발생하는 비효율적인 연산들을 발견하고 이를 줄이기 위해 사람의 시각적 인식 방식을 결합한 새로운 컨셉의 반도체를 개발했다. 사람은 사물을 기억할 때, 대략적인 윤곽에서 시작하여, 점점 그 형태를 구체화하는 과정과 바로 직전에 보았던 물체라면 이를 토대로 현재의 물체가 어떻게 생겼는지 바로 추측하는 인지능을 가지고 있다. 이러한 사람의 인지 과정을 모방하여, 새롭게 개발한 반도체는 저해상도 복셀을 통해 미리 사물의 대략적인 형태를 파악하고, 과거 렌더링했던 결과를 토대로, 현재 렌더링할 때 필요한 연산량을 최소화하는 연산 방식을 채택하였다.

유 교수팀이 개발한 메타브레인은 사람의 시각적 인식 과정을 모방한 하드웨어 아키텍처뿐만 아니라 최첨단 CMOS 칩을 함께 개발하여, 세계 최고의 성능을 달성하였다. 메타브레인은 인공지능 기반 3D 렌더링 기술에 최적화되어, 최대 100 FPS 이상의 렌더링 속도를 달성하였으며, 이는 기존 GPU보다 911배 빠른 속도다. 뿐만아니라, 1개 영상화면 처리 당 소모에너지를 나타내는 에너지효율 역시 GPU 대비 26,400배 높인 연구 결과로 VR/AR 헤드셋, 모바일 기기에서도 인공지능 기반 실시간 렌더링의 가능성을 열었다.

연구팀은 메타브레인의 활용 예시를 보여주고자, 스마트 3D 렌더링 응용시스템을 함께 개발하였으며, 사용자가 선호하는 스타일에 맞춰, 3D 모델의 스타일을 바꾸는 예제를 보여주었다. 인공지능에게 원하는 스타일의 이미지를 주고 재학습만 수행하면 되기 때문에, 복잡한 소프트웨어의 도움 없이도 손쉽게 3D 모델의 스타일을 손쉽게 바꿀 수 있다. 유 교수팀이 구현한 응용시스템의 예시 이외에도, 사용자의 얼굴을 본떠 만든 실제에 가까운 3D 아바타를 만들거나, 각종 구조물들의 3D 모델을 만들고 영화 제작 환경에 맞춰 날씨를 바꾸는 등 다양한 응용 예시가 가능할 것으로 기대된다.

연구팀은 메타브레인을 시작으로, 앞으로의 3D 그래픽스 분야 역시 인공지능으로 대체되기 시작할 것으로 기대한다며, 인공지능과 3D 그래픽스의 결합은 메타버스 실현을 위한 큰 기술적 혁신이라는 점을 밝혔다.

연구를 주도한 KAIST 전기및전자공학부 유회준 교수는 “현재 3D 그래픽스는 사람이 사물을 어떻게 보고 있는지가 아니라, 사물이 어떻게 생겼는지를 묘사하는데 집중하고 있다”라며 “이번 연구는 인공지능이 사람의 공간 인지 능력을 모방하여 사람이 사물을 인식하고 표현하는 방법을 차용함으로써 효율적인 3D 그래픽스를 가능케 한 연구”라고 본 연구의 의의를 밝혔다. 또한 “메타버스의 실현은 본 연구에서 보인 것처럼 인공지능 기술의 혁신과 인공지능 반도체의 혁신이 함께 이루어질 것”이라 미래를 전망하였다.

데모 동영상 유튜브 주소: https://www.youtube.com/watch?v=m-aqnZhALv0

2023.03.07 조회수 8929 -

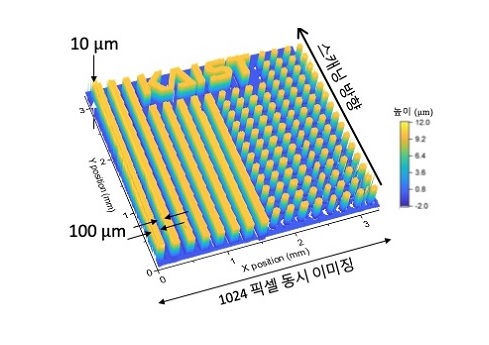

반도체 소자 내의 복잡한 움직임을 관측할 수 있는 초고속 카메라 개발

우리 대학 김정원 교수 연구팀이 반도체 소자 내의 미세 구조와 동적 특성을 고해상도로 측정할 수 있는 초고속 카메라 기술을 개발하였다고 밝혔다.

기존에는 볼 수 없었던 반도체 소자 내에서의 빠르고 불규칙적인 복잡한 움직임을 이제 초고속 카메라로 관측할 수 있게 되었다.

기계공학과 나용진 박사가 제 1저자로 참여하고 기계공학과 유홍기, 이정철 교수팀 및 한국표준과학연구원(KRISS) 서준호, 강주식 박사팀이 참여한 공동연구팀의 이번 논문은 국제학술지 ‘빛: 과학과 응용(Light: Science & Applications)’ [IF=20.257] 2월 15일 字에 게재됐다. (논문명: Massively parallel electro-optic sampling of space-encoded optical pulses for ultrafast multi-dimensional imaging)

최근 마이크로 및 나노 소자들의 복잡도와 기능성이 급격하게 향상됨에 따라 이들 소자 내의 미세 구조와 동적인 움직임을 실시간으로 정확하게 측정해야 할 필요성이 급증하고 있다. 미세 구조 측정 측면에서는 다양한 3차원 집적회로와 소자들의 발전으로 더 큰 웨이퍼 영역에 대해 더 높은 분해능 및 측정속도를 가지는 계측 기술이 반도체 산업에서 중요해지고 있다. 한편 동적 특성의 측정은 마이크로 및 나노 소자 내에서의 물리현상들을 이해하고 다양한 응용 분야들로 발전시키는 데 중요하다. 특히 다양한 역학 현상의 관측을 위해서는 더 높은 해상도, 더 빠른 측정속도 및 더 큰 측정범위를 필요로 하지만 기존의 측정 기술들은 여러가지 한계들을 가지고 있었다.

이번 연구는 기존의 한계를 극복한 새로운 초고속 카메라 기술을 개발하였다. 100펨토초(10조분이 1초) 정도의 매우 짧은 펄스폭을 가지는 빛 펄스를 1000개 이상의 다른 색을 가지는 펄스들로 쪼갠 후, 각기 다른 색을 가진 펄스들을 이용하여 서로 다른 공간적 위치에서의 높낮이를 정밀하게 측정할 수 있는 기술이다. 구현한 기술은 초당 2.6억개의 픽셀들에 대한 높낮이의 차이를 최고 330피코미터(30억분의 1미터) 수준까지 측정할 수 있을 정도로 빠르고 정밀하다. 연구팀은 이를 이용하여 복잡한 3차원 형상을 고속으로 정밀하고 정확하게 측정할 수 있는 초고속 카메라 기능을 선보였고, 기존의 측정 기술로는 관측하기 어렵던 복잡하고 비반복적인 고속의 동역학 현상들을 성공적으로 관측할 수 있었다.

이번에 개발한 초고속 카메라 기술의 고속 형상 이미징 속도와 높은 공간 분해능을 이용하면 반도체 공정이나 3D 프린팅 과정을 실시간으로 모니터링하며 공정을 제어할 수 있어 점점 고도화 및 집적화 되는 공정의 수율을 크게 향상시킬 수 있을 것으로 기대된다. 또한 다양한 진폭이 존재하면서 동시에 매우 빠른 순간 속도를 갖는 미세 구조의 움직임을 포착할 수 있음을 보여, 기존에 관찰하지 못했던 복잡한 비선형(nonlinear) 및 과도(transient)의 물리 현상들을 탐구하는 차세대 계측 기술로 발전할 수 있을 것으로 기대된다.

김정원 교수는 “이번 연구에서는 1차원적인 선 모양의 빛을 스캔해서 움직이는 방식으로 2차원 표면의 높낮이를 측정하였으나, 향후에는 2차원 표면의 높낮이를 스캔 없이 한번에 측정할 수 있는 방식으로 기술을 발전시킬 예정”이라고 밝혔다.

한편 이번 연구는 과학기술정보통신부와 한국연구재단이 추진하는 중견후속연구, 선도연구센터, 기초연구실 및 중견연구 사업의 지원을 받아 수행됐다.

2023.03.02 조회수 9556

반도체 소자 내의 복잡한 움직임을 관측할 수 있는 초고속 카메라 개발

우리 대학 김정원 교수 연구팀이 반도체 소자 내의 미세 구조와 동적 특성을 고해상도로 측정할 수 있는 초고속 카메라 기술을 개발하였다고 밝혔다.

기존에는 볼 수 없었던 반도체 소자 내에서의 빠르고 불규칙적인 복잡한 움직임을 이제 초고속 카메라로 관측할 수 있게 되었다.

기계공학과 나용진 박사가 제 1저자로 참여하고 기계공학과 유홍기, 이정철 교수팀 및 한국표준과학연구원(KRISS) 서준호, 강주식 박사팀이 참여한 공동연구팀의 이번 논문은 국제학술지 ‘빛: 과학과 응용(Light: Science & Applications)’ [IF=20.257] 2월 15일 字에 게재됐다. (논문명: Massively parallel electro-optic sampling of space-encoded optical pulses for ultrafast multi-dimensional imaging)

최근 마이크로 및 나노 소자들의 복잡도와 기능성이 급격하게 향상됨에 따라 이들 소자 내의 미세 구조와 동적인 움직임을 실시간으로 정확하게 측정해야 할 필요성이 급증하고 있다. 미세 구조 측정 측면에서는 다양한 3차원 집적회로와 소자들의 발전으로 더 큰 웨이퍼 영역에 대해 더 높은 분해능 및 측정속도를 가지는 계측 기술이 반도체 산업에서 중요해지고 있다. 한편 동적 특성의 측정은 마이크로 및 나노 소자 내에서의 물리현상들을 이해하고 다양한 응용 분야들로 발전시키는 데 중요하다. 특히 다양한 역학 현상의 관측을 위해서는 더 높은 해상도, 더 빠른 측정속도 및 더 큰 측정범위를 필요로 하지만 기존의 측정 기술들은 여러가지 한계들을 가지고 있었다.

이번 연구는 기존의 한계를 극복한 새로운 초고속 카메라 기술을 개발하였다. 100펨토초(10조분이 1초) 정도의 매우 짧은 펄스폭을 가지는 빛 펄스를 1000개 이상의 다른 색을 가지는 펄스들로 쪼갠 후, 각기 다른 색을 가진 펄스들을 이용하여 서로 다른 공간적 위치에서의 높낮이를 정밀하게 측정할 수 있는 기술이다. 구현한 기술은 초당 2.6억개의 픽셀들에 대한 높낮이의 차이를 최고 330피코미터(30억분의 1미터) 수준까지 측정할 수 있을 정도로 빠르고 정밀하다. 연구팀은 이를 이용하여 복잡한 3차원 형상을 고속으로 정밀하고 정확하게 측정할 수 있는 초고속 카메라 기능을 선보였고, 기존의 측정 기술로는 관측하기 어렵던 복잡하고 비반복적인 고속의 동역학 현상들을 성공적으로 관측할 수 있었다.

이번에 개발한 초고속 카메라 기술의 고속 형상 이미징 속도와 높은 공간 분해능을 이용하면 반도체 공정이나 3D 프린팅 과정을 실시간으로 모니터링하며 공정을 제어할 수 있어 점점 고도화 및 집적화 되는 공정의 수율을 크게 향상시킬 수 있을 것으로 기대된다. 또한 다양한 진폭이 존재하면서 동시에 매우 빠른 순간 속도를 갖는 미세 구조의 움직임을 포착할 수 있음을 보여, 기존에 관찰하지 못했던 복잡한 비선형(nonlinear) 및 과도(transient)의 물리 현상들을 탐구하는 차세대 계측 기술로 발전할 수 있을 것으로 기대된다.

김정원 교수는 “이번 연구에서는 1차원적인 선 모양의 빛을 스캔해서 움직이는 방식으로 2차원 표면의 높낮이를 측정하였으나, 향후에는 2차원 표면의 높낮이를 스캔 없이 한번에 측정할 수 있는 방식으로 기술을 발전시킬 예정”이라고 밝혔다.

한편 이번 연구는 과학기술정보통신부와 한국연구재단이 추진하는 중견후속연구, 선도연구센터, 기초연구실 및 중견연구 사업의 지원을 받아 수행됐다.

2023.03.02 조회수 9556 -

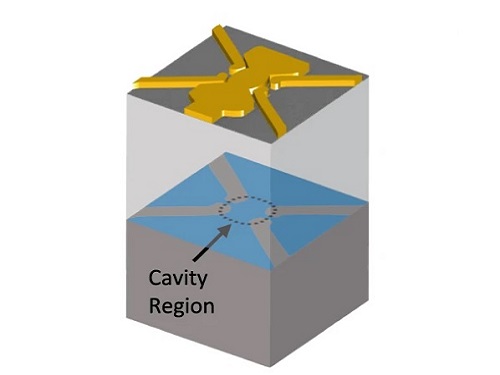

획기적인 반도체 소자 설계를 위한 2차원 공진기 개발

빛을 이용한 광공진기가 현대 정보·통신 산업에 필수적인 것과 같이, 양자 정보를 처리하는 차세대 반도체 소자를 설계하는 데에 활용될 수 있는 2차원 전자를 가두는 공진기*를 세계 최초로 구현하여 화제다.

*공진기란 한정된 공간 안에 파동을 가두는 장치로서 빛이나 음파, 혹은 통신 기술에 쓰이는 전자기파와 같은 파동을 제어하는 분야에서 필수적으로 활용됨.

우리 대학 응집상 양자 결맞음 센터(센터장 물리학과 심흥선 교수)는 우리 대학 물리학과 최형순 교수, 부산대학교 정윤철 교수, 전북대학교 최형국 교수와 공동연구를 통해 2차원 전자의 파동성을 이용한 공진기를 개발하는데 성공했다고 13일 밝혔다.

빛은 파동이면서도 다양한 매질 내에서 장거리 이동이 가능하다. 따라서 빛은 마주보는 거울 사이에 가두어 두더라도 소실되지 않고 여러 차례 왕복이 가능하여 광공진기 개발에 용이하고 실제로 다양한 광학소자들이 이미 폭넓게 개발되어 활용되고 있다. 반면에 물질 내부의 전자는 매질 내에서 쉽게 산란되어 빛의 파동성을 유효하게 활용하는 기술이나 소자 개발이 쉽지 않다. 이런 한계를 극복하고 전자를 이용하여 광학 기술을 모사하는 것을 '전자광학'이라고 한다. 이번 연구는 전자가 단순히 파동성을 띈다는 사실을 확인한 것에 그치지 않고 광공진기의 2차원 전자광학적 소자에 대응되는 전자공진기를 실제로 구현했다는 점에서 의미가 크다.

지금까지 직진하는 1차원 전자를 가둬 공진기를 만든 사례는 있었지만, 2차원 평면상에서 반사나 회절, 간섭 등이 복합적으로 일어나는 전자를 가둬 공진기를 만든 처음 사례이다. 이번 연구를 통해 앞으로 더욱 다양한 형태로 전자를 제어할 수 있는 원천기술로도 활용될 수 있을 것으로 기대된다.

공동연구팀은 반도체 나노소자 공정을 통해 전자의 파동을 반사할 수 있는 곡면거울을 제작하고 광공진기의 구조를 2차원 전자에 적용하여 물질 파동 또한 빛과 동일한 방법으로 가두어 둘 수 있다는 사실을 밝혀낸 것이다. 이를 위해 반도체를 극저온으로 냉각하면 반도체 내부의 전자가 수 미크론(백만분의 1미터) 정도 양자역학적 특성이 보존되는 2차원 전자 파동 형태로 존재할 수 있다. 이 반도체 위에 전극을 입히고 강한 음전압을 걸어주면 전극이 있는 영역으로는 전자가 진입하지 못하게 되므로 전자가 반사되는 거울 역할을 할 수 있다. 이 원리를 적용하여 두 개의 마주 보는 곡면거울로 이루어진 공진기 구조를 만들고 그 내부에 전자 파동을 주입하여 그 전도도를 측정함으로써 실제로 전자가 공명하는 특성이 관측하였다. 이를 통해 양자역학적 특성을 갖는 물질 파동 또한 빛과 동일한 방법으로 가두어 둘 수 있다는 사실을 밝혀낸 것이다.

우리 대학 물리학과 박사과정 박동성학생과 부산대학교 박사과정 정환철학생이 공동 제1 저자로 참여한 이 연구 결과는 지난 1월 26일 네이처 자매지인 `네이처 커뮤니케이션즈(Nature Communications)'에 게재됐다. (논문명 : Observation of electronic modes in open cavity resonator)

최형순 교수는 “동 기술은 2차원 전자계의 전자광학 발전에 새로운 가능성을 제시하는 원천기술로써 향후 다양한 양자기술 분야에도 활용될 수 있을 것으로 기대된다”라고 설명했다.

이번 연구는 한국연구재단 선도연구센터(SRC)를 중심으로 이루어졌으며 그 외에도 한국연구재단의 다양한 연구 사업(양자컴퓨팅 개발사업, 기본연구, 중견연구 지원사업 등)의 지원이 있었다.

2023.02.13 조회수 10576

획기적인 반도체 소자 설계를 위한 2차원 공진기 개발

빛을 이용한 광공진기가 현대 정보·통신 산업에 필수적인 것과 같이, 양자 정보를 처리하는 차세대 반도체 소자를 설계하는 데에 활용될 수 있는 2차원 전자를 가두는 공진기*를 세계 최초로 구현하여 화제다.

*공진기란 한정된 공간 안에 파동을 가두는 장치로서 빛이나 음파, 혹은 통신 기술에 쓰이는 전자기파와 같은 파동을 제어하는 분야에서 필수적으로 활용됨.

우리 대학 응집상 양자 결맞음 센터(센터장 물리학과 심흥선 교수)는 우리 대학 물리학과 최형순 교수, 부산대학교 정윤철 교수, 전북대학교 최형국 교수와 공동연구를 통해 2차원 전자의 파동성을 이용한 공진기를 개발하는데 성공했다고 13일 밝혔다.

빛은 파동이면서도 다양한 매질 내에서 장거리 이동이 가능하다. 따라서 빛은 마주보는 거울 사이에 가두어 두더라도 소실되지 않고 여러 차례 왕복이 가능하여 광공진기 개발에 용이하고 실제로 다양한 광학소자들이 이미 폭넓게 개발되어 활용되고 있다. 반면에 물질 내부의 전자는 매질 내에서 쉽게 산란되어 빛의 파동성을 유효하게 활용하는 기술이나 소자 개발이 쉽지 않다. 이런 한계를 극복하고 전자를 이용하여 광학 기술을 모사하는 것을 '전자광학'이라고 한다. 이번 연구는 전자가 단순히 파동성을 띈다는 사실을 확인한 것에 그치지 않고 광공진기의 2차원 전자광학적 소자에 대응되는 전자공진기를 실제로 구현했다는 점에서 의미가 크다.

지금까지 직진하는 1차원 전자를 가둬 공진기를 만든 사례는 있었지만, 2차원 평면상에서 반사나 회절, 간섭 등이 복합적으로 일어나는 전자를 가둬 공진기를 만든 처음 사례이다. 이번 연구를 통해 앞으로 더욱 다양한 형태로 전자를 제어할 수 있는 원천기술로도 활용될 수 있을 것으로 기대된다.

공동연구팀은 반도체 나노소자 공정을 통해 전자의 파동을 반사할 수 있는 곡면거울을 제작하고 광공진기의 구조를 2차원 전자에 적용하여 물질 파동 또한 빛과 동일한 방법으로 가두어 둘 수 있다는 사실을 밝혀낸 것이다. 이를 위해 반도체를 극저온으로 냉각하면 반도체 내부의 전자가 수 미크론(백만분의 1미터) 정도 양자역학적 특성이 보존되는 2차원 전자 파동 형태로 존재할 수 있다. 이 반도체 위에 전극을 입히고 강한 음전압을 걸어주면 전극이 있는 영역으로는 전자가 진입하지 못하게 되므로 전자가 반사되는 거울 역할을 할 수 있다. 이 원리를 적용하여 두 개의 마주 보는 곡면거울로 이루어진 공진기 구조를 만들고 그 내부에 전자 파동을 주입하여 그 전도도를 측정함으로써 실제로 전자가 공명하는 특성이 관측하였다. 이를 통해 양자역학적 특성을 갖는 물질 파동 또한 빛과 동일한 방법으로 가두어 둘 수 있다는 사실을 밝혀낸 것이다.

우리 대학 물리학과 박사과정 박동성학생과 부산대학교 박사과정 정환철학생이 공동 제1 저자로 참여한 이 연구 결과는 지난 1월 26일 네이처 자매지인 `네이처 커뮤니케이션즈(Nature Communications)'에 게재됐다. (논문명 : Observation of electronic modes in open cavity resonator)

최형순 교수는 “동 기술은 2차원 전자계의 전자광학 발전에 새로운 가능성을 제시하는 원천기술로써 향후 다양한 양자기술 분야에도 활용될 수 있을 것으로 기대된다”라고 설명했다.

이번 연구는 한국연구재단 선도연구센터(SRC)를 중심으로 이루어졌으며 그 외에도 한국연구재단의 다양한 연구 사업(양자컴퓨팅 개발사업, 기본연구, 중견연구 지원사업 등)의 지원이 있었다.

2023.02.13 조회수 10576 -

획기적 음의 정전용량 플래시 메모리 최초 개발

우리 대학 전기및전자공학부 전상훈 교수 연구팀이 `음의 정전용량 효과(Negative Capacitance Effect, 이하 NC 효과)*'를 활용해 기존 플래시 메모리의 물리적 성능 한계를 뛰어넘는 음의 정전용량 플래시 메모리 (NC-Flash Memory)를 세계 최초로 개발했다고 18일 밝혔다.

*음의 정전용량 효과: 음의 정전용량 현상은 인가되는 전압이 증가하면 전하량이 감소함을 의미한다. 음의 정전용량 특성을 가지는 유전체 사용시, 트랜지스터에 인가되는 전압을 내부적으로 증폭하여 상대적으로 낮은 동작전압을 사용할 수 있어, 파워소모를 줄일 수 있다.

전기및전자공학부 김태호 박사과정과 김기욱 박사과정이 공동 제1 저자로 수행한 이번 연구는 저명 국제 학술지 `어드밴스드 펑셔널 머터리얼즈(Advanced Functional Materials)' 2022년 12월호에 출판됐다. (논문명 : The Opportunity of Negative Capacitance Behavior in Flash Memory for High-Density and Energy-Efficient In-Memory Computing Applications) 이 국제학술지는 독일 와일리 출판사(Wiley-VCH)에서 발행하는 피어리뷰 과학 저널이다. (Impact Factor : 19.924)

현대 전자 소자에서 축전기(Capacitor)는 매우 중요한 구성 요소의 하나로, 전자 소자가 소형화되고 수직 방향으로 적층 되면서 축전기에 저장되는 전하량(Charge, Q)이 감소하는 문제가 생기므로 높은 정전용량(Capacitance, C)을 가진 유전체 물질이 필수적으로 요구되고 있다. 여기에 일반적인 축전기와 다르게 정전용량이 음의 값을 갖는(Negative Capacitance) 축전기를 활용한다면 다층의 축전기의 전체 정전용량을 오히려 더 증가시킬 수 있고, 차세대 소자에 적합한 높은 정전용량 소자 개발 난제를 해결할 수 있을 것이라는 가설이 제안되었다.

최근 메모리 공급업체들은 데이터의 폭발적 증가와 더 높은 용량의 솔리드 스테이트 드라이브(SSD) 및 더 빠른 액세스 시간에 대한 요구로 인해 기술 경쟁을 치열하게 하고 있다. 스토리지의 핵심 기술인 3D 낸드 플래시는 지속적으로 더 높은 층을 적층할 수 있는 기술을 요구하고 있고, 2028년에는 1,000단 이상의 메모리 적층이 필요할 것으로 예상되고 있다.

한편, 강유전체* 물질에서 보이는 `음의 정전용량 효과(NC 효과)'은 전자 소자에 인가된 외부 전압을 내부적으로 증폭해 전력 소모를 줄이는 특성이 있어, 전자 소자의 물리적 성능 한계를 극복할 수 있다는 가능성이 제시됐다. 최근 페로브스카이트 강유전체에서 NC 효과를 실험적으로 관찰했으나, 페로브스카이트 강유전체의 소형화 한계 및 CMOS 공정과의 부적합성으로 인해 NC 효과를 활용한 전자 소자의 구현에 대해 상당한 회의론을 불러일으켰다.

*강유전체: 전기적으로는 절연체이지만 자연상태에서 외부 전기장이 없어도 전기 편극을 지닐 수 있는 특이한 물리적 성질을 가진 물질

전상훈 교수 연구팀은 기존 플래시 메모리의 물리적 성능 한계를 극복하고 동작전압을 낮추기 위해, 반도체 공정에 사용되는 하프늄옥사이드(HfO2) 강유전체 박막의 NC 효과를 안정화해 저전압 구동이 가능한 강유전체 소재의 NC-플래시 메모리를 세계 최초로 개발했다. 개발된 NC-플래시 메모리는 기존 플래시 메모리 대비 전력 소모가 10,000배 이상 낮은 저전력 고성능 특성을 달성했다.

연구팀은 그뿐만 아니라 기존 컴퓨팅 구조인 폰노이만 아키텍처를 대체하여 새롭게 지향하는 인메모리 컴퓨팅을 NC-플래시 메모리를 기반으로 구현해 세계 최고 수준의 에너지 효율 또한 달성했다.

이번 연구 결과는 빠른 스토리지를 필요로 하는 최신 컴퓨팅과 네트워킹의 요구를 충족하는 차세대 낸드 플래시 메모리 개발에 있어 핵심 역할을 할 것이다.

한편, 이번 연구는 연세대학교와 협업을 통해서 이루어졌고, 한국 연구재단 지능형 반도체 기술개발사업의 지원을 받아 수행됐다.

2023.01.18 조회수 9440

획기적 음의 정전용량 플래시 메모리 최초 개발

우리 대학 전기및전자공학부 전상훈 교수 연구팀이 `음의 정전용량 효과(Negative Capacitance Effect, 이하 NC 효과)*'를 활용해 기존 플래시 메모리의 물리적 성능 한계를 뛰어넘는 음의 정전용량 플래시 메모리 (NC-Flash Memory)를 세계 최초로 개발했다고 18일 밝혔다.

*음의 정전용량 효과: 음의 정전용량 현상은 인가되는 전압이 증가하면 전하량이 감소함을 의미한다. 음의 정전용량 특성을 가지는 유전체 사용시, 트랜지스터에 인가되는 전압을 내부적으로 증폭하여 상대적으로 낮은 동작전압을 사용할 수 있어, 파워소모를 줄일 수 있다.

전기및전자공학부 김태호 박사과정과 김기욱 박사과정이 공동 제1 저자로 수행한 이번 연구는 저명 국제 학술지 `어드밴스드 펑셔널 머터리얼즈(Advanced Functional Materials)' 2022년 12월호에 출판됐다. (논문명 : The Opportunity of Negative Capacitance Behavior in Flash Memory for High-Density and Energy-Efficient In-Memory Computing Applications) 이 국제학술지는 독일 와일리 출판사(Wiley-VCH)에서 발행하는 피어리뷰 과학 저널이다. (Impact Factor : 19.924)

현대 전자 소자에서 축전기(Capacitor)는 매우 중요한 구성 요소의 하나로, 전자 소자가 소형화되고 수직 방향으로 적층 되면서 축전기에 저장되는 전하량(Charge, Q)이 감소하는 문제가 생기므로 높은 정전용량(Capacitance, C)을 가진 유전체 물질이 필수적으로 요구되고 있다. 여기에 일반적인 축전기와 다르게 정전용량이 음의 값을 갖는(Negative Capacitance) 축전기를 활용한다면 다층의 축전기의 전체 정전용량을 오히려 더 증가시킬 수 있고, 차세대 소자에 적합한 높은 정전용량 소자 개발 난제를 해결할 수 있을 것이라는 가설이 제안되었다.

최근 메모리 공급업체들은 데이터의 폭발적 증가와 더 높은 용량의 솔리드 스테이트 드라이브(SSD) 및 더 빠른 액세스 시간에 대한 요구로 인해 기술 경쟁을 치열하게 하고 있다. 스토리지의 핵심 기술인 3D 낸드 플래시는 지속적으로 더 높은 층을 적층할 수 있는 기술을 요구하고 있고, 2028년에는 1,000단 이상의 메모리 적층이 필요할 것으로 예상되고 있다.

한편, 강유전체* 물질에서 보이는 `음의 정전용량 효과(NC 효과)'은 전자 소자에 인가된 외부 전압을 내부적으로 증폭해 전력 소모를 줄이는 특성이 있어, 전자 소자의 물리적 성능 한계를 극복할 수 있다는 가능성이 제시됐다. 최근 페로브스카이트 강유전체에서 NC 효과를 실험적으로 관찰했으나, 페로브스카이트 강유전체의 소형화 한계 및 CMOS 공정과의 부적합성으로 인해 NC 효과를 활용한 전자 소자의 구현에 대해 상당한 회의론을 불러일으켰다.

*강유전체: 전기적으로는 절연체이지만 자연상태에서 외부 전기장이 없어도 전기 편극을 지닐 수 있는 특이한 물리적 성질을 가진 물질

전상훈 교수 연구팀은 기존 플래시 메모리의 물리적 성능 한계를 극복하고 동작전압을 낮추기 위해, 반도체 공정에 사용되는 하프늄옥사이드(HfO2) 강유전체 박막의 NC 효과를 안정화해 저전압 구동이 가능한 강유전체 소재의 NC-플래시 메모리를 세계 최초로 개발했다. 개발된 NC-플래시 메모리는 기존 플래시 메모리 대비 전력 소모가 10,000배 이상 낮은 저전력 고성능 특성을 달성했다.

연구팀은 그뿐만 아니라 기존 컴퓨팅 구조인 폰노이만 아키텍처를 대체하여 새롭게 지향하는 인메모리 컴퓨팅을 NC-플래시 메모리를 기반으로 구현해 세계 최고 수준의 에너지 효율 또한 달성했다.

이번 연구 결과는 빠른 스토리지를 필요로 하는 최신 컴퓨팅과 네트워킹의 요구를 충족하는 차세대 낸드 플래시 메모리 개발에 있어 핵심 역할을 할 것이다.

한편, 이번 연구는 연세대학교와 협업을 통해서 이루어졌고, 한국 연구재단 지능형 반도체 기술개발사업의 지원을 받아 수행됐다.

2023.01.18 조회수 9440 -

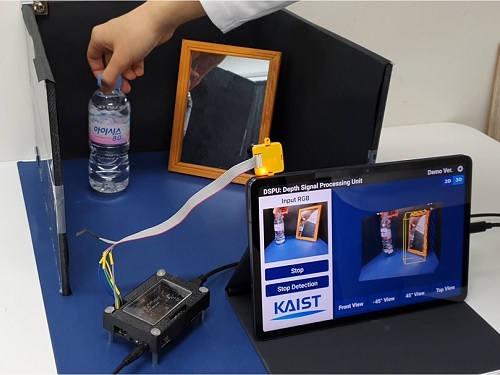

사진에서 3차원 정보를 추론하는 인공지능 반도체 IP(지식재산권) 세계 최초 개발

우리 대학 전기및전자공학부 유회준 교수가 이끄는 PIM 반도체 설계 연구센터(AI-PIM)가 유수 학계에서 인정한 5종의 최첨단 인공지능 반도체 IP(지식재산권)를 개발했다고 29일 밝혔다.

대표적으로 심층신경망 추론 기술 및 센서 퓨전* 기술을 통해 사진으로부터 3차원 공간정보 추출하고 물체를 인식해 처리하는 인공지능(AI) 칩은 KAIST에서 세계 최초로 개발해 SRAM PIM** 시스템에 필요한 기술을 IP(지식재산권)화 한 것이다.

* 센서 퓨전 : 카메라, 거리센서 등의 각종 센서로부터 얻은 데이터를 결합하여보다 정확한 데이터를 얻는 방식

** SRAM PIM : 기존 메모리 SRAM과 DRAM 중 SRAM에 연산기를 결합한 PIM반도체

이 IP는 올해 2월 20일부터 28일까지 개최된 국제고체회로설계학회(ISSCC)에서 현장 시연을 통해 많은 주목을 받았으며, 이를 누구라도 편리하게 활용할 수 있도록 한 것이다. (웹사이트 : www.ai-pim.org)

KAIST PIM 반도체 설계연구센터는 해당 IP를 포함해 ADC*, PLL** 등 총 5가지의 PIM IP를 확보했으며, 지난 28일 웹사이트를 오픈해 연구자들이 공유할 수 있는 환경을 제공하고 있다.

* ADC(Analog to Digital Converter) : 아날로그 데이터를 디지털 데이터로 변환시키는 회로

** PLL(Phase-Locked Loop) : 내부 신호의 위상과 외부 신호의 위상을 동기화할 수 있도록 설계된 회로

기존 물체 인식 인공지능 반도체는 사진과 같은 2차원 정보를 인식하는 `사진인식기술'에 불과하다. 하지만 현실 세계의 물체들은 3차원 구조물이기 때문에 3차원 공간정보를 활용해야만 정확한 `물체인식'이 가능하다.

3차원 공간정보는 사진과 같은 2차원 정보에 거리정보를 포함시켜 실제 3차원 공간을 표현한 것으로, 3차원 공간정보에 물체를 식별해 해당 물체의 위치 및 각도를 추적하는 3차원 물체인식 기술이다. 이는 자율주행, 자동화 기술, 개인용 증강현실 (AR)과 가상현실(VR) 등과 같은 3D 어플리케이션에서 사용하는 핵심기술이다.

기존 ToF 센서*를 활용해 센서 뷰 내에 있는 모든 물체에 대한 정밀한 3차원 정보를 추출하는 것은 전력 소모가 매우 크기 때문에 배터리 기반 모바일 장치(스마트폰, 태블릿 등)에서는 사용하기 어렵다.

* ToF 센서 : 3차원 공간정보를 추출하는 Time-of-Flight 센서로, 레이저를 방출하고 반사된 레이저가 검출되는 시간을 측정하여 거리를 계산, 대표적인 센서로 3D 라이다 (LiDAR) 센서가 있음

또한, ToF 센서는 특정 측정 환경에서 3차원 정보가 손실되는 문제와 데이터 전처리 과정에 많은 시간이 소요된다는 문제점이 있다.

3차원 물체인식 기술은 데이터가 복잡해 기존 인공지능 2차원 사진인식 가속 프로세서로 처리하기 어렵다. 이는 3차원 포인트 클라우드 데이터를 어떻게 선택하고 그룹화하느냐에 따라 메모리 접근량이 달라진다.

따라서 3차원 포인트 클라우드 기반 인공지능 추론은 연산 능력이 제한적이고 메모리가 작은 모바일 장치에서는 소프트웨어만으로 구현할 수 없었다.

이에 연구팀은 카메라와 저전력 거리센서 (64픽셀)를 사용하여 3차원 공간정보를 생성했고, 모바일에서도 3차원 어플리케이션 구현이 가능한 반도체 (DSPU: Depth Signal Processing Unit)를 개발함으로써 인공지능 반도체의 활용범위를 넓혔다.

모바일 기기에서 저전력 센서를 활용한 3차원 정보 처리 시스템을 구동하면서, 실시간 심층신경망 추론과 센서 퓨전 기술을 가속하기 위해서는 다양한 핵심기술이 필요하다. 인공지능 핵심기술이 적용된 DSPU는 단순 ToF센서에 의존했던 3차원 물체인식 가속기 반도체 대비 63.4% 낮춘 전력 소모와 53.6% 낮춘 지연시간을 달성했다.

PIM반도체 설계연구센터(AI-PIM)의 소장인 유회준 교수는 “이번 연구는 저가의 거리센서와 카메라를 융합해 3차원 데이터 처리를 가능하게 한 인공지능 반도체를 IP화했다는 점에서 의미가 크며, 모바일 기기에서 인공지능 활용 영역을 크게 넓혀 다양한 분야에 응용 및 기술이전을 기대하고 있다”고 연구의 의의를 설명했다.

한편, 이번 연구는 과학기술정보통신부와 정보통신기획평가원의 PIM인공지능반도체핵심기술개발사업을 통해 개발되었으며, 이와 관련해 PIM 반도체 관련 기업과 연구기관에 개발된 IP들의 기술이전 및 활용을 돕고 있다.

2022.12.29 조회수 9374

사진에서 3차원 정보를 추론하는 인공지능 반도체 IP(지식재산권) 세계 최초 개발

우리 대학 전기및전자공학부 유회준 교수가 이끄는 PIM 반도체 설계 연구센터(AI-PIM)가 유수 학계에서 인정한 5종의 최첨단 인공지능 반도체 IP(지식재산권)를 개발했다고 29일 밝혔다.

대표적으로 심층신경망 추론 기술 및 센서 퓨전* 기술을 통해 사진으로부터 3차원 공간정보 추출하고 물체를 인식해 처리하는 인공지능(AI) 칩은 KAIST에서 세계 최초로 개발해 SRAM PIM** 시스템에 필요한 기술을 IP(지식재산권)화 한 것이다.

* 센서 퓨전 : 카메라, 거리센서 등의 각종 센서로부터 얻은 데이터를 결합하여보다 정확한 데이터를 얻는 방식

** SRAM PIM : 기존 메모리 SRAM과 DRAM 중 SRAM에 연산기를 결합한 PIM반도체

이 IP는 올해 2월 20일부터 28일까지 개최된 국제고체회로설계학회(ISSCC)에서 현장 시연을 통해 많은 주목을 받았으며, 이를 누구라도 편리하게 활용할 수 있도록 한 것이다. (웹사이트 : www.ai-pim.org)

KAIST PIM 반도체 설계연구센터는 해당 IP를 포함해 ADC*, PLL** 등 총 5가지의 PIM IP를 확보했으며, 지난 28일 웹사이트를 오픈해 연구자들이 공유할 수 있는 환경을 제공하고 있다.

* ADC(Analog to Digital Converter) : 아날로그 데이터를 디지털 데이터로 변환시키는 회로

** PLL(Phase-Locked Loop) : 내부 신호의 위상과 외부 신호의 위상을 동기화할 수 있도록 설계된 회로

기존 물체 인식 인공지능 반도체는 사진과 같은 2차원 정보를 인식하는 `사진인식기술'에 불과하다. 하지만 현실 세계의 물체들은 3차원 구조물이기 때문에 3차원 공간정보를 활용해야만 정확한 `물체인식'이 가능하다.

3차원 공간정보는 사진과 같은 2차원 정보에 거리정보를 포함시켜 실제 3차원 공간을 표현한 것으로, 3차원 공간정보에 물체를 식별해 해당 물체의 위치 및 각도를 추적하는 3차원 물체인식 기술이다. 이는 자율주행, 자동화 기술, 개인용 증강현실 (AR)과 가상현실(VR) 등과 같은 3D 어플리케이션에서 사용하는 핵심기술이다.

기존 ToF 센서*를 활용해 센서 뷰 내에 있는 모든 물체에 대한 정밀한 3차원 정보를 추출하는 것은 전력 소모가 매우 크기 때문에 배터리 기반 모바일 장치(스마트폰, 태블릿 등)에서는 사용하기 어렵다.

* ToF 센서 : 3차원 공간정보를 추출하는 Time-of-Flight 센서로, 레이저를 방출하고 반사된 레이저가 검출되는 시간을 측정하여 거리를 계산, 대표적인 센서로 3D 라이다 (LiDAR) 센서가 있음

또한, ToF 센서는 특정 측정 환경에서 3차원 정보가 손실되는 문제와 데이터 전처리 과정에 많은 시간이 소요된다는 문제점이 있다.

3차원 물체인식 기술은 데이터가 복잡해 기존 인공지능 2차원 사진인식 가속 프로세서로 처리하기 어렵다. 이는 3차원 포인트 클라우드 데이터를 어떻게 선택하고 그룹화하느냐에 따라 메모리 접근량이 달라진다.

따라서 3차원 포인트 클라우드 기반 인공지능 추론은 연산 능력이 제한적이고 메모리가 작은 모바일 장치에서는 소프트웨어만으로 구현할 수 없었다.

이에 연구팀은 카메라와 저전력 거리센서 (64픽셀)를 사용하여 3차원 공간정보를 생성했고, 모바일에서도 3차원 어플리케이션 구현이 가능한 반도체 (DSPU: Depth Signal Processing Unit)를 개발함으로써 인공지능 반도체의 활용범위를 넓혔다.

모바일 기기에서 저전력 센서를 활용한 3차원 정보 처리 시스템을 구동하면서, 실시간 심층신경망 추론과 센서 퓨전 기술을 가속하기 위해서는 다양한 핵심기술이 필요하다. 인공지능 핵심기술이 적용된 DSPU는 단순 ToF센서에 의존했던 3차원 물체인식 가속기 반도체 대비 63.4% 낮춘 전력 소모와 53.6% 낮춘 지연시간을 달성했다.

PIM반도체 설계연구센터(AI-PIM)의 소장인 유회준 교수는 “이번 연구는 저가의 거리센서와 카메라를 융합해 3차원 데이터 처리를 가능하게 한 인공지능 반도체를 IP화했다는 점에서 의미가 크며, 모바일 기기에서 인공지능 활용 영역을 크게 넓혀 다양한 분야에 응용 및 기술이전을 기대하고 있다”고 연구의 의의를 설명했다.

한편, 이번 연구는 과학기술정보통신부와 정보통신기획평가원의 PIM인공지능반도체핵심기술개발사업을 통해 개발되었으며, 이와 관련해 PIM 반도체 관련 기업과 연구기관에 개발된 IP들의 기술이전 및 활용을 돕고 있다.

2022.12.29 조회수 9374 -

차세대 반도체 핵심소재로 열적으로 안정된 강유전체 소재 최초 개발

우리 대학 전기및전자공학부 전상훈 교수 연구팀이 하프니아 강유전체 소재의 물성적 이해를 바탕으로 반도체 3D 집적 공정에서도 열적으로 안정한 *강유전체 소재를 세계 최초로 개발했다고 12일 밝혔다. 현재 반도체 제조 업계에서 고집적, 고효율의 3D 메모리 소자에 대한 필요성이 꾸준하게 대두되고 있다는 점을 고려할 때, 이번 연구는 강유전체 기반의 3D 메모리 집적 공정에서 핵심 기술로 평가받을 것이라 예상된다.

*강유전체: 외부의 전기장 없이도 스스로 분극을 가지는 재료로서 외부 전기장에 의해 분극의 방향이 바뀔 수 있는 소재를 말한다. 비휘발성 특성이 있어, 기능성 소재로서 메모리 소자에 활용이 가능하지만, 고온에서 열적으로 안정성을 확보해야하는 도전 목표가 남아 있으며, 일반 유전체를 일컫는 상유전체는 외부의 전기장이 없으면 분극 특성을 유지하지 못한다는 점에서 다르다.

하프니아 강유전체 소재는 비휘발성 절연막으로, CMOS 공정 호환성, 동작 속도, 내구성 등의 우수한 물리적 특성을 바탕으로 차세대 반도체의 핵심 소재로써 활발하게 연구되고 있는 물질이다. 하지만 하프니아 소재는 필연적으로 고온에서 비휘발성 특성을 잃고 누설전류가 증가하는 한계를 가진다. 이를 억제하기 위해 세계 유수의 기관들에서 다양한 접근방법들이 보고됐지만, 3D 집적 공정 시에 발생하는 고온의 열처리 조건 (750℃ 이상, 30분)에서 강유전체 박막 내의 일반 유전체 (상유전체) 형성을 억제할 수 없었다.

전상훈 교수 연구팀은 세계 최초로 3D 집적 공정에서 요구되는 고온의 열처리 조건에서도 강유전체 박막 내의 상유전체의 형성을 완벽하게 억제하고 비휘발성 기능을 유지하며 우수한 내구성을 가지는 하프니아 강유전체 소재 및 공정 기술을 개발하는 데에 성공했다. 연구팀은 강유전체 박막 내에 이온 반지름이 작은 원소를 고용하는 도핑 기술을 활용해 강유전체 박막의 결정화 온도를 제어함과 동시에 도펀트의 농도에 따른 운동학적 에너지를 고려해 강유전체 소재의 비휘발성 및 기능성과 열적 안정성을 획기적으로 개선했다.

전상훈 교수 연구팀은 CMOS 공정을 이용해 강유전체 기반의 메모리 소자를 집적했고 고온의 열적 에너지(750℃ 이상, 30분)를 가한 후에도 우수한 강유전성이 발현되는 것을 확인했다. 또한 열적 에너지에 따른 강유전체 소재의 도메인 스위칭 동작을 전기적 측정을 통해 직관적으로 분석할 수 있는 시스템을 개발해 추후, 강유전체 소재의 열적 안정성 연구의 프레임 워크를 구축 및 제시했다. 해당 연구는 학계에서 활발하게 연구되고 있는 강유전체 소재의 기능성과 반도체 제조 업계에서 필요로 했던 강유전체 소재 기반의 3D 메모리 소자 집적 공정 사이의 간극을 줄였다는 점에서 큰 의미를 가진다.

전상훈 교수는 “이번 연구 결과는 답보상태에 있던 강유전체 소재 기반의 3D 메모리 및 회로 집적 기술 개발에 대한 돌파구가 되는 기술이 될 것으로 판단되며, 향후 고집적/고효율의 시스템 개발에 있어 핵심 역할을 할 것”이라고 설명했다.

전기및전자공학부 김기욱 박사 과정이 제1 저자로 수행한 이번 연구는 반도체 소자 및 회로 분야의 최고 권위 학회인‘IEEE 국제전자소자학회(International Electron Devices Meeting) 2022 (IEDM 2022)’에 12월 5일 발표를 마쳤다. 한편 이번 연구는 삼성전자(Samsung Electronics)와 차세대 지능형 반도체 사업단의 지능형 반도체 선도기술개발의 지원을 받아 진행됐다.

2022.12.12 조회수 10018

차세대 반도체 핵심소재로 열적으로 안정된 강유전체 소재 최초 개발

우리 대학 전기및전자공학부 전상훈 교수 연구팀이 하프니아 강유전체 소재의 물성적 이해를 바탕으로 반도체 3D 집적 공정에서도 열적으로 안정한 *강유전체 소재를 세계 최초로 개발했다고 12일 밝혔다. 현재 반도체 제조 업계에서 고집적, 고효율의 3D 메모리 소자에 대한 필요성이 꾸준하게 대두되고 있다는 점을 고려할 때, 이번 연구는 강유전체 기반의 3D 메모리 집적 공정에서 핵심 기술로 평가받을 것이라 예상된다.

*강유전체: 외부의 전기장 없이도 스스로 분극을 가지는 재료로서 외부 전기장에 의해 분극의 방향이 바뀔 수 있는 소재를 말한다. 비휘발성 특성이 있어, 기능성 소재로서 메모리 소자에 활용이 가능하지만, 고온에서 열적으로 안정성을 확보해야하는 도전 목표가 남아 있으며, 일반 유전체를 일컫는 상유전체는 외부의 전기장이 없으면 분극 특성을 유지하지 못한다는 점에서 다르다.

하프니아 강유전체 소재는 비휘발성 절연막으로, CMOS 공정 호환성, 동작 속도, 내구성 등의 우수한 물리적 특성을 바탕으로 차세대 반도체의 핵심 소재로써 활발하게 연구되고 있는 물질이다. 하지만 하프니아 소재는 필연적으로 고온에서 비휘발성 특성을 잃고 누설전류가 증가하는 한계를 가진다. 이를 억제하기 위해 세계 유수의 기관들에서 다양한 접근방법들이 보고됐지만, 3D 집적 공정 시에 발생하는 고온의 열처리 조건 (750℃ 이상, 30분)에서 강유전체 박막 내의 일반 유전체 (상유전체) 형성을 억제할 수 없었다.

전상훈 교수 연구팀은 세계 최초로 3D 집적 공정에서 요구되는 고온의 열처리 조건에서도 강유전체 박막 내의 상유전체의 형성을 완벽하게 억제하고 비휘발성 기능을 유지하며 우수한 내구성을 가지는 하프니아 강유전체 소재 및 공정 기술을 개발하는 데에 성공했다. 연구팀은 강유전체 박막 내에 이온 반지름이 작은 원소를 고용하는 도핑 기술을 활용해 강유전체 박막의 결정화 온도를 제어함과 동시에 도펀트의 농도에 따른 운동학적 에너지를 고려해 강유전체 소재의 비휘발성 및 기능성과 열적 안정성을 획기적으로 개선했다.

전상훈 교수 연구팀은 CMOS 공정을 이용해 강유전체 기반의 메모리 소자를 집적했고 고온의 열적 에너지(750℃ 이상, 30분)를 가한 후에도 우수한 강유전성이 발현되는 것을 확인했다. 또한 열적 에너지에 따른 강유전체 소재의 도메인 스위칭 동작을 전기적 측정을 통해 직관적으로 분석할 수 있는 시스템을 개발해 추후, 강유전체 소재의 열적 안정성 연구의 프레임 워크를 구축 및 제시했다. 해당 연구는 학계에서 활발하게 연구되고 있는 강유전체 소재의 기능성과 반도체 제조 업계에서 필요로 했던 강유전체 소재 기반의 3D 메모리 소자 집적 공정 사이의 간극을 줄였다는 점에서 큰 의미를 가진다.

전상훈 교수는 “이번 연구 결과는 답보상태에 있던 강유전체 소재 기반의 3D 메모리 및 회로 집적 기술 개발에 대한 돌파구가 되는 기술이 될 것으로 판단되며, 향후 고집적/고효율의 시스템 개발에 있어 핵심 역할을 할 것”이라고 설명했다.

전기및전자공학부 김기욱 박사 과정이 제1 저자로 수행한 이번 연구는 반도체 소자 및 회로 분야의 최고 권위 학회인‘IEEE 국제전자소자학회(International Electron Devices Meeting) 2022 (IEDM 2022)’에 12월 5일 발표를 마쳤다. 한편 이번 연구는 삼성전자(Samsung Electronics)와 차세대 지능형 반도체 사업단의 지능형 반도체 선도기술개발의 지원을 받아 진행됐다.

2022.12.12 조회수 10018 -

고성능 스트레처블 고분자 반도체를 위한 신개념 계면공학법 개발

우리 대학 신소재공학과 강지형 교수, 미국 버클리 대학교 문재완 박사와 미국 스탠퍼드 대학교 제난 바오(Zhenan Bao) 교수 공동연구팀이 고분자 반도체와 회로기판의 경계면을 개선하는 새로운 계면 개질법을 개발하고, 이를 이용해 고성능 스트레처블(늘어나고 유연한) 고분자 반도체를 구현했다고 24일 밝혔다.

고분자 반도체는 기존의 실리콘 기반의 반도체와는 다르게 탄소를 기반으로 구성돼 있으며, 상대적으로 낮은 가격과 대면적 공정이 가능하다는 장점으로 인해 추후 유연 소자, 태양전지, OLED 등의 산업에 응용될 수 있는 차세대 반도체 재료다.

하지만 전기적 성능이 좋은 고분자 반도체는 작은 응력에도 쉽게 깨지는 문제점이 있었다. 일반적으로 고분자 반도체는 결정구조를 많이 가질수록 전기적 성능이 좋아지지만, 이러한 결정구조는 고분자 반도체가 응력에 취약해지게 만들기 때문이다.

이러한 문제점을 해결하기 위해, 기존에는 분자구조의 변화, 첨가제 등을 이용해 고분자 반도체 자체의 기계적 물성을 변화시키는 데 주로 초점을 맞춰왔다.

그러나 기존의 방법들은 기계적 물성이 향상되는 대신 전기적 성질이 악화되고, 각각의 고분자 반도체에 맞는 분자구조를 찾는데 많은 시간이 소요돼 고성능 스트레처블 고분자 반도체 구현에 적합하지 않았다.

우리 대학 강지형 교수와 스탠퍼드 대학교 제난 바오 교수 공동연구팀은 이번 연구에서 고분자 자체의 성질을 변화시키는 것이 아닌 기판과 고분자 반도체 사이의 계면을 개질하는 새로운 방법을 제시했다. 이러한 계면 공학법을 통해 고분자 반도체는 전기적 성질을 잃지 않으면서 기계적 물성이 크게 개선됐다.

공동연구팀은 이번 연구에서 응력에 의해 고분자 반도체가 손상을 받는 것은 고분자 박막과 기판 사이 계면에서의 박리 현상과 그로 인한 응력의 편재화(localization)에 의해 상당 부분 기인함을 발견했다.

공동연구팀은 이러한 문제점을 극복하기 위해 고분자 반도체 박막과 기판 사이의 계면에 새로운 고분자 층을 도입했다. 이 고분자 층은 반도체 박막과 기판 모두와 강하게 결합해 두 층의 박리현상과 응력의 편재화를 효과적으로 막아줬으며, 동역학적 결합(dynamic bond)을 할 수 있는 구조를 가져 추가적인 응력 분산 효과를 보였다.

이러한 계면 개질이 이뤄진 고성능 고분자 반도체는 최대 110%의 변형률까지 눈에 띄는 균열이 발견되지 않았으며, 이는 기존의 같은 반도체가 30% 변형률에서 상당한 균열을 보인 것에 비하면 획기적인 발전이다. 또한 이러한 접근법은 특정 고분자 반도체에 국한되지 않고, 다양한 고분자 반도체, 고분자 전도체, 금속 전도체에 모두 적용 가능하다는 장점이 있다.

신소재공학과 강지형 교수와 스탠퍼드 대학교 문재완 박사가 공동 제1 저자로 참여한 이번 연구 결과는 나노 재료 분야 저명 국제 학술지 `네이처 나노테크놀로지 (Nature Nanotechnology)' 11월 10일 字 온라인판에 게재됐다. (논문명 : Tough interface-enabled stretchable electronics using non-stretchable polymer semiconductors and conductors).

강지형 교수는 "이번 연구는 스트레처블 고분자 반도체 구현을 위한 설계 방향을 새롭게 제시했다는 점에서 의미가 있다ˮ고 하면서, "이번에 개발된 계면 공학법은 급속도로 성장하고 있는 유연소자 시장에 게임 체인저가 될 것으로 기대된다ˮ고 말했다.

한편 이번 연구는 한국연구재단의 우수신진연구사업, 나노소재기술개발사업 미래기술연구실, 삼성종기원 과제의 지원을 받아 수행됐다.

2022.11.25 조회수 9461

고성능 스트레처블 고분자 반도체를 위한 신개념 계면공학법 개발

우리 대학 신소재공학과 강지형 교수, 미국 버클리 대학교 문재완 박사와 미국 스탠퍼드 대학교 제난 바오(Zhenan Bao) 교수 공동연구팀이 고분자 반도체와 회로기판의 경계면을 개선하는 새로운 계면 개질법을 개발하고, 이를 이용해 고성능 스트레처블(늘어나고 유연한) 고분자 반도체를 구현했다고 24일 밝혔다.

고분자 반도체는 기존의 실리콘 기반의 반도체와는 다르게 탄소를 기반으로 구성돼 있으며, 상대적으로 낮은 가격과 대면적 공정이 가능하다는 장점으로 인해 추후 유연 소자, 태양전지, OLED 등의 산업에 응용될 수 있는 차세대 반도체 재료다.

하지만 전기적 성능이 좋은 고분자 반도체는 작은 응력에도 쉽게 깨지는 문제점이 있었다. 일반적으로 고분자 반도체는 결정구조를 많이 가질수록 전기적 성능이 좋아지지만, 이러한 결정구조는 고분자 반도체가 응력에 취약해지게 만들기 때문이다.

이러한 문제점을 해결하기 위해, 기존에는 분자구조의 변화, 첨가제 등을 이용해 고분자 반도체 자체의 기계적 물성을 변화시키는 데 주로 초점을 맞춰왔다.

그러나 기존의 방법들은 기계적 물성이 향상되는 대신 전기적 성질이 악화되고, 각각의 고분자 반도체에 맞는 분자구조를 찾는데 많은 시간이 소요돼 고성능 스트레처블 고분자 반도체 구현에 적합하지 않았다.

우리 대학 강지형 교수와 스탠퍼드 대학교 제난 바오 교수 공동연구팀은 이번 연구에서 고분자 자체의 성질을 변화시키는 것이 아닌 기판과 고분자 반도체 사이의 계면을 개질하는 새로운 방법을 제시했다. 이러한 계면 공학법을 통해 고분자 반도체는 전기적 성질을 잃지 않으면서 기계적 물성이 크게 개선됐다.

공동연구팀은 이번 연구에서 응력에 의해 고분자 반도체가 손상을 받는 것은 고분자 박막과 기판 사이 계면에서의 박리 현상과 그로 인한 응력의 편재화(localization)에 의해 상당 부분 기인함을 발견했다.

공동연구팀은 이러한 문제점을 극복하기 위해 고분자 반도체 박막과 기판 사이의 계면에 새로운 고분자 층을 도입했다. 이 고분자 층은 반도체 박막과 기판 모두와 강하게 결합해 두 층의 박리현상과 응력의 편재화를 효과적으로 막아줬으며, 동역학적 결합(dynamic bond)을 할 수 있는 구조를 가져 추가적인 응력 분산 효과를 보였다.

이러한 계면 개질이 이뤄진 고성능 고분자 반도체는 최대 110%의 변형률까지 눈에 띄는 균열이 발견되지 않았으며, 이는 기존의 같은 반도체가 30% 변형률에서 상당한 균열을 보인 것에 비하면 획기적인 발전이다. 또한 이러한 접근법은 특정 고분자 반도체에 국한되지 않고, 다양한 고분자 반도체, 고분자 전도체, 금속 전도체에 모두 적용 가능하다는 장점이 있다.

신소재공학과 강지형 교수와 스탠퍼드 대학교 문재완 박사가 공동 제1 저자로 참여한 이번 연구 결과는 나노 재료 분야 저명 국제 학술지 `네이처 나노테크놀로지 (Nature Nanotechnology)' 11월 10일 字 온라인판에 게재됐다. (논문명 : Tough interface-enabled stretchable electronics using non-stretchable polymer semiconductors and conductors).

강지형 교수는 "이번 연구는 스트레처블 고분자 반도체 구현을 위한 설계 방향을 새롭게 제시했다는 점에서 의미가 있다ˮ고 하면서, "이번에 개발된 계면 공학법은 급속도로 성장하고 있는 유연소자 시장에 게임 체인저가 될 것으로 기대된다ˮ고 말했다.

한편 이번 연구는 한국연구재단의 우수신진연구사업, 나노소재기술개발사업 미래기술연구실, 삼성종기원 과제의 지원을 받아 수행됐다.

2022.11.25 조회수 9461 -

세계 최초 네트워크 기술이 적용된 SSD 시스템 반도체 개발

우리 대학 전기및전자공학부 김동준 교수 연구팀이 세계 최초로 `패킷 기반 네트워크' 기술이 적용된 SSD(Solid State Drive, 반도체 기억소자를 사용한 저장장치) 시스템 개발을 통해 차세대 SSD의 읽기/쓰기 성능을 비약적으로 높이는 시스템 반도체를 개발했다고 28일 밝혔다.

패킷이란 다양한 크기를 지닌 데이터를 일정한 크기로 분할한 후 제어 정보를 추가한 데이터 전송의 기본 단위를 말하며, 효율적이고 신뢰성 있게 데이터를 전송할 수 있다는 장점이 있어 주로 컴퓨터 네트워크 기반 정보 기술에서 사용되고 있다. 최근 시스템 반도체 분야에서는 다양한 계산 자원들을 칩 내부 네트워크로 연결하여 효율적으로 활용하는 기술이 적용되고 있다. 본 연구는 이러한 시스템 반도체 분야에서 효과적인 네트워크 연결 기술을 메모리 반도체에 적용하였다는 점에서 큰 의미를 가지고 있다.

SSD는 플래시메모리를 이용해 정보를 저장하는 장치로, 기존 자기디스크를 이용한 데이터 저장장치인 `하드디스크 드라이브(HDD)'에 비해 데이터 입출력(읽기/쓰기) 속도가 빠르고 발열과 소음이 적어 데이터 센터 및 클라우드 서비스를 위한 주요 저장장치로 활용되고 있다. 전 세계적으로 수십억 명이 사용하는 페이스북(Facebook), 트위터(Twitter) 등과 같은 SNS 서비스를 제공하는 기업들뿐만 아니라 구글, 마이크로소프트 등과 같이 수십억 명의 사용자 정보를 저장하고 이를 활용해 서비스를 제공하는 기업들은 더 많은 데이터를 저장하고 성능이 좋은 고용량/고성능 SSD 제품을 필요로 한다.

특히 인터넷 서비스 제공 기업들은 많은 양의 정보가 데이터 센터에서 저장되고 처리되면서 더 많은 데이터를 저장할 수 있고, 더 빠르게 데이터를 읽고 쓰는 것이 가능한 고성능 SSD 제품을 요구한다. 따라서 SSD는 지속해서 성능과 용량의 개선을 요구하는 상황에 놓이게 된다.

이에 삼성, SK 하이닉스, 등과 같은 SSD 및 메모리를 제공하는 기업에서는 고성능 SSD 기술에 크게 주목하고 있으며, 이는 많은 애플리케이션의 성능 향상에 도움이 될 뿐만 아니라 비용적인 측면에서도 효율적으로 서버 시스템을 확장하는 데 도움이 될 것으로 기대하고 있다.

하지만 이러한 장점에도 불구하고, 고용량 및 고성능 SSD를 위해 규모를 증가시키는 스케일 업(scale-up)은 하드웨어 패키징 한계에 제한돼 쉽게 확장하기 어렵다. 무엇보다도 기존 SSD 시스템은 사용 가능한 처리량 (bandwidth)이 있음에도 불구하고 효율적으로 사용하지 못하는 비효율적인 데이터 송수신 방식 채택해 사용하고 있다.

이에 김동준 교수 연구팀은 기존 SSD 시스템 설계를 분석해 CPU, GPU 등과 같은 비메모리 시스템 반도체 설계에서 주로 활용되는 네트워크 기술을 적용해 SSD 성능을 크게 높일 수 있는 `네트워크 기술이 적용된 SSD 시스템 반도체'를 개발했다. 김동준 교수팀이 개발한 SSD 시스템은 플래시 인터커넥트(interconnection network) 와 패킷 기반 플래시 컨트롤러 (packet-based flash controller) 등으로 구성되어 있으며, 현재 사용되는 기존 SSD 시스템 대비 2배 많은 처리량을 제공하고 응답시간을 약 10배 줄인 성능을 보인다고 연구팀 관계자는 설명했다.

또한 이번 개발을 통해서 기존 하드웨어의 한계를 비메모리 시스템 반도체에서 주로 사용되는 패킷(packet) 기반 송수신 기법의 사용으로 극복해 고성능 SSD 기술에 도움을 줄 수 있을 것으로 기대된다고 연구팀 관계자는 설명했다.

전기및전자공학부 김지호 박사과정이 제1 저자로, 한양대학교 컴퓨터소프트웨어학과 강석원 박사과정, 박영준 연세대학교 컴퓨터과학과 교수가 공동 저자로 참여한 이번 연구는 미국 시카고에서 열리는 컴퓨터 구조 분야 최우수 국제 학술대회인 `55th IEEE/ACM International Symposium on Microarchitecture (MICRO 2022)'에서 오늘 10월 발표될 예정이다. (논문명 : Networked SSD: Flash Memory Interconnection Network for High-Bandwidth SSD)

연구를 주도한 김동준 교수는 "이번 연구는 지금까지는 없던 네트워크 패킷(packet)이 적용된 SSD 시스템 반도체를 세계 최초로 개발했다는 점에서 의의가 있으며, 데이터 센터 및 클라우드 서비스 시장에서 지속적으로 증가하는 고성능 SSD 요구에 발맞춰 큰 도움을 줄 수 있을 것으로 보인다ˮ며, "SSD의 성능 향상은 인공지능 연구 및 빅데이터 분석 기술을 활용하는 다양한 알고리즘 성능 개선에도 기여할 것으로 보인다ˮ고 연구의 의의를 설명했다.

한편 이번 연구는 한국연구재단과 정보통신기획평가원 차세대지능형반도체기술개발사업의 지원을 받아 수행됐다.

2022.09.28 조회수 10369

세계 최초 네트워크 기술이 적용된 SSD 시스템 반도체 개발

우리 대학 전기및전자공학부 김동준 교수 연구팀이 세계 최초로 `패킷 기반 네트워크' 기술이 적용된 SSD(Solid State Drive, 반도체 기억소자를 사용한 저장장치) 시스템 개발을 통해 차세대 SSD의 읽기/쓰기 성능을 비약적으로 높이는 시스템 반도체를 개발했다고 28일 밝혔다.

패킷이란 다양한 크기를 지닌 데이터를 일정한 크기로 분할한 후 제어 정보를 추가한 데이터 전송의 기본 단위를 말하며, 효율적이고 신뢰성 있게 데이터를 전송할 수 있다는 장점이 있어 주로 컴퓨터 네트워크 기반 정보 기술에서 사용되고 있다. 최근 시스템 반도체 분야에서는 다양한 계산 자원들을 칩 내부 네트워크로 연결하여 효율적으로 활용하는 기술이 적용되고 있다. 본 연구는 이러한 시스템 반도체 분야에서 효과적인 네트워크 연결 기술을 메모리 반도체에 적용하였다는 점에서 큰 의미를 가지고 있다.

SSD는 플래시메모리를 이용해 정보를 저장하는 장치로, 기존 자기디스크를 이용한 데이터 저장장치인 `하드디스크 드라이브(HDD)'에 비해 데이터 입출력(읽기/쓰기) 속도가 빠르고 발열과 소음이 적어 데이터 센터 및 클라우드 서비스를 위한 주요 저장장치로 활용되고 있다. 전 세계적으로 수십억 명이 사용하는 페이스북(Facebook), 트위터(Twitter) 등과 같은 SNS 서비스를 제공하는 기업들뿐만 아니라 구글, 마이크로소프트 등과 같이 수십억 명의 사용자 정보를 저장하고 이를 활용해 서비스를 제공하는 기업들은 더 많은 데이터를 저장하고 성능이 좋은 고용량/고성능 SSD 제품을 필요로 한다.

특히 인터넷 서비스 제공 기업들은 많은 양의 정보가 데이터 센터에서 저장되고 처리되면서 더 많은 데이터를 저장할 수 있고, 더 빠르게 데이터를 읽고 쓰는 것이 가능한 고성능 SSD 제품을 요구한다. 따라서 SSD는 지속해서 성능과 용량의 개선을 요구하는 상황에 놓이게 된다.

이에 삼성, SK 하이닉스, 등과 같은 SSD 및 메모리를 제공하는 기업에서는 고성능 SSD 기술에 크게 주목하고 있으며, 이는 많은 애플리케이션의 성능 향상에 도움이 될 뿐만 아니라 비용적인 측면에서도 효율적으로 서버 시스템을 확장하는 데 도움이 될 것으로 기대하고 있다.

하지만 이러한 장점에도 불구하고, 고용량 및 고성능 SSD를 위해 규모를 증가시키는 스케일 업(scale-up)은 하드웨어 패키징 한계에 제한돼 쉽게 확장하기 어렵다. 무엇보다도 기존 SSD 시스템은 사용 가능한 처리량 (bandwidth)이 있음에도 불구하고 효율적으로 사용하지 못하는 비효율적인 데이터 송수신 방식 채택해 사용하고 있다.

이에 김동준 교수 연구팀은 기존 SSD 시스템 설계를 분석해 CPU, GPU 등과 같은 비메모리 시스템 반도체 설계에서 주로 활용되는 네트워크 기술을 적용해 SSD 성능을 크게 높일 수 있는 `네트워크 기술이 적용된 SSD 시스템 반도체'를 개발했다. 김동준 교수팀이 개발한 SSD 시스템은 플래시 인터커넥트(interconnection network) 와 패킷 기반 플래시 컨트롤러 (packet-based flash controller) 등으로 구성되어 있으며, 현재 사용되는 기존 SSD 시스템 대비 2배 많은 처리량을 제공하고 응답시간을 약 10배 줄인 성능을 보인다고 연구팀 관계자는 설명했다.

또한 이번 개발을 통해서 기존 하드웨어의 한계를 비메모리 시스템 반도체에서 주로 사용되는 패킷(packet) 기반 송수신 기법의 사용으로 극복해 고성능 SSD 기술에 도움을 줄 수 있을 것으로 기대된다고 연구팀 관계자는 설명했다.

전기및전자공학부 김지호 박사과정이 제1 저자로, 한양대학교 컴퓨터소프트웨어학과 강석원 박사과정, 박영준 연세대학교 컴퓨터과학과 교수가 공동 저자로 참여한 이번 연구는 미국 시카고에서 열리는 컴퓨터 구조 분야 최우수 국제 학술대회인 `55th IEEE/ACM International Symposium on Microarchitecture (MICRO 2022)'에서 오늘 10월 발표될 예정이다. (논문명 : Networked SSD: Flash Memory Interconnection Network for High-Bandwidth SSD)

연구를 주도한 김동준 교수는 "이번 연구는 지금까지는 없던 네트워크 패킷(packet)이 적용된 SSD 시스템 반도체를 세계 최초로 개발했다는 점에서 의의가 있으며, 데이터 센터 및 클라우드 서비스 시장에서 지속적으로 증가하는 고성능 SSD 요구에 발맞춰 큰 도움을 줄 수 있을 것으로 보인다ˮ며, "SSD의 성능 향상은 인공지능 연구 및 빅데이터 분석 기술을 활용하는 다양한 알고리즘 성능 개선에도 기여할 것으로 보인다ˮ고 연구의 의의를 설명했다.

한편 이번 연구는 한국연구재단과 정보통신기획평가원 차세대지능형반도체기술개발사업의 지원을 받아 수행됐다.

2022.09.28 조회수 10369 -

세계 최초 개인정보 보호 기술이 적용된 인공지능(AI) 반도체 개발

우리 대학 전기및전자공학부 유민수 교수 연구팀이 세계 최초로 `차등 프라이버시 기술이 적용된 인공지능(AI) 어플리케이션(Differentially private machine learning)'의 성능을 비약적으로 높이는 인공지능 반도체를 개발했다고 19일 밝혔다.

빅데이터 및 인공지능 기술의 발전과 함께 구글, 애플, 마이크로소프트 등 클라우드 서비스를 제공하는 기업들은 전 세계 수십억 명의 사용자들에게 인공지능 기술을 기반으로 여러 가지 서비스(머신러닝 애즈 어 서비스, ML-as-a-Service, MLaaS)를 제공하고 있다. 이러한 서비스 중에는, 대표적으로 유튜브나 페이스북 등에서 시청자의 개별 취향에 맞춰 동영상 콘텐츠나 상품 등을 추천하는 `개인화 추천 시스템 기술(예- 딥러닝 추천 모델, Deep Learning Recommendation Model)' 이나, 구글 포토(Photo) 와 애플 아이클라우드(iCloud) 등에서 사진을 인물 별로 분류해주는 `안면 인식 기술 (예- 합성곱 신경망 네트워크 안면 인식, Convolutional Neural Network based Face Recognition)' 등이 있다.

이와 같은 서비스는 사용자의 정보를 대량으로 수집해, 이를 기반으로 인공지능 알고리즘의 정확도와 성능을 개선한다. 이 과정에서 필연적으로 많은 양의 사용자 정보가 서비스 제공 기업의 데이터 센터로 전송되고, 민감한 개인정보나 파일들이 저장되고 사용되는 과정에서 정보가 유출되는 문제가 발생하기도 한다.

또한 이러한 문제는 최근 주목받는 대형 인공지능 모델의 경우에 더 쉽게 발생하는 경향이 있으며, 실제 구글에서 사용하는 대화형 인공지능 모델인 GPT-2의 경우, 특정 단어들을 이야기했을 때 사용자의 개인정보 등을 유출하는 문제를 보였다. [참고1] 유사사례로서 국내에서 2020년 화제가 되었던 스캐터랩의 인공지능 챗봇 이루다의 경우에도 비슷한 문제가 불거진 적이 있다. [참고2]

[참고1] https://ai.googleblog.com/2020/12/privacy-considerations-in-large.html

[참고2] https://n.news.naver.com/mnews/article/092/0002243051?sid=105

이에 애플, 구글, 마이크로소프트 등 빅 테크 기업에서는 `차등 프라이버시 (differential privacy)' 기술을 크게 주목하고 있다. 차등 프라이버시 기술은 학습에 사용되는 그라디언트(gradient, 학습 방향 기울기)에 잡음(노이즈)를 섞음으로써 인공지능 모델로부터 사용자의 개인정보를 유출하는 모든 종류의 공격을 방어할 수 있다.

하지만 이러한 장점에도 불구하고, 차등 프라이버시 기술 적용 시, 기존 대비 어플리케이션의 속도와 성능이 크게 하락하는 문제 때문에 아직까지 범용적으로 널리 적용되지는 못했다. 이는 차등 프라이버시 머신러닝 학습 과정이 일반적인 머신러닝 학습과 다른 특성을 보이고, 이로 인해 기존의 하드웨어에서 효과적으로 실행되지 않아 메모리 사용량, 학습 속도 및 하드웨어 활용도 (hardware utilization) 측면에서 비효율적이기 때문이다.

이에 유민수 교수 연구팀은 차등 프라이버시 기술의 성능 병목 구간을 분석해 해당 기술이 적용된 어플리케이션의 성능을 크게 시킬 수 있는 `차등 프라이버시 머신러닝을 위한 인공지능(AI) 반도체 칩'을 개발했다. 유민수 교수팀이 개발한 인공지능 반도체는 외적 기반 연산기와 덧셈기 트리 기반의 후처리 연산기 등으로 구성돼 있으며, 현재 가장 널리 사용되는 인공지능 프로세서인 구글 TPUv3 대비 차등 프라이버시 인공지능 학습 과정을 3.6 배 빠르게 실행시킬 수 있고, 엔비디아의 최신 GPU A100 대비 10배 적은 자원으로 대등한 성능을 보인다고 연구팀 관계자는 설명했다. 또한 이번 개발을 통해서 기존 하드웨어의 한계로 널리 쓰이지 못했던 차등 정보보호 기술의 대중화에 도움을 줄 수 있을 것으로 기대된다고 전했다.

우리 대학 전기및전자공학부 박범식, 황랑기 연구원이 공동 제1 저자로, 윤동호, 최윤혁 연구원이 공동 저자로 참여한 이번 연구는 미국 시카고에서 열리는 컴퓨터 구조 분야 최우수 국제 학술대회인 `55th IEEE/ACM International Symposium on Microarchitecture(MICRO 2022)'에서 오늘 10월 발표될 예정이다. (논문명 : DiVa: An Accelerator for Differentially Private Machine Learning)

또한 이번 연구는 지금까지는 없던 차등 프라이버시가 적용된 인공지능 반도체를 세계 최초로 개발했다는 점에서 의의가 있으며, 차등 프라이버시 인공지능 기술을 대중화해 인공지능 기반 서비스 사용자들의 개인정보를 보호하는 데에 큰 도움을 줄 수 있을 것으로 보인다. 또한, 가속기의 성능 향상은 인공지능 연구 효율을 높여 차등 프라이버시 인공지능 모델의 정확도 개선에도 기여할 것으로 보인다.

한편 이번 연구는 한국연구재단, 삼성전자, 그리고 반도체설계교육센터 (IDEC, IC Design Education Center)의 지원을 받아 수행됐다.

2022.08.19 조회수 13036

세계 최초 개인정보 보호 기술이 적용된 인공지능(AI) 반도체 개발

우리 대학 전기및전자공학부 유민수 교수 연구팀이 세계 최초로 `차등 프라이버시 기술이 적용된 인공지능(AI) 어플리케이션(Differentially private machine learning)'의 성능을 비약적으로 높이는 인공지능 반도체를 개발했다고 19일 밝혔다.

빅데이터 및 인공지능 기술의 발전과 함께 구글, 애플, 마이크로소프트 등 클라우드 서비스를 제공하는 기업들은 전 세계 수십억 명의 사용자들에게 인공지능 기술을 기반으로 여러 가지 서비스(머신러닝 애즈 어 서비스, ML-as-a-Service, MLaaS)를 제공하고 있다. 이러한 서비스 중에는, 대표적으로 유튜브나 페이스북 등에서 시청자의 개별 취향에 맞춰 동영상 콘텐츠나 상품 등을 추천하는 `개인화 추천 시스템 기술(예- 딥러닝 추천 모델, Deep Learning Recommendation Model)' 이나, 구글 포토(Photo) 와 애플 아이클라우드(iCloud) 등에서 사진을 인물 별로 분류해주는 `안면 인식 기술 (예- 합성곱 신경망 네트워크 안면 인식, Convolutional Neural Network based Face Recognition)' 등이 있다.

이와 같은 서비스는 사용자의 정보를 대량으로 수집해, 이를 기반으로 인공지능 알고리즘의 정확도와 성능을 개선한다. 이 과정에서 필연적으로 많은 양의 사용자 정보가 서비스 제공 기업의 데이터 센터로 전송되고, 민감한 개인정보나 파일들이 저장되고 사용되는 과정에서 정보가 유출되는 문제가 발생하기도 한다.

또한 이러한 문제는 최근 주목받는 대형 인공지능 모델의 경우에 더 쉽게 발생하는 경향이 있으며, 실제 구글에서 사용하는 대화형 인공지능 모델인 GPT-2의 경우, 특정 단어들을 이야기했을 때 사용자의 개인정보 등을 유출하는 문제를 보였다. [참고1] 유사사례로서 국내에서 2020년 화제가 되었던 스캐터랩의 인공지능 챗봇 이루다의 경우에도 비슷한 문제가 불거진 적이 있다. [참고2]

[참고1] https://ai.googleblog.com/2020/12/privacy-considerations-in-large.html

[참고2] https://n.news.naver.com/mnews/article/092/0002243051?sid=105

이에 애플, 구글, 마이크로소프트 등 빅 테크 기업에서는 `차등 프라이버시 (differential privacy)' 기술을 크게 주목하고 있다. 차등 프라이버시 기술은 학습에 사용되는 그라디언트(gradient, 학습 방향 기울기)에 잡음(노이즈)를 섞음으로써 인공지능 모델로부터 사용자의 개인정보를 유출하는 모든 종류의 공격을 방어할 수 있다.

하지만 이러한 장점에도 불구하고, 차등 프라이버시 기술 적용 시, 기존 대비 어플리케이션의 속도와 성능이 크게 하락하는 문제 때문에 아직까지 범용적으로 널리 적용되지는 못했다. 이는 차등 프라이버시 머신러닝 학습 과정이 일반적인 머신러닝 학습과 다른 특성을 보이고, 이로 인해 기존의 하드웨어에서 효과적으로 실행되지 않아 메모리 사용량, 학습 속도 및 하드웨어 활용도 (hardware utilization) 측면에서 비효율적이기 때문이다.

이에 유민수 교수 연구팀은 차등 프라이버시 기술의 성능 병목 구간을 분석해 해당 기술이 적용된 어플리케이션의 성능을 크게 시킬 수 있는 `차등 프라이버시 머신러닝을 위한 인공지능(AI) 반도체 칩'을 개발했다. 유민수 교수팀이 개발한 인공지능 반도체는 외적 기반 연산기와 덧셈기 트리 기반의 후처리 연산기 등으로 구성돼 있으며, 현재 가장 널리 사용되는 인공지능 프로세서인 구글 TPUv3 대비 차등 프라이버시 인공지능 학습 과정을 3.6 배 빠르게 실행시킬 수 있고, 엔비디아의 최신 GPU A100 대비 10배 적은 자원으로 대등한 성능을 보인다고 연구팀 관계자는 설명했다. 또한 이번 개발을 통해서 기존 하드웨어의 한계로 널리 쓰이지 못했던 차등 정보보호 기술의 대중화에 도움을 줄 수 있을 것으로 기대된다고 전했다.

우리 대학 전기및전자공학부 박범식, 황랑기 연구원이 공동 제1 저자로, 윤동호, 최윤혁 연구원이 공동 저자로 참여한 이번 연구는 미국 시카고에서 열리는 컴퓨터 구조 분야 최우수 국제 학술대회인 `55th IEEE/ACM International Symposium on Microarchitecture(MICRO 2022)'에서 오늘 10월 발표될 예정이다. (논문명 : DiVa: An Accelerator for Differentially Private Machine Learning)

또한 이번 연구는 지금까지는 없던 차등 프라이버시가 적용된 인공지능 반도체를 세계 최초로 개발했다는 점에서 의의가 있으며, 차등 프라이버시 인공지능 기술을 대중화해 인공지능 기반 서비스 사용자들의 개인정보를 보호하는 데에 큰 도움을 줄 수 있을 것으로 보인다. 또한, 가속기의 성능 향상은 인공지능 연구 효율을 높여 차등 프라이버시 인공지능 모델의 정확도 개선에도 기여할 것으로 보인다.

한편 이번 연구는 한국연구재단, 삼성전자, 그리고 반도체설계교육센터 (IDEC, IC Design Education Center)의 지원을 받아 수행됐다.

2022.08.19 조회수 13036 -

KAIST, 인공지능 반도체 생태계를 선도하다

인공지능 반도체(이하 AI 반도체)가 국가적인 전략기술로 두드러지면서 KAIST의 관련 성과도 주목받고 있다. 과학기술정보통신부는 지난해 2030년 세계 AI 반도체 시장 20% 점유를 목표로 인공지능 반도체 지원사업에 본격적으로 착수한 바 있다. 올해에는 산학연 논의를 거쳐 5년간 1조 200억 원을 투입하는 `인공지능 반도체 산업 성장 지원대책'으로 지원을 확대했다. 이에 따라 AI 반도체 전문가 양성을 위해 주요 대학들의 행보도 분주해졌다.

KAIST는 반도체와 인공지능 양대 핵심 분야에서 최상급의 교육, 연구 역량을 쌓아 왔다. 반도체 분야에서는 지난 17년 동안 메사추세츠 공과대학(이하 MIT), 스탠퍼드(Stanford)와 같은 세계적인 학교를 제치고 국제반도체회로학회(이하 ISSCC, International Solid State Circuit Conference)에서 대학 중 1위를 지켜 왔다는 점이 돋보인다. ISSCC는 1954년 설립된 반도체 집적회로 설계 분야 세계 최고 권위 학회다. 참가자 중 60% 이상이 삼성, 퀄컴, TSMC, 인텔을 비롯한 산업계 소속일만큼 산업적인 실용성을 중시해서 `반도체 설계 올림픽'이라는 별명도 있다.

KAIST는 ISSCC에서 채택 논문 수 기준 매년 전 세계 대학교 중 1~2위를 유지했다. 최근 17년간 평균 채택 논문 수를 살펴보면 압도적인 선두다. 해당 기간 채택된 KAIST의 논문은 평균 8.4편으로, 경쟁자인 MIT(4.6편)와 캘리포니아대학교 로스앤젤레스(UCLA)(3.6편)에 비해 두 배 가까운 성과다. 국내에서는 반도체 설계 분야 부동의 1위인 삼성에 이어 종합 2위 자리를 유지하고 있다. 그럴 뿐만 아니라 ISSCC와 쌍벽을 이루는 집적회로 분야 학술대회인 초고밀도집적회로학회에서도 KAIST는 2022년 전 세계 대학 중 1위를 기록했다.

KAIST의 연구진들이 반도체 산업 핵심 분야 전반에서 신기술을 발표해 연구의 질적인 수준도 높다. 전기및전자공학부 정명수 교수 연구팀은 고성능 저전력을 추구하는 현재 업계의 수요에 대응해 전력 공급 없이도 동작을 유지하는 컴퓨터를 개발했다. 소재 분야에서는 신소재공학과의 박병국 교수 연구팀이 기존의 메모리에 비해 동작 속도가 10배 이상 빠른 `스핀궤도토크 자성메모리' 소자를 개발해서 기존 `폰노이만 구조'의 한계를 극복하는 방안을 제시하기도 했다.

이처럼 현재 반도체 산업의 주요 과제에 솔루션을 제공하는 한편으로 미래의 새로운 반도체 분야를 선점하는 데 필요한 신기술 개발도 활발하다. 암호 및 비선형 연산 분야에서 차세대 컴퓨팅으로 주목받는 양자컴퓨팅 분야에서는 전기및전자공학부 김상현 교수 연구팀이 3차원 집적 기술을 세계 최초로 선보였다. 신경계의 원리를 활용해 인공지능 분야에서 발군의 성능을 보일 것으로 기대되는 뉴로모픽 컴퓨팅에서는 전기및전자공학부 최신현 교수 연구팀이 신경세포를 모사하는 차세대 멤리스터를 개발 중이다.

인공지능 분야에서도 비약적으로 성장했다. 인공지능 분야의 양대 세계 최고 권위 학회인 국제머신러닝학회(ICML)과 인공신경망학회(NeurIPS) 논문 수 기준으로 KAIST는 2020년 세계 6위, 아시아에서는 1위를 기록했다. KAIST의 순위는 2012년부터 꾸준히 우상향 그래프를 그려 8년만에 37위에서 6위로, 무려 31계단이나 도약했다. 2021년에는 인공지능 분야 톱 학회 11개에 발표된 한국 논문 중 약 40%에 달하는 129편이 KAIST에서 나왔다. KAIST의 이러한 활약에 힘입어 2021년 한국은 글로벌 인공지능 톱 학회 등재 논문 수 기준으로 미국, 중국, 영국, 캐나다, 독일에 이어 6위에 올랐다.

내용 면에서도 KAIST의 인공지능 연구는 최전선에 있다. 전기및전자공학부 유회준 교수 연구팀은 모바일기기에서 인공지능 실시간 학습을 구현해 에지 네트워크의 단점을 보완했다. 인공지능을 구현하려면 데이터 축적관 막대한 양의 연산이 필요한데, 이를 위해 고성능 서버가 방대한 연산을 담당하고 사용자 단말은 데이터 수집과 간단한 연산만 하는 `에지 네트워크'가 사용된다. 유 교수의 연구는 사용자 단말에 학습 능력을 부여함으로써 인공지능의 처리 속도와 성능을 크게 높일 수 있다.

지난 6월에는 전산학부 김민수 교수 연구팀이 초대규모 인공지능 모델 처리에 꼭 필요한 솔루션을 제시했다. 연구팀이 개발한 초대규모 기계학습 시스템은 현재 업계에서 주로 사용되는 구글의 텐서플로우(Tensorflow)나 IBM의 시스템DS 대비 최대 8.8배나 빠른 속도를 달성할 수 있을 것으로 기대된다.

KAIST는 반도체와 인공지능이 결합된 AI 반도체 분야에서도 주목할만한 성과를 내고 있다. 2020년 전기및전자공학부 유민수 교수 연구팀은 세계 최초로 추천시스템에 최적화된 AI 반도체를 개발하는 데 성공했다. 인공지능 추천시스템은 방대한 콘텐츠와 사용자 정보를 다룬다는 특성상 범용 인공지능 시스템으로 운영하면 병목현상으로 성능에 한계가 있다. 유민수 교수팀은 `프로세싱-인-메모리(이하 PIM, Processing-In-Memory)' 기술을 기반으로 기존 시스템 대비 최대 21배 빠른 속도를 낼 수 있는 반도체를 개발했다. PIM은 처리할 데이터를 임시로 저장하기만 하던 `램'에서 연산까지 수행해 효율을 높이는 기술이다. PIM 기술이 본격적으로 상용화되면 메모리 분야에서 강세인 한국 기업의 AI 반도체 시장 경쟁력이 비약적으로 높아질 것으로 기대된다.

KAIST는 그간의 성과에 안주하지 않고 인공지능 및 반도체, 그리고 AI 반도체 분야 초격차를 유지하고자 다각적인 노력을 기울이고 있다. 1990년 국내 최초로 인공지능연구센터를 설립한 데 이어 2019년에는 김재철AI대학원을 개설해 전문인력을 양성 중이다. 2020년에는 인공지능과 반도체 연구를 융합해 ITRC 인공지능반도체시스템 연구센터가 출범했으며, 2021년에는 인공지능을 다양한 분야에 접목하는 `AI+X' 연구를 활성화하고자 김재철AI대학원과 별도로 AI 연구원을 설립했다.

KAIST는 이러한 노력으로 축적된 내적 역량을 바탕으로 네이버 등 기업과 공동연구센터를 설립하는 한편, 화성시와 같은 지자체와 협력해 동시다발적인 전문인력 양성에 나섰다. 지난 2021년에는 삼성전자와 함께 반도체시스템공학과 설립 협약을 체결하고 새로운 반도체 전문인력 교육과정을 준비하고 있다. 새로 설립되는 반도체시스템공학과는 2023년부터 매년 100명 내외의 신입생을 선발하고, 이들이 전문역량을 꽃피울 수 있도록 학생 전원에게 특별장학금을 지급할 예정이다. 또한 산업계와의 긴밀한 협력을 통해 삼성전자 견학과 인턴십, 공동 워크숍을 지원해 현장에 밀착한 교육을 제공할 예정이다.

KAIST는 국내 반도체 분야 박사 인력의 25%, 박사 출신 중견 및 벤처기업 CEO의 20%를 배출하며 한국 반도체 산업 생태계가 성장하는 데 중대한 공헌을 했다. 본격적으로 열린 AI 반도체 경쟁 체제를 앞두고 KAIST가 다시 산업 생태계의 구심점 역할을 할지 귀추가 주목된다.

2022.08.04 조회수 18791

KAIST, 인공지능 반도체 생태계를 선도하다

인공지능 반도체(이하 AI 반도체)가 국가적인 전략기술로 두드러지면서 KAIST의 관련 성과도 주목받고 있다. 과학기술정보통신부는 지난해 2030년 세계 AI 반도체 시장 20% 점유를 목표로 인공지능 반도체 지원사업에 본격적으로 착수한 바 있다. 올해에는 산학연 논의를 거쳐 5년간 1조 200억 원을 투입하는 `인공지능 반도체 산업 성장 지원대책'으로 지원을 확대했다. 이에 따라 AI 반도체 전문가 양성을 위해 주요 대학들의 행보도 분주해졌다.

KAIST는 반도체와 인공지능 양대 핵심 분야에서 최상급의 교육, 연구 역량을 쌓아 왔다. 반도체 분야에서는 지난 17년 동안 메사추세츠 공과대학(이하 MIT), 스탠퍼드(Stanford)와 같은 세계적인 학교를 제치고 국제반도체회로학회(이하 ISSCC, International Solid State Circuit Conference)에서 대학 중 1위를 지켜 왔다는 점이 돋보인다. ISSCC는 1954년 설립된 반도체 집적회로 설계 분야 세계 최고 권위 학회다. 참가자 중 60% 이상이 삼성, 퀄컴, TSMC, 인텔을 비롯한 산업계 소속일만큼 산업적인 실용성을 중시해서 `반도체 설계 올림픽'이라는 별명도 있다.

KAIST는 ISSCC에서 채택 논문 수 기준 매년 전 세계 대학교 중 1~2위를 유지했다. 최근 17년간 평균 채택 논문 수를 살펴보면 압도적인 선두다. 해당 기간 채택된 KAIST의 논문은 평균 8.4편으로, 경쟁자인 MIT(4.6편)와 캘리포니아대학교 로스앤젤레스(UCLA)(3.6편)에 비해 두 배 가까운 성과다. 국내에서는 반도체 설계 분야 부동의 1위인 삼성에 이어 종합 2위 자리를 유지하고 있다. 그럴 뿐만 아니라 ISSCC와 쌍벽을 이루는 집적회로 분야 학술대회인 초고밀도집적회로학회에서도 KAIST는 2022년 전 세계 대학 중 1위를 기록했다.

KAIST의 연구진들이 반도체 산업 핵심 분야 전반에서 신기술을 발표해 연구의 질적인 수준도 높다. 전기및전자공학부 정명수 교수 연구팀은 고성능 저전력을 추구하는 현재 업계의 수요에 대응해 전력 공급 없이도 동작을 유지하는 컴퓨터를 개발했다. 소재 분야에서는 신소재공학과의 박병국 교수 연구팀이 기존의 메모리에 비해 동작 속도가 10배 이상 빠른 `스핀궤도토크 자성메모리' 소자를 개발해서 기존 `폰노이만 구조'의 한계를 극복하는 방안을 제시하기도 했다.

이처럼 현재 반도체 산업의 주요 과제에 솔루션을 제공하는 한편으로 미래의 새로운 반도체 분야를 선점하는 데 필요한 신기술 개발도 활발하다. 암호 및 비선형 연산 분야에서 차세대 컴퓨팅으로 주목받는 양자컴퓨팅 분야에서는 전기및전자공학부 김상현 교수 연구팀이 3차원 집적 기술을 세계 최초로 선보였다. 신경계의 원리를 활용해 인공지능 분야에서 발군의 성능을 보일 것으로 기대되는 뉴로모픽 컴퓨팅에서는 전기및전자공학부 최신현 교수 연구팀이 신경세포를 모사하는 차세대 멤리스터를 개발 중이다.

인공지능 분야에서도 비약적으로 성장했다. 인공지능 분야의 양대 세계 최고 권위 학회인 국제머신러닝학회(ICML)과 인공신경망학회(NeurIPS) 논문 수 기준으로 KAIST는 2020년 세계 6위, 아시아에서는 1위를 기록했다. KAIST의 순위는 2012년부터 꾸준히 우상향 그래프를 그려 8년만에 37위에서 6위로, 무려 31계단이나 도약했다. 2021년에는 인공지능 분야 톱 학회 11개에 발표된 한국 논문 중 약 40%에 달하는 129편이 KAIST에서 나왔다. KAIST의 이러한 활약에 힘입어 2021년 한국은 글로벌 인공지능 톱 학회 등재 논문 수 기준으로 미국, 중국, 영국, 캐나다, 독일에 이어 6위에 올랐다.

내용 면에서도 KAIST의 인공지능 연구는 최전선에 있다. 전기및전자공학부 유회준 교수 연구팀은 모바일기기에서 인공지능 실시간 학습을 구현해 에지 네트워크의 단점을 보완했다. 인공지능을 구현하려면 데이터 축적관 막대한 양의 연산이 필요한데, 이를 위해 고성능 서버가 방대한 연산을 담당하고 사용자 단말은 데이터 수집과 간단한 연산만 하는 `에지 네트워크'가 사용된다. 유 교수의 연구는 사용자 단말에 학습 능력을 부여함으로써 인공지능의 처리 속도와 성능을 크게 높일 수 있다.

지난 6월에는 전산학부 김민수 교수 연구팀이 초대규모 인공지능 모델 처리에 꼭 필요한 솔루션을 제시했다. 연구팀이 개발한 초대규모 기계학습 시스템은 현재 업계에서 주로 사용되는 구글의 텐서플로우(Tensorflow)나 IBM의 시스템DS 대비 최대 8.8배나 빠른 속도를 달성할 수 있을 것으로 기대된다.

KAIST는 반도체와 인공지능이 결합된 AI 반도체 분야에서도 주목할만한 성과를 내고 있다. 2020년 전기및전자공학부 유민수 교수 연구팀은 세계 최초로 추천시스템에 최적화된 AI 반도체를 개발하는 데 성공했다. 인공지능 추천시스템은 방대한 콘텐츠와 사용자 정보를 다룬다는 특성상 범용 인공지능 시스템으로 운영하면 병목현상으로 성능에 한계가 있다. 유민수 교수팀은 `프로세싱-인-메모리(이하 PIM, Processing-In-Memory)' 기술을 기반으로 기존 시스템 대비 최대 21배 빠른 속도를 낼 수 있는 반도체를 개발했다. PIM은 처리할 데이터를 임시로 저장하기만 하던 `램'에서 연산까지 수행해 효율을 높이는 기술이다. PIM 기술이 본격적으로 상용화되면 메모리 분야에서 강세인 한국 기업의 AI 반도체 시장 경쟁력이 비약적으로 높아질 것으로 기대된다.

KAIST는 그간의 성과에 안주하지 않고 인공지능 및 반도체, 그리고 AI 반도체 분야 초격차를 유지하고자 다각적인 노력을 기울이고 있다. 1990년 국내 최초로 인공지능연구센터를 설립한 데 이어 2019년에는 김재철AI대학원을 개설해 전문인력을 양성 중이다. 2020년에는 인공지능과 반도체 연구를 융합해 ITRC 인공지능반도체시스템 연구센터가 출범했으며, 2021년에는 인공지능을 다양한 분야에 접목하는 `AI+X' 연구를 활성화하고자 김재철AI대학원과 별도로 AI 연구원을 설립했다.

KAIST는 이러한 노력으로 축적된 내적 역량을 바탕으로 네이버 등 기업과 공동연구센터를 설립하는 한편, 화성시와 같은 지자체와 협력해 동시다발적인 전문인력 양성에 나섰다. 지난 2021년에는 삼성전자와 함께 반도체시스템공학과 설립 협약을 체결하고 새로운 반도체 전문인력 교육과정을 준비하고 있다. 새로 설립되는 반도체시스템공학과는 2023년부터 매년 100명 내외의 신입생을 선발하고, 이들이 전문역량을 꽃피울 수 있도록 학생 전원에게 특별장학금을 지급할 예정이다. 또한 산업계와의 긴밀한 협력을 통해 삼성전자 견학과 인턴십, 공동 워크숍을 지원해 현장에 밀착한 교육을 제공할 예정이다.

KAIST는 국내 반도체 분야 박사 인력의 25%, 박사 출신 중견 및 벤처기업 CEO의 20%를 배출하며 한국 반도체 산업 생태계가 성장하는 데 중대한 공헌을 했다. 본격적으로 열린 AI 반도체 경쟁 체제를 앞두고 KAIST가 다시 산업 생태계의 구심점 역할을 할지 귀추가 주목된다.

2022.08.04 조회수 18791